# Reconfigurable Integrated Circuits for Relmagine

Jonathan Frechette Advanced Imager Technology Group MIT Lincoln Laboratory 30 September 2016

Delivered to the U.S. Government with Unlimited Rights, as defined in DFARS Part 252.227-7013 or 7014 (Feb 2014). Notwithstanding any copyright notice, U.S. Government rights in this work are defined by DFARS 252.227-7013 or DFARS 252.227-7014 as detailed above. Use of this work other than as specifically authorized by the U.S. Government may violate any copyrights that exist in this work.

This material is based upon work supported by the Defense Advanced Research Projects Agency (DARPA) under Air Force Contract No. FA8721-05-C-0002 and/or FA8702-15-D-0001. Any opinions, findings and conclusions or recommendations expressed in this material are those of the author(s) and do not necessarily reflect the views of the United States Government.

© (2016) MASSACHUSETTS INSTITUTE OF TECHNOLOGY

Subject to FAR 52.227-11 – Patent Rights – Ownership by the Contractor (May 2014)

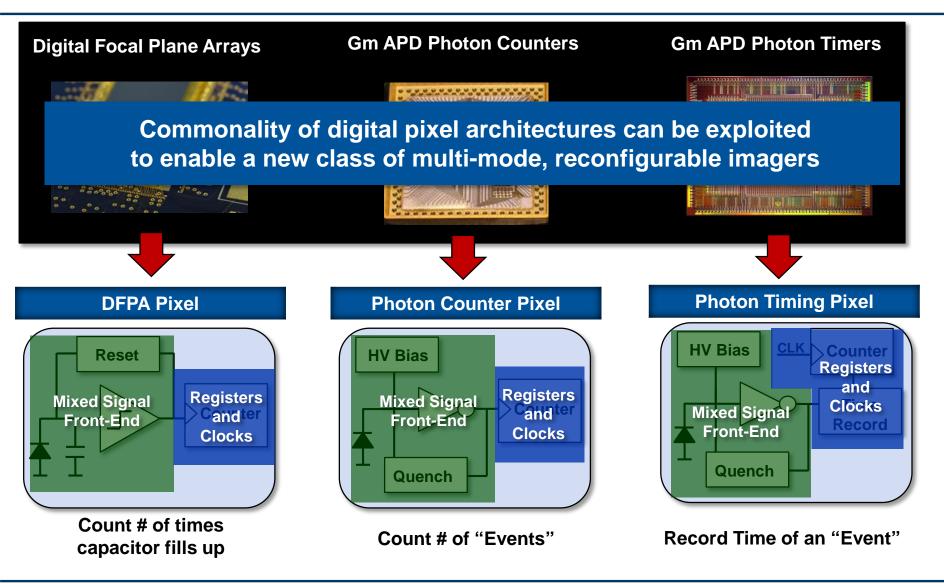

#### **Flexibility of Digital Pixel Architectures**

LINCOLN LABORATORY MASSACHUSETTS INSTITUTE OF TECHNOLOGY

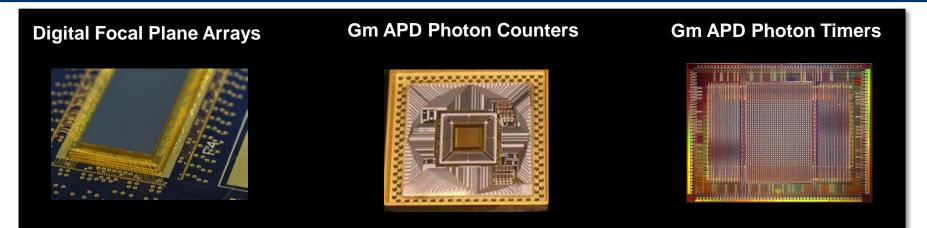

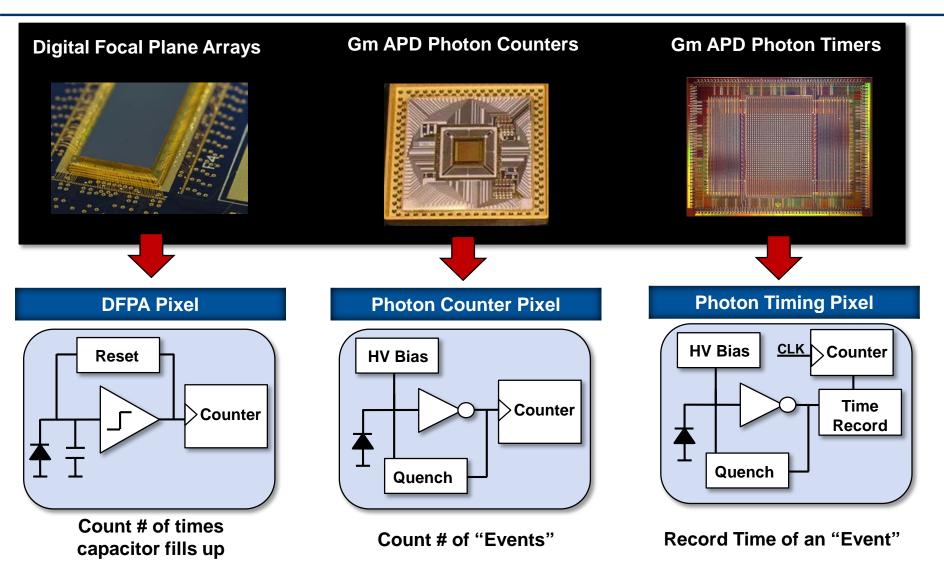

## **Digital ROICs Demonstrated by MITLL**

- Digital Readout Integrated Circuit (ROIC) characteristics

- ROICs are hybridized to an array of diodes (type of diode varies)

- In-pixel digitization

- All digital readout

- Standard foundry CMOS process

- Similar backend digital building blocks

## **Digital ROICs Demonstrated by MITLL**

- Digital Readout Integrated Circuit (ROIC) characteristics

- ROICs are hybridized to an array of diodes (type of diode varies)

- In-pixel digitization

- All digital readout

- Standard foundry CMOS process

- Similar backend digital building blocks

#### Key difference: How ROIC interfaces to diode and performs digitization

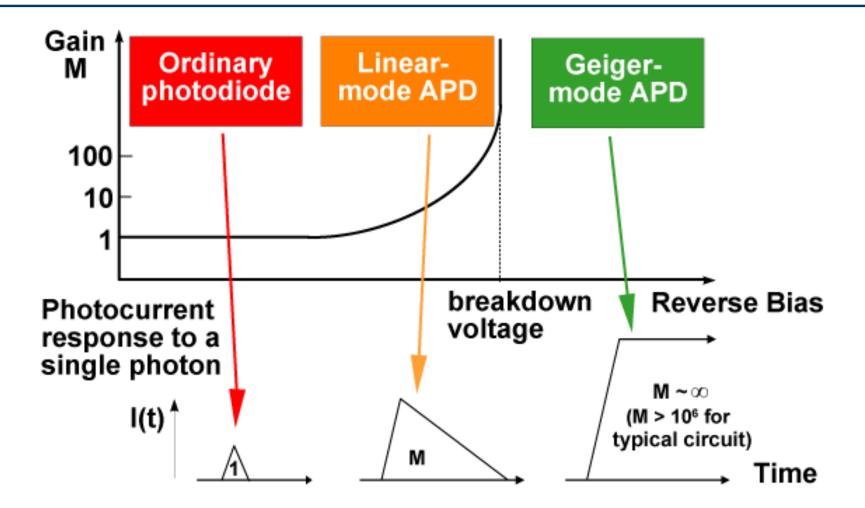

#### **Photodiode Modes of Operation**

Each type of photodiode requires a different type of ROIC front-end circuit

#### **In-pixel Digitization Methods**

### **In-pixel Digitization Methods**

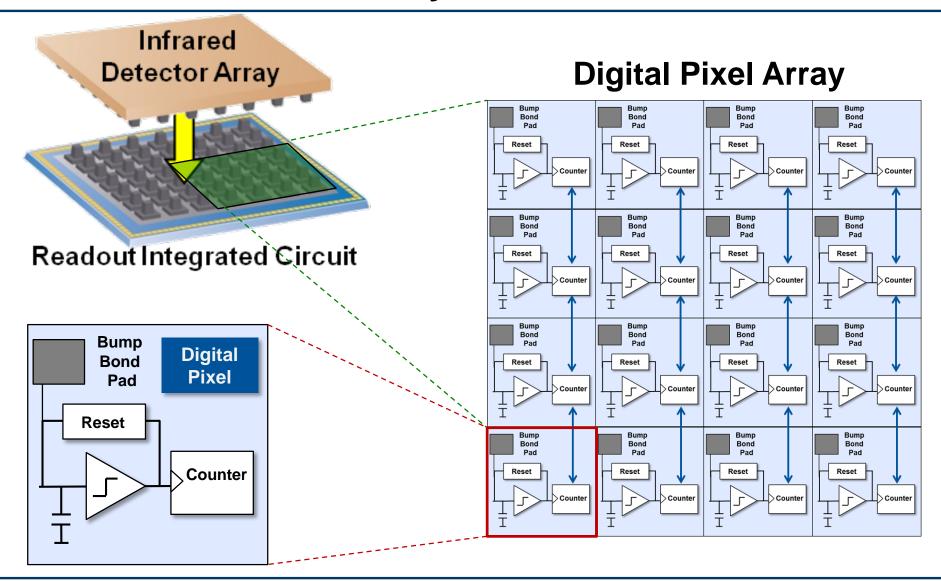

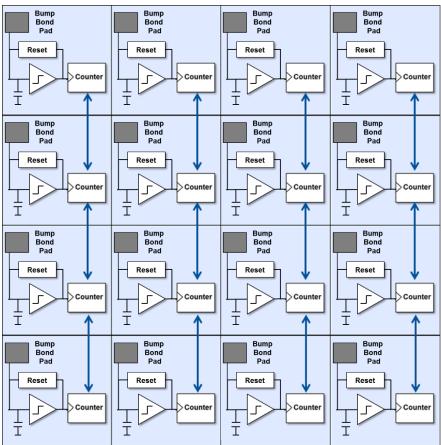

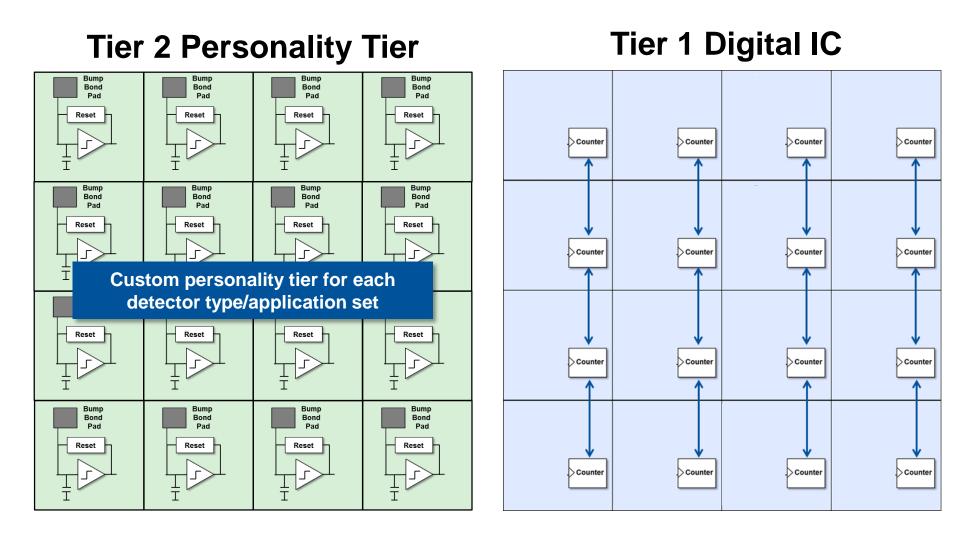

#### MITLL Digital Focal Plane Array Architecture

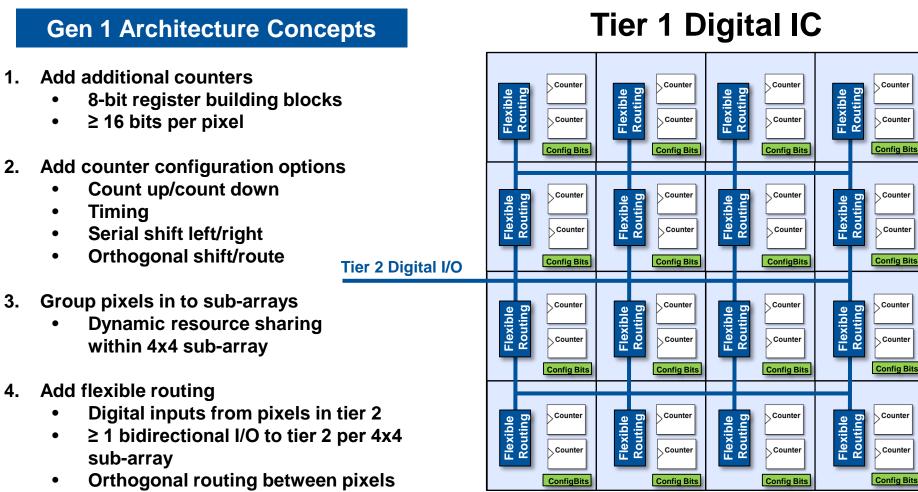

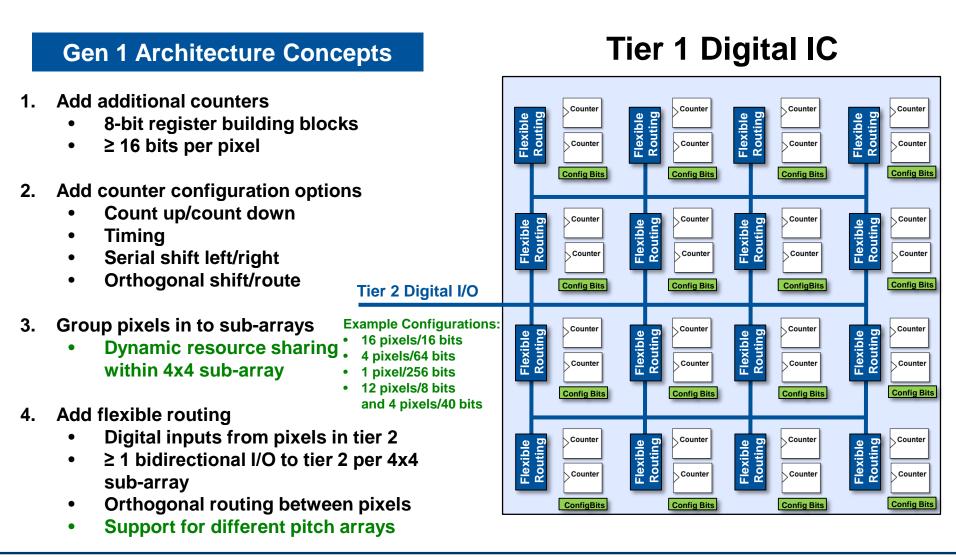

• Support for different pitch arrays

#### **Notional Device Specification**

#### **Gen 1 Notional Characteristics**

| Criterion                           | Gen 1                                                              |

|-------------------------------------|--------------------------------------------------------------------|

| Pixel Format                        | 640 x 512                                                          |

| Pixel Pitch                         | ≥ 10 µm                                                            |

| Operating Temperature               | 77 – 300 K                                                         |

| Minimum Tier 1-2 Interconnect Pitch | 5 µm                                                               |

| Digital Registers/Pixel             | ≥ 16 bits                                                          |

| Pixel Configuration                 | <ul> <li>8 bits per counter, independently configurable</li> </ul> |

|                                     | Count up/down or timing                                            |

|                                     | Serial shift left/right                                            |

|                                     | Orthogonal data shift/route                                        |

|                                     | Resource configuration per 4x4 pixel sub-array                     |

| Tier 2 Interface                    | ≥ 1 bidirectional I/Os per 4x4 pixel sub-array                     |

| Routing                             | 4 reconfigurable routing channels per 4x4 pixel sub-array          |

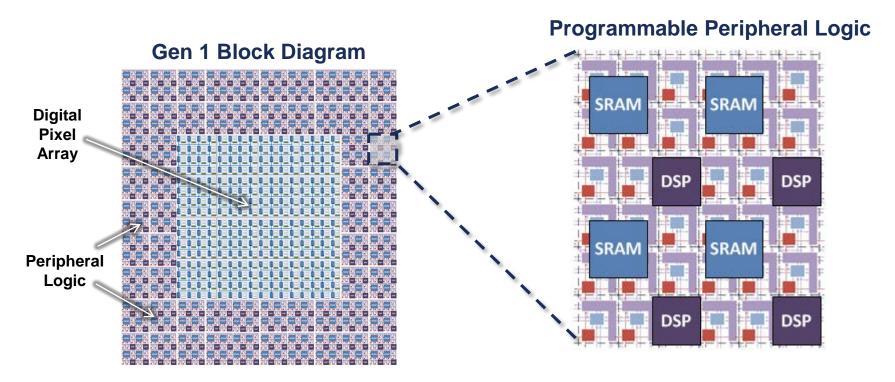

| Peripheral Logic                    | <ul> <li>≥ 10k look up tables</li> </ul>                           |

|                                     | • ≥ 64 DSP blocks                                                  |

|                                     | <ul> <li>≥ 1 MB memory</li> </ul>                                  |

#### **FPGA-like Resources and Programming**

- Pixel array will be surrounded by banks of reconfigurable logic resources

- Reconfigurable periphery and pixel array circuitry programmed through FPGA based synthesis and place and route tools

- Tools consist of open source FPGA CAD tools and government furnished software from MITLL as well as a library of Verilog models of Relmagine digital resources

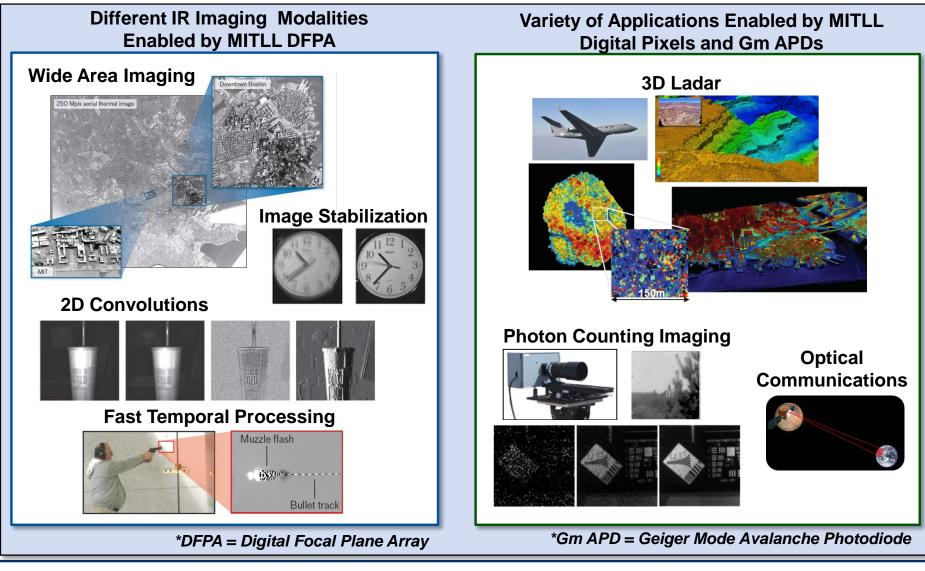

- MITLL leveraging extensive background in digital pixels to develop next generation reconfigurable integrated circuits for ReImagine

- Gen 1 IC will provide arrays of dynamically reconfigurable counter resources surrounded by peripheral programmable logic

- Gen 2 IC will expand and Gen-1 concepts and replace some of the counter resources in the pixel array with more complex digital blocks (e.g. memories, adders, multipliers, etc)

- Reconfigurable ICs will be programmed through a combination of open source FPGA CAD tools and government-furnished software from MITLL