# PHOTOVOLTAIC DC ARC FAULT DETECTOR TESTING AT SANDIA NATIONAL LABORATORIES

Jay Johnson<sup>1</sup>, Birger Pahl<sup>2</sup>, Charles Luebke<sup>2</sup>, Tom Pier<sup>2</sup>, Theodore Miller<sup>3</sup>, Jason Strauch<sup>1</sup>, Scott Kuszmaul<sup>1</sup>, and Ward Bower<sup>1</sup>

<sup>1</sup>Sandia National Laboratories, Albuquerque, NM, USA

<sup>2</sup>Eaton Corporation, Milwaukee, WI, USA

<sup>3</sup>Eaton Corporation, Pittsburgh, PA, USA

#### **ABSTRACT**

The 2011 National Electrical Code® (NEC®) added Article 690.11 that requires photovoltaic (PV) systems on or penetrating a building to include a listed DC arc fault protection device. To fill this new market, manufacturers are developing new Arc Fault Circuit Interrupters (AFCIs). Comprehensive and challenging testing has been conducted using a wide range of PV technologies, system topologies, loads and noise sources. The Distributed Energy Technologies Laboratory (DETL) at Sandia National Laboratories (SNL) has used multiple reconfigurable arrays with a variety of module technologies, inverters, and balance of system (BOS) components to characterize new Photovoltaic (PV) DC AFCIs and Arc Fault Detectors (AFDs). The device's detection capabilities, characteristics and nuisance tripping avoidance were the primary purpose of the testing. SNL and Eaton Corporation collaborated to test an Eaton AFD prototype and quantify arc noise for a wide range of PV array configurations and the system responses. The tests were conducted by generating controlled, series PV arc faults between PV modules. Arc fault detection studies were performed on systems using aged modules, positive- and negative-grounded arrays, DC/DC converters, 3-phase inverters, and on strings with branch connectors. The tests were conducted to determine if nuisance trips would occur in systems using electrically noisy inverters, with series arc faults on parallel strings, and in systems with inverters performing antiislanding and maximum power point tracking (MPPT) algorithms. The tests reported herein used the arc fault detection device to indicate when the trip signal was sent to the circuit interrupter. Results show significant noise is injected into the array from the inverter but AFCI functionality of the device was generally stable. The relative locations of the arc fault and detector had little influence on arc fault detection. Lastly, detection of certain frequency bands successfully differentiated normal operational noise from an arc fault signal.

## INTRODUCTION

Arc faults in photovoltaic systems have ignited a number of fires in residential, commercial, and utility installations [1-3]. Article 690.11 in the 2011 National Electrical Code

requires new photovoltaic (PV) systems on or penetrating a building to include a listed DC arc fault protection device [4]. To enter this new market, PV DC Arc Fault Circuit Interrupter (AFCI) designs must be compatible with a wide range of PV technologies, inverters, and other BOS components.

The Distributed Energy Technologies Laboratory (DETL), at Sandia National Laboratories, shown in Figure 1, has been used as a test bed to integrate novel technologies into renewable energy systems for decades. SNL has partnered with inverter, module, and—most recently—AFD and AFCI manufacturers. With the adoption of the 2011 NEC, SNL is testing new AFDs and AFCIs on PV systems. SNL facilities have reconfigurable PV arrays with PV modules from different manufacturers and a diverse portfolio of PV technologies, ages, and I-V characteristics, along with a range of connectors, DC disconnects, combiner boxes, line lengths, and inverters. The variety of PV array technologies and configurations makes the facility ideal for testing the robustness of AFDs and AFCIs.

Figure 1 A portion of the PV arrays at DETL.

PV DC AFCI devices consist of an intelligent Arc Fault Detector (AFD) and an Arc Fault Interrupting Device (i.e., circuit interrupter) that physically disconnects the DC PV circuit. Some of the suggested AFCIs are installed on individual strings and detect the presence of a specific AC frequency or frequencies that are emitted by the arcing event. Based on this detection methodology, Sandia and Eaton engineers identified a set of tests—in addition to the UL 1699B testing [6]—to investigate the potential for two of the major AFD failure modes: (1) the AFD falsely indicates an arc (nuisance trips) due to antenna effects,

crosstalk, or inverter noise or (2) the AFD fails to detect the arc fault because the frequency of the arcing signal was filtered, masked, or attenuated in the circuit components. Tests were conducted at DETL to measure baseline and arcing noise which the detector would encounter and be required to differentiate regardless of the arc fault location, module or inverter technology, and topology. This paper focuses on evaluating the types of noise that are encountered for various system configurations and conditions that can influence the ability of an AFD to detect arc faults. It will not report any proprietary pass/fail results or detection times of the AFD hardware under test.

#### ARC FAULT DETECTION CHALLENGES

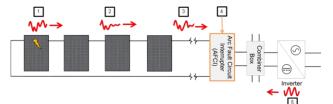

There are a number of challenges to remote arc fault detection. As shown in Fig. 2, the following behavior occurs during the arcing event:

- An arc fault initiates at some location in the string and generates 1/f ("pink") AC noise on top of the DC current. This signal—illustrated on the left side of Fig. 2—travels down the line through the system.

- As the signal passes through the PV modules and connectors, a variable attenuation occurs in the PV modules and connectors and changes the frequency amplitudes (profile) of the electrical noise as it propagates downstream.

- Antenna effects, crosstalk and other RF phenomena further modify the signal profile and characteristics.

- 4. The modified arcing signal reaches the arc fault detector in the AFCI. Depending on the PV cell technology, system topology, metrological conditions, and health of the modules, the signal reaching the AFD is likely different than the original arcing signal—possibly allowing an arcing condition to go undetected.

- Inverter noise is injected onto the PV string and inverter switching generates switching frequency and harmonics from 1kHz to >100 kHz [6].

Figure 2 Arc fault signal propagation and detection block diagram.

# **ARC FAULT DETECTION TESTS**

The list in Table 1 outlines the tests performed at Sandia National Laboratories to verify the AFD was capable of arc fault detection without nuisance trips. The baseline measurements established system noise levels. Arcing tests monitored arc fault detection and nuisance events by

inserting the arc fault generator (AFG) into different strings. With the diversity in PV systems, there was a need to test a number of special cases to satisfy different "what if" scenarios. They include thin-film PV, 3-phase inverters, DC/DC converters, and noise from different inverter designs.

#### **Baseline Measurements**

Prior to inserting the arc fault detector or circuit interrupter into the PV system, the AC noise of the array was measured in three locations, (a) at the far end of the PV string, (b) after the combiner box, and (c) at the inverter. Repositioning the data acquisition (DAQ) system identified if there were any RF effects or filtering due to line lengths, connectors, disconnects, and switchgear between the string and the inverter. The noise injected into the system from different inverters was measured and quantified to determine if this influenced arc fault detection time or nuisances trips. Last, the number of strings that were connected within the combiner box and with branched connections was varied to determine if system size and topology influenced the noise signatures.

## **Arcing Tests**

The *arcing tests* were designed to determine if the AFD functioned properly over a range of PV systems. First, the arc fault detector was placed on the PV array side of the combiner box, and then the arc fault was initiated at different locations within the array. The time required for detection was recorded for each location to determine if there was consistency. Other variations included:

- changing the inverter type

- changing the circuit layout with and without MC4 Yconnectors

- varying the AFD location

- testing on strings with aged modules with hot spots

There are many possible testing permutations. Experiments focused on encompassing worst case situations: noisy inverters, long line lengths, parallel strings connected with Y-connectors, and aged modules containing hot spots from many years of degradation. The goal was to verify these variables would not affect the AFD performance. Table 2 shows a subset of the components and configurations used for the characterization tests.

## **Special Cases**

AFDs and AFCIs must be robust enough to operate with various attenuation effects from the components while being exposed to external noise sources. The AFD under test was found to operate on a small—but representative—subset of PV technologies, BOS components and configurations. These special configurations included DC/DC converters, positive- and negative-grounded arrays, PV arrays with partial shading, single and 3-phase inverters, and thin-film PV systems. The susceptibility to nuisance tripping events due to

maximum power point tracking (MPPT) algorithms and anti-islanding fluctuations were also tested to verify they would not cause nuisance tripping. Also, there was concern that an arc fault in a parallel PV string would cause AFDs to trip due to crosstalk or other coupling. Tests were conducted to verify AFD selectivity.

## Table 1 List of Arc Fault Detector Tests.

## Baseline Measurements

- Voltage and current data capture of AC noise (baseline) at string and inverter on different topologies and module technologies.

- Measure the system noise at multiple locations where the arc fault detector may be located: on the string, at the combiner box, and at the inverter.

- b. Measure frequency signatures from selected inverters.

- Vary number of strings connected to the combiner box and inverter.

- Include branched systems with Yconnectors.

#### Arcing Tests

- Connect AFD to a single string at the combiner box.

- a. Produce arc faults at different locations in the PV array.

- Test arc fault detection on strings using a resistive load bank (does not include inverter switching frequency influence).

- Test strings with inverters, especially inverters that are 'noisy' or have irregular anti-islanding and/or maximum power point tracking methods.

- Test with strings using pre-identified, aged modules with known hot spots.

- Move the AFD inside DETL to determine if line lengths affect detection.

- Connect parallel strings at combiner box. Rerun previous tests.

- Special cases:

- a. Test using a 3-phase inverter.

- b. Test using systems with DC/DC converters.

- c. Test using a thin-film BIPV array.

- d. Crosstalk test Test the AFD operation when an arc fault is present in a parallel PV string.

- Test AFD using a negative- and positivegrounded array.

- f. Test on strings with Y-connectors.

- g. Reverse current during shading, where the inverter may maintain the DC bus voltage.

- Test to determine if nuisance trips occur on inverter start/shut-down and combiner box disconnect switching.

# **Data Acquisition System**

The string current was measured with a Tektronix TCP0150A; the string voltage and arcing voltage were

measured with Tektronix P5205 probes; and the AC current was measured with an Ion Physics CM-1-L current transformer. A Tektronix MSO4054 500-MHz mixed signal oscilloscope was used to visualize and record the data. The data was collected at a 10 MHz sample rate.

#### **RESULTS**

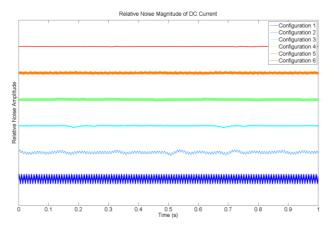

Testing was performed at the DETL facility at SNL to compare baseline noise and arcing noise on a range of systems. The most significant test results are presented in this paper. Baseline measurements were taken to quantify the noise in six different PV strings with different inverters, shown in Table 2. For the six configurations, the inverter places a unique noise signature on the line as shown in Figure 3.

Table 2 Baseline inverter noise testing configurations

| Configuration | Inverter                                      | Modules            | Strings | Modules/String |

|---------------|-----------------------------------------------|--------------------|---------|----------------|

| 1             | 4.8 kW                                        | 175 W c-Si         | 4       | 6              |

| 2             | 20 kW, 3-<br>phase                            | 90 W c-Si          | 1       | 21             |

| 3             | 20 kW, 3<br>phase                             | 80 W c-Si          | 1       | 22             |

| 4             | 3 kW                                          | 200 W c-Si         | 4       | 6              |

| 5             | 75 kW-3-<br>phase<br>with DC/DC<br>converters | 175 W c-Si         | 8       | 12             |

| 6             | 4 kW                                          | 540 W a-Si<br>BIPV | 3       | 2              |

Figure 3 DC string current on different PV arrays with different inverters.

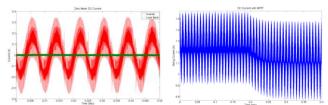

The noise signatures are composed of harmonics from 60 Hz AC current being reflected onto the DC side of the inverter, 120 Hz signals (shown in Figure 4) resulting from inverter switching in the single-phase H-bridge topology, and other inverter switching frequencies and broadband noise. Inverters also update the maximum power point tracking set-point at regular intervals (often 1 second), which induces noise at that point, shown in Figure 4. Further, inverters that have active anti-islanding algorithms regularly produce a prognostic spike on the AC side that may couple to the DC side of the inverter. Many noise

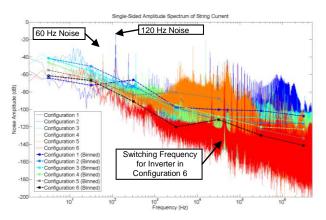

components are identifiable by taking the Discrete Fourier Transform (DFT) of the inverter noise signatures. The resulting spectral content for the configurations in Table 2 is shown in Figure 5.

Figure 4 120 Hz noise from the inverter compared to a resistive load bank noise (left) and the effect of MPPT on current (right).

Figure 5 Noise in six PV arrays with different inverters.

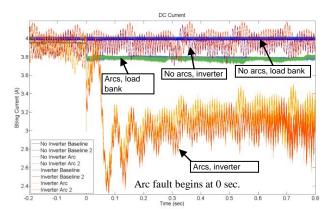

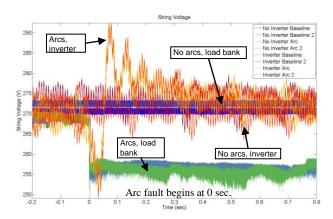

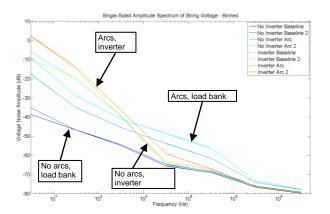

Depending on the PV system topology and components, arc faults in the PV system may result in different MPPT or anti-islanding operation. In single string tests, the operating dc current and voltage drops initially because the string impedance suddenly increased from the arc fault event. The inductive inverter components increase the dc-side time constant, so the response is significantly slower with the inverter. Baseline and arcing measurements on a string with an inverter and with a resistive load bank are shown in Figures 6 and 7.

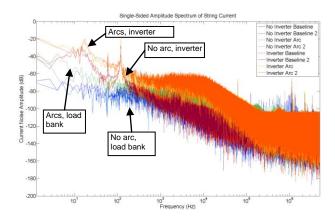

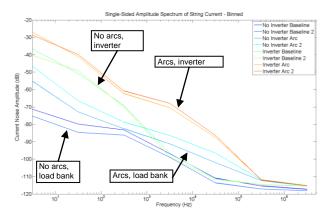

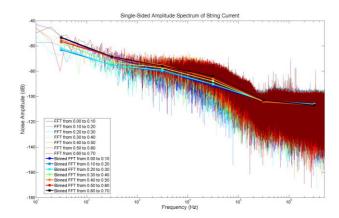

The inverter and arcing noise can be quantified by examining the DFT of the current from 0.05-0.8 s shown in Figure 6. Arcing frequencies are characterized by 1/f (pink) noise content [5], but, as shown in Figure 8, the noise is perturbed as the signal travels to the remotely located detector by filtering from the PV modules, antenna effects, or inverter noise. Shown in the binned result in Figure 9, this particular inverter puts more noise on the line for frequencies below 1 kHz, whereas the arc fault puts more uniform broadband noise on the line. Interestingly, the arcing noise is larger than the non-arcing noise between 1 Hz and 100 kHz regardless of the inverter noise. When performing the DFT on the voltage time series, as shown in Figure 10, the differentiation between arcing and non-faulted strings is more challenging using the decade binning technique.

Figure 6 DC string current for arcing and non-arcing conditions with an inverter and a resistive load bank. The arc initiated at 0 seconds and continued for more than 0.8 seconds.

Figure 7 DC string voltage for arcing and non-arcing conditions with an inverter and a resistive load bank.

Figure 8 Frequency content of the string current for arcing and non-arcing conditions with an inverter and a resistive load bank.

Figure 9 Current frequency content binned each decade for arcing and non-arcing conditions with an inverter and a resistive load bank.

Figure 10 Voltage frequency content binned each decade for arcing and non-arcing conditions with an inverter and a resistive load bank.

To create the ignition of an arc fault, the voltage exceeds the permittivity of free space, current begins flowing between the electrodes, and the gas ionizes to create a plasma. To determine if the initial period of the arc fault contained different frequency content than subsequent time periods, the arcing time domain was subdivided into 0.10 second blocks and the DFT of each time subsection was calculated. Shown in Figure 11, there was a slight variation in the frequency domain as the arcing time increased. Over most of the frequency domain, and especially between 10-100 kHz, the arcing noise amplitudes increased slightly over the duration of the arc fault. Since the arc was "drawn out" by separating opposing electrodes, the increase in noise may be caused by the increased arc gap.

It was believed that the location of the arc fault and the location of the detector could affect the measured frequency content. The arc fault generator was located before and after each module in a 6-module string and the arcing current was measured. While the amplitude of all

arcing frequencies was significantly larger than the baseline measurements, the location of the arc fault had little effect on the frequency content at the AFD. Likewise, when the detector was placed at the end of the string and at a location ~30 m farther along the conductor, there was no significant effect on the detected frequencies.

Figure 11 DFT data for 0.10 s arc fault subsections.

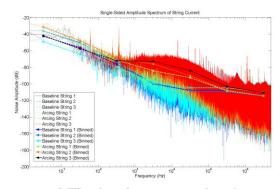

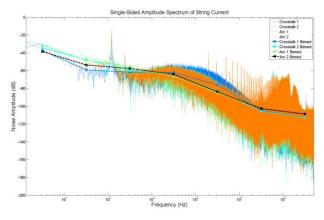

DETL has three subarrays connected to the same 3-phase inverter. The subarravs were composed of four 21 module strings of 90 W c-Si (crystalline silicon) modules, four 22 module strings with 80 W c-Si, and four 22 module 80 W p-Si (polycrystalline silicon) strings—each from different module manufacturers—and labeled subarray 1, 2, and 3. Baseline measurements and arcing measurements at the centers of the strings were taken. The binned frequency content (Figure 12) illustrates that certain frequency ranges are superior for arc fault detection. From 1-100 Hz and 100 kHz to 5 MHz there is little or no difference in the arcing noise content when compared to the baseline current frequencies. However, for the frequencies between 100 Hz-100 kHz, there is a clear separation between the arcing noise and the baseline for all strings. Thus, it is likely that the same arc detection algorithm could be used for these three module technologies.

Figure 12 DFT of string current for three string topologies with arcing and non-arcing conditions.

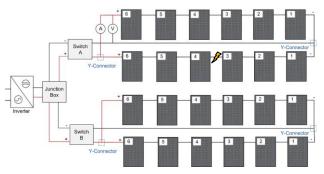

The 2011 *NEC* requires AFCIs to have enunciators to indicate that an arcing fault was detected. Ideally this will help identify the possible locations where the arc fault occurred so repairs can be completed quickly. However, if an arc fault on a parallel string causes the AFCI to trip, it will be more difficult to locate the fault location. To determine if the Eaton AFD was susceptible to false trips due to crosstalk, an arc fault was generated on a parallel string. The test setup is shown in Figure 13 and the frequency results for the crosstalk test and an arc fault on the monitored string are shown in Figure 14. The results show that the arcing frequency content and crosstalk noise on parallel strings is very similar. This indicates that more than just the frequency content of the string may be required to differentiate arcing noise from crosstalk noise.

Figure 13 Crosstalk test experimental configuration.

Figure 14 Crosstalk tests on Array.

# **CONCLUSIONS**

Article 690.11 of the 2011 National Electrical Code requires DC arc fault circuit protection on PV systems greater than 80 V mounted on or penetrating a building. Underwriters Laboratories, Inc has created Subject 1699B, which prescribes a series of tests to list the AFCI, including temperature, humidity, mechanical and electrical loads, radiation, and a representative set of arc fault tests [6]. The arc fault tests however do not cover the full range of field situations in which arc fault detectors will be required to perform. AFDs and AFCIs must function on a wide range of PV, BOS, and inverter technologies,

topologies, and array sizes, while also being resistant to nuisance trips from different forms of system noise. Additional AFD and AFCI tests using various PV technologies and system topologies were performed at the Distributed Energy Technologies Laboratory at Sandia National Laboratories.

Eaton Corporation collaborated with Sandia to run a battery of tests with a prototype AFCI. These tests focused on verifying accurate arc fault detection without false tripping. By also capturing current and voltage time series data of the baseline and arcing cases for the range of configurations, detection strategies and variabilities Inverters injected significant signal were measured. profiles on the PV strings. From the binned DFT results, it was shown that a range of noise frequencies are emitted above the baseline level during an arc fault, indicating these may be most appropriate for arc fault detection. Arc fault and detector locations did not appreciably affect the probability of detection for tests conducted, but some abnormalities were observed and will be further investigated. Difficulties distinguishing between arcing and crosstalk noise for some PV system configurations will also be an area for future study.

## **ACKNOWLEDGEMENT**

Sandia National Laboratories is a multi-program laboratory managed and operated by Sandia Corporation, a wholly owned subsidiary of Lockheed Martin Corporation, for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-AC04-94AL85000. This work was funded by the US Department of Energy Solar Energy Technologies Program.

## **REFERENCES**

- [1] Haeberlin, H. "Arc Detector as an External Accessory Device for PV Inverters for Remote Detection of Dangerous Arcs on the DC Side of PV Plants" European Photovoltaic Solar Energy Conference Valencia, Spain 2010.

- [2] Ji, L. PV Fire: Experience and Studies, International Photovoltaic Reliability Workshop II, 31 July, 2009.

- [3] Jackson, P. "Target Roof PV Fire of 4-5-09," City of Bakersfield, CA Development Services/Building Department Memorandum, 4-29-2009.

- [4] National Electrical Code, 2011 Edition, NFPA70, National Fire Protection Association, Batterymarch, MA.

- [5] Strobl, C. and Meckler, P. "Arc Faults in Photovoltaic Systems," 25<sup>th</sup> ICEC, 4 Oct, 2010.

- [6] Outline of Investigation for Photovoltaic (PV) DC Arc-Fault Circuit Protection, Subject 1699B, Underwriters Laboratories, Northbrook, IL, 29 April, 2011.