### In the Matter of

### Certain Semiconductor Integrated Circuits and Products Containing Same

Investigation No. 337-TA-665 Volume 2 of 2

**Publication 4268**

October 2011

**U.S. International Trade Commission**

Washington, DC 20436

### **U.S. International Trade Commission**

### COMMISSIONERS

Shara L. Aranoff, Chairman Daniel R. Pearson, Vice Chairman Deanna Tanner Okun Charlotte R. Lane Irving A. Williamson Dean A. Pinkert

Address all communications to Secretary to the Commission United States International Trade Commission Washington, DC 20436

## **U.S. International Trade Commission**

Washington, DC 20436 www.usitc.gov

# In the Matter of

# Certain Semiconductor Integrated Circuits and Products Containing Same

Investigation No. 337-TA-665 Volume 2 of 2

October 2011

introduced as an exhibit during trial, but read aloud by Qimonda's counsel during Dr. Shanfield's cross examination. (*See* CRB at 77-78 (citing Tr. at 1739:6-1740:21, 1743:17-22).) In this testimony, Dr. Glew allegedly stated that he believed {

1739:6-13.) This alleged "testimony" from Dr. Glew is not evidence, as the Glew deposition transcript was not admitted into evidence. Counsel's recitation during the cross examination of Dr. Shanfield does not suffice.

Assuming, *arguendo*, that the evidence showed { } this does not prove that the "connected to the substrate" limitation is met. As construed by me, this limitation requires a direct physical connection between the substrate and the contacts. Dr. Glew's testimony does not { } (Tr. at 1739:6-13.)

Qimonda has the burden to prove a domestic industry exists. After reviewing the expert testimony and other relevant evidence offered by the parties and admitted into the record, I find that Qimonda failed to introduce any evidence {

} Thus, I find that

} (Tr. at

Qimonda failed to demonstrate that { } meets the "connected to the substrate" limitation of claim 1.

#### V. INVALIDITY

#### A. Applicable Law

It is Respondents' burden to prove invalidity, and the burden of proof never shifts to the patentee to prove validity. *Scanner Techs. Corp. v. ICOS Vision Sys. Corp. N.V.*, 528 F.3d 1365, 1380 (Fed. Cir. 2008). "Under the patent statutes, a patent enjoys a presumption of validity, *see* 35 U.S.C. § 282, which can be overcome only through facts supported by clear and convincing

evidence[.]" SRAM Corp. v. AD-II Eng'g, Inc., 465 F.3d 1351, 1357 (Fed. Cir. 2006).

The clear and convincing evidence standard placed on the party asserting the invalidity defense requires a level of proof beyond the preponderance of the evidence. Although not susceptible to precise definition, "clear and convincing" evidence has been described as evidence which produces in the mind of the trier of fact "an abiding conviction that the truth of a factual contention is 'highly probable." *Price v. Symsek*, 988 F.2d 1187, 1191 (Fed. Cir. 1993) (citing *Buildex, Inc. v. Kason Indus., Inc.,* 849 F.2d 1461, 1463 (Fed.Cir.1988).)

"A patent is invalid for anticipation if a single prior art reference discloses each and every limitation of the claimed invention. Moreover, a prior art reference may anticipate without disclosing a feature of the claimed invention if that missing characteristic is necessarily present, or inherent, in the single anticipating reference." *Schering Corp. v. Geneva Pharm., Inc.*, 339 F.3d 1373, 1377 (Fed. Cir. 2003). "When no prior art other than that which was considered by the PTO examiner is relied on by the attacker, he has the added burden of overcoming the deference that is due to a qualified government agency presumed to have properly done its job[.]" *Am. Hoist & Derrick Co. v. Sowa & Sons, Inc.*, 725 F.2d 1350, 1359 (Fed. Cir. 1984). Therefore, the challenger's "burden is especially difficult when the prior art was before the PTO examiner during prosecution of the application." *Hewlett-Packard Co. v. Bausch & Lomb Inc.*, 909 F.2d 1464, 1467 (Fed.Cir.1990).

Section 103 of the Patent Act states:

A patent may not be obtained though the invention is not identically disclosed or described as set forth in section 102 of this title, if the differences between the subject matter sought to be patented and the prior art are such that the subject matter as a whole would have been obvious at the time the invention was made to a person having ordinary skill in the art to which said subject matter pertains. Patentability shall not be negatived by the manner in which the invention was made.

#### 35 U.S.C. § 103(a) (2008).

"Obviousness is a question of law based on underlying questions of fact." *Scanner Techs. Corp. v. ICOS Vision Sys. Corp. N.V.*, 528 F.3d 1365, 1379 (Fed. Cir. 2008). The underlying factual determinations include: "(1) the scope and content of the prior art, (2) the level of ordinary skill in the art, (3) the differences between the claimed invention and the prior art, and (4) objective indicia of non-obviousness." *Id.* (citing *Graham v. John Deere Co.*, 383 U.S. 1, 17 (1966)). These factual determinations are often referred to as the "*Graham* factors."

"When no prior art other than that which was considered by the PTO examiner is relied on by the attacker, he has the added burden of overcoming the deference that is due to a qualified government agency presumed to have properly done its job[.]" *Am. Hoist & Derrick Co.*, 725 F.2d at 1359. Therefore, the challenger's "burden is especially difficult when the prior art was before the PTO examiner during prosecution of the application." *Hewlett-Packard Co.*, 909 F.2d at 1467.

The critical inquiry in determining the differences between the claimed invention and the prior art is whether there is a reason to combine the prior art references. *KSR Int'l Co. v. Teleflex Inc.*, 550 U.S. 398, 417-418 (2007). In *KSR*, the Supreme Court rejected the Federal Circuit's rigid application of the teaching-suggestion-motivation test. The Court stated that "it can be important to identify a reason that would have prompted a person of ordinary skill in the relevant field to combine the elements in the way the claimed new invention does." *Id.* at 418. The Court described a more flexible analysis:

Often, it will be necessary for a court to look to interrelated teachings of multiple patents; the effects of demands known to the design community or present in the marketplace; and the background knowledge possessed by a person having ordinary skill in the art, all in order to determine whether there was an apparent reason to combine the known elements in the fashion claimed by the patent at issue...As our precedents make clear, however, the analysis need not seek out

precise teachings directed to the specific subject matter of the challenged claim, for a court can take account of the inferences and creative steps that a person of ordinary skill in the art would employ.

Id.

Since *KSR* was decided, the Federal Circuit has announced that, where a patent challenger contends that a patent is invalid for obviousness based on a combination of prior art references, "the burden falls on the patent challenger to show by clear and convincing evidence that a person of ordinary skill in the art would have had reason to attempt to make the composition or device, . . . and would have had a reasonable expectation of success in doing so." *PharmaStem Therapeutics, Inc. v. Viacell, Inc.*, 491 F.3d 1342, 1360 (Fed. Cir. 2007).

#### B. The '670 Patent

**Respondents' Position**: Respondents allege that the '670 patent is anticipated by a technical article published by one of the named inventors of the '670 patent, Dr. Herbert Kabza and others entitled "Shallow Doping Profiles for High-Speed Bipolar Transistors" in the September 1988 edition of Journal de Physique. (hereinafter "the Kabza article") (RIB at 63-64 (citing RX-702).) More specifically, Respondents allege that more than one year before the filing date of the U.S. application that led to the '670 patent, the Kabza article was published disclosing the "two-step-anneal process that appears in claim 1." Respondents assert that, despite that fact, Dr. Kabza withheld the article from the U.S. Patent & Trademark Office ("USPTO"); but while withholding the Kabza article, he was arguing to the USPTO that the references cited by the examiner did not show the claimed two-step-anneal process.<sup>44</sup> (*Id.* at 63-64, 68.)

Respondents aver that the Kabza article was published before the earliest priority date for the '670 patent, and is thus, prior art under 35 U.S.C. § 102(a). (RIB at 64.) Respondents argue

<sup>&</sup>lt;sup>44</sup> Respondents originally raised an inequitable conduct defense; but they have since abandoned that defense.

it is also prior art under § 102(b), because it was published more than one year before the earliest U.S. filing date for the application that led to the '670 patent. (Id.)

Respondents state that in general, the '670 patent is directed to a method for manufacturing polycrystalline silicon layers from amorphous silicon using a two-step anneal process. (RIB at 64 (citing RX-813C at Q. 39).) Respondents say that as set forth in claim 1, the first step of the two-step anneal takes place at an initial temperature below the crystallization temperature of amorphous silicon, and the second step takes place at a temperature that is above the crystallization temperature. (Id. (citing RX-813C at Q. 39; JX-7 at 6:45-66).) Respondents continue that by controlling heating in a reproducible manner, a polycrystalline silicon layer is formed having a defined particle size and texture. (Id. (citing RX-813C at Q. 39; JX-7 at 6:57-

66).)

Respondents recite that Claim 1 of the '670 Patent states:

1. A method for the manufacture of a polycrystalline silicon layer on a substrate, comprising the steps of:

[1] depositing an amorphous silicon layer on a substrate; and

[2] then controlling the phase transformation of the amorphous silicon into a polycrystalline layer by the steps of:

[3] heating said substrate with said amorphous silicon layer to an initial temperature that is lower than a crystalline temperature for the amorphous silicon,

[4] holding the substrate with said amorphous silicon layer at the initial temperature to achieve a thermal equilibrium of the substrate with the amorphous silicon layer at said initial temperature, and then, after reaching the thermal equilibrium,

[5] continuing the heating of said substrate with said amorphous silicon layer to raise the temperature at a controlled rate through a reproducible prescribed temperature profile from said initial temperature to a target temperature, said target temperature being higher than the crystallization temperature of said amorphous silicon so that said amorphous silicon

crystallizes and becomes a polycrystalline layer having a defined grain size and texture.

(RIB at 64-65 (citing JX-7 at 6:41-66 (bracketed element numbers added by Respondents).)

Respondents assert that the Kabza article expressly discloses steps [2]-[5] of claim 1, specifically "the two-step anneal that is recited in the claim." Regarding step [1], Respondents concede that the Kabza article does not disclose "depositing an amorphous silicon layer on a substrate" as that term would be understood by a person of ordinary skill in the art. (*Id.*) They say it does describe, however, preamorphizing the silicon layer by implantation of germanium (Ge) ions at 60 keV. (RIB at 64-65 (citing RX-702 at 2).)

Respondents say Qimonda has asserted that "preamorphizing by ion bombardment" comes within the scope of "depositing an amorphous silicon layer" for purposes of infringement. (RIB at 65 (citing CX-141C at Q. 45).) Although Respondents argue that Qimonda is incorrect, they argue that if the Court were to adopt Qimonda's construction, it would necessarily have to use that claim construction for purposes of invalidity. (*Id.* (citing *Amgen Inc. v. Hoechst Marion Roussel, Inc.*, 314 F.3d 1313, 1330 (Fed. Cir. 2003) ("It is axiomatic that claims are construed the same way for both invalidity and infringement.")).) Under Qimonda's construction, Respondents allege, the Kabza article would disclose step [1] of claim 1 of the '670 patent. (*Id.*)

Respondents argue that even if the Court does not adopt Qimonda's construction for "depositing an amorphous silicon layer," the Kabza article is still material because it discloses each and every other element of claim 1. (RIB at 65-66 (citing RX-813C at Q. 47, 57).) They quote:

To reduce the influence of the channelling effect, we preamorphized the bulk Si by Ge implantation at 60 keV prior to the B+ implant. To allow for direct comparison of the benefits of preamorphization, the B+ implantation was done at 10 keV as well. Of course perfect recrystallization of the amorphous layer is of

crucial importance. To remove the defects we employed two step anneal. A first step (450°C, 30 min) is performed to smoothen the amorphous/crystalline interface /2/ and to create the proper conditions for defect-free recrystallization during the final high temperature step. In order to minimize the broadening of the base profile this anneal was done by rapid thermal processing (RTP) at 1075° (10 sec).

#### (Id. (citing RX-702 at 2).)

Respondents state that "Step [2] of claim 1" requires "controlling the phase transformation of the amorphous silicon into a polycrystalline layer." (RIB at 66 (citing JX-7 at 6:45-46).) They continue that the Kabza article discloses "recrystallization of the amorphous layer" using a two-step anneal. (*Id.* (citing RX-702 at 2).) Specifically, Respondents aver, the Kabza article discloses heating the substrate with amorphous silicon layer to 450°C for 30 minutes and then heating to 1075°C. (*Id.*) Therefore, they argue, the Kabza article discloses this limitation. (*Id.* (citing RX-813C at Q. 51; RX-702 at 2).)

Respondents recite that "Step [3] of claim 1" requires "heating said substrate with said amorphous silicon layer to an initial temperature that is lower than a crystalline temperature for the amorphous silicon." (RIB at 66 (citing JX-7 at 6:48-51).) Respondents argue that the Kabza article discloses using a first anneal or heat step at 450°C, which is below the crystallization temperature for amorphous silicon, thus disclosing the limitation of element 3. (*Id.* (citing RX-813C at Q. 51).)

Respondents note that "Step [4] of claim 1" requires "holding the substrate with said amorphous silicon layer at the initial temperature to achieve a thermal equilibrium of the substrate with the amorphous silicon layer at said initial temperature." (RIB at 66 (citing JX-7 at 6:52-55).) Respondents argue that the Kabza article discloses this limitation. (*Id.* (citing RX-813C at Q. 53).) Respondents say the Kabza article explains that the first part of the two-step anneal is performed at 450°C for thirty minutes. (*Id.* (citing RX-702 at 2).) Respondents reason

that because the substrate and amorphous silicon would achieve thermal equilibrium in not more than a couple of minutes, the thirty-minute first heating step in the Kabza article is sufficient to achieve thermal equilibrium. (*Id.* (citing RX-813C at Q. 53).)

Respondents say that element 5 of claim 1 requires "continuing the heating of said substrate with said amorphous silicon layer to raise the temperature at a controlled rate through a reproducible prescribed temperature profile from said initial temperature to a target temperature, said target temperature being higher than the crystallization temperature of said amorphous silicon so that said amorphous silicon crystallizes and becomes a polycrystalline layer having a defined grain size and texture." (RIB at 66-67 (citing JX-7 at 6:57-66).) Respondents argue that the Kabza article also discloses this element as it explains that after an initial heating to 450°C, the substrate is then heated to a target temperature of 1075°C. (*Id.* (citing RX-813C at Q. 54; RX-702 at 2).) Respondents add that 1075°C is above the crystallization temperature of amorphous silicon. (*Id.* (citing RX-813C at Q. 54).) They continue that the second heating step is programmed into the processing sequence of a rapid thermal processing (RTP) system. (*Id.* (citing RX-813C at Q. 54; RX-702 at 2).) Respondents say that Dr. Kabza admitted that rapid thermal processing is a controlled process that follows a reproducible temperature profile. (*Id.* (citing Deposition Stipulation, Tab 8, at 119:6-21).)

Respondents argue that in his rebuttal witness statement, Qimonda's expert, Dr. Hammond reads process steps into Kabza that are not present and are not required. (RIB at 67.) Respondents say that Dr. Hammond asserts that after the first step of the two-step anneal in the Kabza article, the substrate would be removed from a furnace, allowed to cool, and then inserted into a rapid thermal processing tool. (*Id.* (citing CX-1045C at Q. 33).) Respondents allege that the Kabza article does not mention any of these additional steps. (*Id.* (citing Tr. at 1372:24-

1373:4).) Respondents aver that nothing in the Kabza article suggests performing the two steps of the two-step anneal in separate tools or to remove the substrate from the tool after the first step. (*Id.*) They argue that it would not be unreasonable to perform both the low-temperature 450°C first step and the 1075°C second step in the same rapid thermal processing tool. (*Id.* (citing Tr. at 1374:25-1375:4).)

Respondents state that Dr. Hammond admitted that it would be possible to use the same rapid thermal anneal tool for both steps in the Kabza paper. (RIB at 67-68 (citing Tr. at 1476:25-1477:9).) Respondents argue that the test for what a prior-art reference discloses is what it discloses to a person of ordinary skill in the art. (*Id.* (citing *Motorola, Inc. v. Interdigital Tech. Corp.*, 121 F.3d 1461, 1473 (Fed. Cir. 1997) ("Although this disclosure requirement presupposes the knowledge of one skilled in the art of the claimed invention, that presumed knowledge does not grant a license to read into the prior art reference teachings that are not there.")).) Respondents reiterate that the Kabza article does not address using separate tools for the first and second heating steps in the two-step anneal. (*Id.*) They argue that it is undisputed that a single rapid thermal processing tool would work for both steps of the Kabza article's two-step anneal. (*Id.* (citing Tr. at 1374:25-1375:4, 1476:25- 1477:9).) Respondents argue that it is not necessary to use different tools for the two steps in the Kabza article, then a person of ordinary skill would not use different tools. (*Id.*)

Respondents argue that the court should not read processing steps into the Kabza article that are not there. Respondents continue that if the court were to adopt Qimonda's position that "preamorphizing by ion bombardment" is within the scope of "depositing an amorphous silicon layer," then the Kabza article discloses every element of claim 1 of the '670 patent, and that claim is invalid as anticipated by the Kabza article. (RIB at 68.)

In their reply brief, Respondents say that the only argument Qimonda raises in defense of the patent, they say, is that the Kabza article does not disclose the following limitation: "continuing the heating of said substrate with said amorphous silicon layer to raise the temperature at a controlled rate through a reproducible prescribed temperature profile from said initial temperature to a target temperature, said target temperature being higher than the crystallization temperature of said amorphous silicon." (*Id.*)

Respondents argue that the Kabza article does disclose the foregoing limitation. Respondents say, Kabza explains that after an initial heating to 450°C, the substrate is then heated to a target temperature of 1075°C, which is clearly above the crystallization temperature of amorphous silicon. (RRB at 31.) Respondents allege the second heating step is programmed into the processing sequence of a rapid thermal processing (RTP) system. (*Id.* (citing RX-813C at Q. 54; RX-702 at 2).) Dr. Kabza admitted that rapid thermal processing is a controlled process that follows a reproducible temperature profile. (*Id.* (citing Deposition Stipulation, Tab 8 at 119: 6-21).)

**Qimonda's Position**: Qimonda argues that the prior art reference relied upon by Respondents does not anticipate or render obvious claim 1 of the '670 patent. Respondents argue that the Kabza reference and the deposition testimony of Dr. Kabza show that Respondents' argument is meritless. (CIB at 202-203.)

Qimonda asserts that the Kabza reference does not teach element 5 of claim 1 of the '670 patent, to wit: "after reaching the thermal equilibrium, continuing the heating of said substrate with said amorphous silicon layer to raise the temperature at a controlled rate through a reproducible prescribed temperature profile from said initial temperature to a target temperature, said target temperature being higher than the crystallization temperature of said amorphous

silicon so that said amorphous silicon crystallizes and becomes a polycrystalline layer having a defined grain size and texture." (CIB at 203 (citing JX-7 at claim 1; CX-1045C at Q. 33).)

Qimonda posits that the method claimed in claim 1 of the '670 Patent controls the phase transformation of the amorphous silicon into polycrystalline silicon through a predetermined, controlled continuous heating process that begins a first heating step and continues through a second heating step, with times and temperatures specified for the duration of the continuous heating process. (CIB at 203-204 (citing CX-141C at Q. 58).) Qimonda claims it is undisputed that claim 1 of the '670 patent requires a process that does not include any interruption between the first heating step and the second heating step. (*Id.*) Qimonda asserts that once heated to a thermal equilibrium, the substrate may not be allowed to cool before it is heated through a "reproducible prescribed temperature profile." (*Id.* (citing CX-1045C at Q. 33; Tr. at 1370:8-22).) Qimonda argues that this control is necessary to achieve consistent and reliable production of polycrystalline silicon having a defined grain size and texture. (*Id.* (citing CX-141C at Q. 58; JX-7 at 2:39-56, 3:22-46).)

Qimonda contrasts the foregoing with the Kabza reference, which they say discloses a two-step annealing process where the first step is performed, then the substrate is removed from the tool, sits for an indeterminate period of time, cools an indeterminate amount, and then is subjected to the second annealing step. (CIB at 204 (citing CX-1045C at Q. 33; CX-547C at 141-144).)

Qimonda continues that the first heating step in the Kabza reference is a 450°C, 30 minute anneal. (CIB at 204.) The second anneal is a 10 second, 1075°C rapid thermal processing ("RTP") anneal. (*Id.* (citing CX-1045C at Q. 33; CX-547C at 143; RX-702 at 2).)

Qimonda points to the testimony of Dr. Kabza during his deposition, to say that one of

ordinary skill in the art would recognize these two anneal steps were performed in different tools

- the first in a conventional furnace, and the second in a rapid thermal processing tool - and that

the wafer would be removed from the first tool and experience room temperature for an

indeterminate period of time before being subject to the second step:

Q. Do you agree that [the Kabza] reference discloses all of those steps?

\* \* \*

THE WITNESS: No, it is not corresponding to Patent.

\* \* \*

Q. I didn't ask you if it was corresponding to the Patent, sir, I asked you if it disclosed all of the steps that I had mentioned in the prior question?

\* \* \*

THE WITNESS: There are two thermal steps which do not stay in a direct relationship to each other.

Q. What do you mean?

A. When you read it then it states here that you first -- that the first step would be at 450°C will be heated within 30 minutes and for sure it happens not in an RTA and not in this rapid terminal processing unit. Which means that the wafer from this first step under 450°C will be taken out, it will be cooled to any kind of temperature, for example, air temperature, normal, and then our rapid thermal processing step comes.

Q. Show me the words that say that, sir?

\* \* \*

#### THE WITNESS:

"A first step (450°C at 30 minutes) is performed to smoothen the amorphous/crystalline interface and to create the proper conditions for defect-free recrystallization during the final high temperature step. In order to minimize the broadening of the base profile this anneal [so the high temperature step] is done by rapid thermal processing at 1075°C for 10 seconds."

That means that the wafer is from a furnace where, just a common furnace, where it has been heated up to 450°C within 30 minutes and then, for example, a week

later this wafer comes to rapid thermal processing unit to perform this second step.

Q. Which words of this paragraph say that it is taken out of the machine used for the first step before the rapid thermal processing step is performed?

\* \* \*

THE WITNESS: It is implicitly known for each who knows, who has knowledge in the field because nobody could do this 30 minute step in a rapid thermal processing equipment because it is too expensive. And here it is a clear difference to claim in Patent '670. Besides there is a total different application.

(CIB at 204-205 (citing CX-547C at 142:12-144:22).)

Qimonda states that Dr. Kabza testified that, while the Kabza paper did not explicitly

state that the wafer was removed from the tool used to perform the first step, one of ordinary

skill in the art would recognize that the first step would not be performed in an expensive,

specialized rapid thermal processing machine, when a cheaper, common furnace could be used to

perform that process:

Q. But you will agree with me that the article in Exhibit 5 does not explicitly say that the wafer is removed from the furnace after the first temperature step, correct?

\* \* \*

THE WITNESS: It doesn't state in explicit words how the transfer between the step of 450°C and 1075° takes place.

Q. So the paper does not explicitly state that it is done in separate chambers, does it?

\* \* \*

THE WITNESS: Everybody who has certain knowledge in the field will understand that because they will know that this 30 minutes in rapid thermal processing is not possible, not -- it is senseless.

(CIB at 205-206 (citing CX-547C at 152:12-153:4).)

Qimonda also points to the testimony of Dr. Hammond who testified:

Kabza, it describes a first step that takes place at 450°C for 30 minutes. One of ordinary skill in the art would recognize that a rapid thermal processing and/or

rapid thermal annealing tool was not used to complete this 30 minute step. Instead, a conventional furnace would have been used. On the same page, the Kabza reference describes the second, high-temperature step as a rapid thermal processing step. Therefore, one of ordinary skill in the art would recognize that the substrate would be removed into the air and have undergone cooling between the two steps.

#### (CIB at 206 (citing CX1045C at Q. 33).)

Qimonda argues that the method in use before the invention of the '670 patent used either a one-step or a two-step process to crystallize amorphous silicon. (CIB at 207-208.) For a onestep process, a furnace would be set at a specific temperature and then the wafers would be inserted into the furnace for a specified time period and removed. (*Id.*) For a two-step process, the general approach was to heat the wafer at one temperature for one period of time, remove the wafer from the tool, then at some future point, to heat the wafer at another temperature for another period of time. (*Id.*) Qimonda continues this removal of the substrate would allow the substrate to cool between the first and second heating steps. Qimonda asserts that the variable cooling associated with the removal of the wafer would affect grain size and texture of the resultant polycrystalline silicon. (*Id.* (citing CX-141C at Q. 21).) Qimonda argues that this flaw pervaded the alleged prior art, as it did the practice of those of skill in the art at the time that the application for the '670 patent was filed. (*Id.*) Qimonda asserts that no combination of references teaches the limitation of element 5 of the '670 patent, so the Kabza reference cannot render the '670 patent obvious. (*Id.* (citing CX-1045C at Q. 31-35).)

**Commission Investigative Staff's Position**: The Staff notes that Dr. Bruce Smith, Respondents' expert, testified that the Kabza article anticipates or would have rendered obvious all of the asserted claims of the '670 patent using Qimonda's apparent construction of the term "depositing" as set forth in claim 1 of the '670 patent. (SIB at 41 (citing RX-813C at Q. 47).) Staff asserts that Dr. Smith admitted that Kabza is not an anticipatory reference unless

Qimonda's claim construction for the term "depositing" a definition that includes ion implantation, is adopted. (*Id.* (citing RX-813C at Q. 57; Tr. at 1407).) Staff submits that under a proper claim construction, the asserted claims of the '670 patent would not be anticipated or obvious in light of Kabza. (*Id.*)

Staff restates its disagreement with Qimonda's construction that the term "depositing" as used in claim 1 of the '670 patent includes preamorphization by ion bombardment. Therefore, Staff does not believe that Kabza renders any of the asserted claims inval*id*. (SIB at 42.)

Staff opines that the evidence does not clearly and convincingly show that Kabza discloses, among other things, a continuous heating process as required by claim 1 regardless of the adopted construction of the term "depositing an amorphous silicon layer." (SIB at 42.) Staff avers that Dr. Hammond opined that Kabza discloses a "two-step annealing process where the first step is performed, then the substrate is removed from the tool, sits for an indeterminate period of time, cools an indeterminate amount, and then is subjected to the second annealing step." (*Id.* (citing CX -1045C at Q. 33).) Staff asserts that Dr. Hammond also opined that this two-step anneal process was the traditional and most cost effective method used in the industry. (*Id.* (citing Tr. at 1476).) Staff says that Dr. Hammond also pointed out that Kabza "does not specify the time or the temperature between the two [annealing] steps …" further undermining a conclusion that Kabza discloses a continuous heating process. (*Id.* (citing CX-1045C at Q. 33).) Staff's view is that Dr. Smith never effectively rebutted Dr. Hammond's opinion in this regard, let alone to the heightened level required to invalidate the claim. (*Id.*)

**Discussion and Conclusion**: Based upon the evidence before me, I find that Respondents have failed to meet their burden to show by clear and convincing evidence that the

Kabza article<sup>45</sup> anticipates claim 1 of the '670 patent.

First, to the extent that the Respondents focus on the construction of "depositing an amorphous silicon layer on a substrate" proposed by Qimonda, their argument is rendered moot by the fact that Qimonda's construction was *not* adopted by me in this matter.<sup>46</sup> I note, too, regarding element 1 of claim 1, the Kabza article does not disclose "depositing an amorphous silicon layer on a substrate" as that term would be understood by a person of ordinary skill in the art. Hence, using the construction that has been applied in this case, the Kabza article clearly does not anticipate claim 1 of the '670 patent.

Second, assuming arguendo that one were to apply the Kabza article to the elements of

claim 1 of the '670 patent using Qimonda's definition, the record lacks clear and convincing

evidence that the Kabza article would then anticipate all of the elements of claim 1.

Respondents quoted the relevant language of the Kabza article:

To reduce the influence of the channelling effect, we preamorphized the bulk Si by Ge implantation at 60 keV prior to the B+ implant. To allow for direct comparison of the benefits of preamorphization, the B+ implantation was done at 10 keV as well. Of course perfect recrystallization of the amorphous layer is of crucial importance. To remove the defects we employed two step anneal. A first step (450°C, 30 min) is performed to smoothen the amorphous/crystalline interface /2/ and to create the proper conditions for defect-free recrystallization during the final high temperature step. In order to minimize the broadening of the base profile this anneal was done by rapid thermal processing (RTP) at 1075° (10 sec).

(RX-702 at 2.)

I have already found the clear and unambiguous language of asserted claim 1 provides for the deposit of a layer of silicon that is in amorphous form and then sets forth the step-by-step sequential process of transforming that amorphous silicon into polycrystalline form.

<sup>&</sup>lt;sup>45</sup> The Kabza article was published in September 1988.

<sup>&</sup>lt;sup>46</sup> For a detailed discussion of the construction of the term "depositing an amorphous silicon layer on a substrate," see Section III.B.3 of this decision.

In claim 1, the beginning point is "depositing an amorphous silicon layer on a substrate."

Immediately following that language, claim 1 continues, "and" followed by element 2, which

states, "then controlling the phase transformation of the amorphous silicon into a

*polycrystalline layer by the steps of*:" Claim 1 then lists, in elements 3-5, a step-by-step process for achieving that transformation. (JX-7 at 6:43-47; 6:48-66) (emphasis added.) Element 5 of claim 1 requires "continuing the heating of said substrate with said amorphous silicon layer to raise the temperature *at a controlled rate through a reproducible prescribed temperature profile from said initial temperature to a target temperature* that is higher than the crystallization temperature of said amorphous silicon." (*Id.* at 6:57-63) (emphasis added.)

An example of a reproducible prescribed temperature profile is illustrated in the '670 patent specification, which describes for example:

... then the furnace is changed from the initial temperature to a target temperature. The target temperature lies above the crystallization temperature of the silicon layer, for example at 700° C. The temperature change ensues corresponding to a predetermined temperature profile, for example having a change rate of less than or equal to 10° C. per minute.

(JX-7 at 5:41-47.)

The process described in the Kabza article does not provide clear and convincing evidence that it calls for a reproducible prescribed temperature profile from the initial temperature to a target temperature. It merely provides a first step of heating and holding the temperature at 450° C for 30 minutes, and then to use rapid thermal processing (RTP) to achieve 1075° C and to hold that temperature for 10 seconds. (RX-702 at 2.) Although Respondents say that Dr. Kabza admitted that rapid thermal processing is a controlled process that follows a reproducible temperature profile, his testimony actually was that RTP uses a prescribed temperature profile only "when the process is running in a control manner and the conditions are

okay." (Deposition Stipulation, Tab 8, at 119:6-21.) I note that the relevant language of the Kabza article, quoted *supra*, does not stipulate that the RTP is to be done "in a controlled manner."

The process described in the Kabza article calls for heating the silicon to a temperature of 450° C for 30 minutes. It does not specify the tool to be used in this step. The second step of the process, however, specifies use of an RTP to heat the silicon to 1075° C for 10 seconds. What is clear from this language is that the authors, when they so desired, were fully cognizant and capable of specifying the RTP tool for use in heating the silicon. The fact that they did not specify RTP for the initial phase leads me to conclude that a separate, unspecified, tool for that initial heating was considered appropriate.

My impression is supported by the testimony of Dr. Kabza, who said:

Q. But you will agree with me that the article in Exhibit 5 does not explicitly say that the wafer is removed from the furnace after the first temperature step, correct?

\* \* \*

THE WITNESS: It doesn't state in explicit words how the transfer between the step of 450°C and 1075° takes place.

Q. So the paper does not explicitly state that it is done in separate chambers, does it?

\* \* \*

THE WITNESS: Everybody who has certain knowledge in the field will understand that because they will know that this 30 minutes in rapid thermal processing is not possible, not -- it is senseless.

(CX-547C at 152:12-153:4.)

Dr. Hammond also testified on this point in his rebuttal testimony, saying in relevant part:

One of ordinary skill in the art would recognize that the Kabza reference, like Sasaki, described a two-step annealing process where the first step is performed, then the substrate is removed from the tool, sits for an indeterminate period of time, cools an indeterminate amount, and then is subjected to the second

annealing step. As illustrated by slide 0048A of Exhibit CDX-40, on page 2 of Kabza, it describes a first step that takes place at 450°C for 30 minutes. One of ordinary skill in the art would recognize that a rapid thermal processing and/or rapid thermal annealing tool was not used to complete this 30 minute step. Instead, a conventional furnace would have been used. On the same page, the Kabza reference describes the second, high-temperature step as a rapid thermal processing step. Therefore, one of ordinary skill in the art would recognize that the substrate would be removed into the air and have undergone cooling between the two steps ... The Kabza reference does not specify the time or temperature between the two steps.

#### (CX1045C at Q. 33.)

Dr. Hammond also opined at trial that this two-step anneal process was the traditional method used in the industry. (Tr. at 1476:11-14.) He testified that using a rapid thermal procession or rapid thermal annealing tool to perform the initial step of heating and holding the silicon at 450° C. for 30 minutes as described in the Kabza article could not be done. He said "the temperature is quite low for any RTA apparatus" and that the time of 30 minutes was "far beyond anything one of ordinary skill would consider to use. RTA is used for tens of seconds, perhaps a hundred seconds' worth of time. Furnaces have historically been used for process times of tens of minutes to tens of hours." (*Id.* at 1477:1-9.)

The evidence supports a finding that the process contemplated by the Kabza article is a two-step process in which the silicon is heated and held at 450° C. for 30 minutes, then it is removed from the tool for an indeterminate period of time and cools an indeterminate amount, after which it is subjected to RTP to a temperature of 1075° C for a period of 10 seconds. Hence, the Kabza article does not disclose the requirement of element 5 for "*continuing* the heating of said substrate with said amorphous silicon layer to raise the temperature *at a controlled rate through a reproducible prescribed temperature profile from said initial temperature to a target temperature* that is higher than the crystallization temperature of said amorphous silicon."

Based on all of the foregoing, and assuming *arguendo* that Qimonda's definition of "depositing an amorphous silicon layer on a substrate" were correct, I find that the record lacks clear and convincing evidence that the Kabza article discloses element 5 of claim 1 of the '670 patent.

#### C. The '434 Patent

#### 1. Maloney

**Respondents' Position**: Respondents argue that the paper titled "Designing MOS Inputs and Outputs to Avoid Oxide Failure in the Charged Device Model," by Timothy J. Maloney, Electrical Overstress/Electrostatic Discharge Symposium Proceedings (Sept. 27-29, 1988), at 220-227 ("Maloney") anticipates claims 1-5 and 7 of the '434 patent. (RIB at 103-104.)

Regarding claim 1, Respondents assert that Maloney discloses every limitation. (RIB at 104 (citing RX0774C; RX-205).) They claim that one of ordinary skill in the art would know that Maloney discloses a semiconductor component. (*Id.*) Respondents state that Figure 2c of Maloney discloses a semiconductor body that has a terminal pad, a semiconductor function element, and an electrically conductive connecting line connecting the terminal to the semiconductor function element. (*Id.*) Respondents offer an annotated version of Figure 2c of Maloney with the claim elements identified. (*Id.* at 105 (citing RX-774C at Q. 145; RDX-124; RX-205 at 221-222, Fig. 2c).)

Respondents claim that Figure 2c also discloses the claimed protective element, with the protective element connected between the terminal pad and the semiconductor function element. (RIB at 105 (citing RX-774C at Q. 145, RX-205 at 221-222, Fig. 2c, RDX-124).) Respondents point to two supply lines as required by claim 1, and they assert that the supply lines are connected to a common VSS potential. (*Id.* (citing RX-744C at Q. 142; RX-205).)

Respondents state that Qimonda's only argument that Maloney does not anticipate claim 1 is that there is only one supply line disclosed, and that Respondents claim that the two supply lines are actually different portions of the same line. (RIB at 106 (citing CX-1044C, Tr. at 1529:24-1551:24; RX-774C).) Respondents rebut this assertion by pointing to a portion of Maloney that describes separate ground paths. (*Id.* (citing RX-205 at 222; RX-774C at Q. 145; RDX-124).)

Finally, Respondents claim that Figure 2c of Maloney discloses a clamp element connected to the first supply line. (RIB at 106 (citing RX-774C at Q. 145; RX-205 at 221-222, Fig. 2c; RDX-124).) Thus, Respondents claim that Maloney anticipates, because it discloses every limitation in claim 1.

Regarding claim 2, Respondents assert that Maloney also discloses that the first supply line may be connected to the second supply line by a bond connection. (RIB at 107 (citing RX-205 at 222; RX-774C at Q. 145).) Moreover, according to Respondents, one of ordinary skill in the art would have appreciated that each "Bus R" in Figure 2c represents various parasitics of ground bus paths, which typically included wire resistances, bond connections, lead frame resistances, inductances, and the like. (*Id.* (citing RX-774C at Q. 142; RX-205).)

Regarding claim 3, Respondents argue that Figure 2c of Maloney discloses that: (1) the semiconductor function element has a terminal; (2) the bond connection has a terminal; (3) the first supply line has a portion disposed between the terminal of the semiconductor function element and the terminal of the bond connection; and (4) the clamp element is connected to the portion of the first supply line. (RIB at 107-108 (citing RX-774C at Q. 149; RX-205 at 221-222, Fig. 2c; RDX-124).)

Respondents argue that claim 4 is invalid because the term "immediate spatial vicinity" is

indefinite. (RIB at 109.) If the term is not found indefinite, Respondents argue that Maloney anticipates claim 4 because Maloney calls for the clamp element to be placed at the input buffer. (*Id.* (citing RX-205 at 222; RX-774C at Q. 151; RDX-124).) Respondents state that placing the clamp element at the input buffer clearly constitutes the "immediate spatial vicinity." (*Id.* (citing RX-774C at Q. 151).)

Regarding claim 5, Respondents assert that Maloney is anticipatory. Respondents state that Figure 2 of Maloney "discloses the clamp element implemented as a MOS transistor having its main current path connected to the connecting line and to the first supply line, with its gate terminal connected to the first supply line, which is generally referred to as a ggNMOS." (RIB at 109-110 (citing RX-774C at Q. 152; RX-205 at 221-222, Fig. 2c; RDX-124).)

Respondents argue that Maloney anticipates claim 7. Respondents claim that Figure 2c of Maloney discloses that: (1) the connecting line includes a given resistance (i.e., the inherent resistance of the portion flagged by the dashed brown oval); (2) the protective element includes a resistor connected between the terminal pad and the semiconductor function element; and (3) the resistor has a resistance that has been adjusted for setting a sum of resistance of the resistor and the given resistance to a predetermined value of at least "typically a few hundred ohms." (RIB at 110 (citing RX-774C at Q. 155; RX-205 at 221-222, Fig. 2c; RDX-124).)

**Qimonda's Position**: Qimonda argues that Maloney fails to anticipate claim 1 because it teaches a single supply line connected to ground, instead of first and second supply lines. (CIB at 101 (citing CX-1044C at Q. 30, 31; CDX-38 at QAG-665-ITC-0233821; Tr. at 1543:9-1544:10, 1546:4-1548:7; RX-205).) Qimonda further claims that Maloney fails to teach that the supply lines are electrically conductively connected. (*Id.* at 102 (citing RX-205 at LSI-337-665-0061847; CX-1044C at Q. 30, 31; CDX-38 at QAG-665-ITC-0233821; Tr. at 1543:9-1544:10,

1546:4-1548:7).)

Qimonda states that a person with ordinary skill would have interpreted the two circuit elements labeled "BUS R" in Maloney as two internal-circuitry buses, which are connected onchip rather than being spatially separated to decouple voltage fluctuations. (CIB at 103 (citing CX-1044C at Q. 30, 31; CDX-38 at QAG-665-ITC-0233821; Tr. at 1543:9-1544:10, 1546:4-1548:7).) Qimonda argues that it was common at the time the '434 patent was filed to connect multiple bond wires to a single bus or on-chip track. (Id. at 104 (citing CX-1044C at Q. 30, 31; CDX-38 at QAG-665-ITC-0233821; Tr. at 1543:9-1544:10, 1546:4-1548:7).) Qimonda claims that a person of ordinary skill in the art at the time of the '434 patent would have interpreted Maloney to refer to this configuration. (Id. (citing CX-1044C at Q. 30, 31; CDX-38 at QAG-665-ITC-0233821; Tr. at 1543:9-1544:10, 1546:4-1548:7).) Qimonda asserts that since ground bus (VSS) resistance is especially important for every on-chip track, the most straightforward interpretation of Fig. 2b and Fig. 2c to a person of ordinary skill in the art would have been that the two "BUS R" labels represented resistance between circuit elements on a single wiring bus or on-chip track. (Id. (citing CX-1044C at Q. 30, 31; CDX-38 at QAG-665-ITC-0233821; Tr. at 1543:9-1544:10, 1546:4-1548:7).) Therefore, according to Qimonda, Maloney would not have taught a person of ordinary skill in the art to spatially separate the buses from each other on the chip, so that voltage fluctuations are decoupled.

In addressing the dependent claims, Qimonda argues that because Maloney does not anticipate claim 1, it does not anticipate any of the dependent claims. (CIB at 104-106.) Regarding claim 2, Qimonda also argues that Maloney also fails to describe "at least one bond connection connecting said first and second supply lines to one another." (*Id.* at 104-105.) Qimonda asserts that a person of ordinary skill in the art would have interpreted the elements

labeled "BUS R" in Figure 2c as two internal buses connected on-chip. (*Id.* at 105 (citing CX-1044C at Q. 32).)

Regarding claim 3, Qimonda argues that Maloney does not describe that "said semiconductor function element has a terminal, said at least one bond connection has a terminal, said first supply line has a portion disposed between said terminal of said semiconductor function element and said terminal of said at least one bond connection, and said clamp element is connected to said portion of said first supply line." Qimonda states that based on the plain meaning of the claim, it is apparent that this limitation requires a specific spatial arrangement of circuit elements. (CIB at 105 (citing CX-1044C at Q. 33).) Qimonda asserts that Fig. 2c of Maloney does not show a layout, but simply provides a highly simplified sketch of a circuit schematic. (*Id.* (citing CX-1044C at Q. 33).) According to Qimonda, because Maloney provides no guidance, there would be a virtually unlimited number of physical layouts embodying the circuit of Fig. 2c, which would not include two decoupled on-chip tracks. (*Id.* (citing CX-1044C at Q. 33).)

Regarding claim 4, Qimonda claims that Maloney does not describe that "said semiconductor function element is connected to said first supply line and to said connecting line at a given location, and said clamp element has a first terminal connected to said first supply line and a second terminal connected to said connecting line, in the immediate spatial vicinity of said given location." Qimonda asserts that Maloney does not show the specific spatial arrangement required by the claim. (CIB at 106 (citing CX-1044C at Q. 34).) Qimonda points to the portion of Maloney that states that "[t]o avoid difficulties with ground bus wiring, the scheme shown in Fig. 2c is used. The pi network cell can remain undisturbed as long as TG2 is added at the input buffer [TN<sub>IN</sub>, TP<sub>IN</sub>], sharing a common ground connection with it." (*Id.* (citing RX-205 at LSI-

337-665-0061847-61848; CX-1044C at Q. 34).) Qimonda argues that one of ordinary skill in the art would understand this statement in light of Fig. 2c to refer to circuit topology (*i.e.*, to the schematics themselves) as opposed to spatial vicinity. (*Id.* (citing RX-205 at LSI-337-665-0061847-61848; CX-1044C at Q. 34).)

Regarding claim 7, Qimonda asserts that Maloney does not describe that "said connecting line has a given resistance, said protective element includes a resistor connected between said terminal pad and said semiconductor function element, and said resistor has a resistance being adjusted for setting a sum of the resistance of said resistor and the given resistance to a predetermined value." Qimonda notes that Maloney states that: "[t]he rest of the protection 'pi network' is a series resistor (typically a few hundred ohms) and the aforementioned grounded gate NMOS device to clamp the gate oxide voltage on TNin and TPin." (CIB at 107 (citing RX-205 at LSI-337-665-0061847-61848; CX-1044C at Q. 35).) Qimonda states that based on this passage, Maloney, at best, only teaches a *series resistor*, and not the sum of the resistances, as having a predetermined value. (*Id.* (citing CX-1044C at Q. 35).)

**Commission Investigative Staff's Position**: Staff argues that Maloney does not anticipate claim 1 of the '434 patent. (SIB at 87.) Staff asserts that Maloney does not clearly and convincingly disclose "a second supply line for the first supply potential...being electrically conductively connected to said first supply line" as required in claim 1. (*Id.*) Staff notes that Dr. Cottrell opined that the two circuit elements labeled "BUS R" are internal-circuitry buses which are connected on-chip rather than being spatially separated to decouple voltage fluctuations. (*Id.*) Staff asserts that given Dr. Cottrell's opinion, and the lack of clear guidance from Maloney, there is no clear and convincing evidence that Maloney discloses the claimed second supply line. (*Id.* at 87-88.)

Discussion and Conclusion: Based upon the evidence before me, I find that

Respondents have clearly and convincingly demonstrated that Maloney anticipates claims 1, 2, 3, and 5 of the '434 patent.

Maloney was published in 1988, meaning that it is prior art pursuant to 35 U.S.C. § 102(a), (b). (RX-205; JX-1.) Maloney was not before the examiner during the prosecution of the '434 patent. (JX-1; JX-2.)

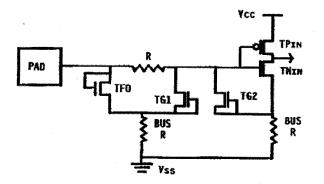

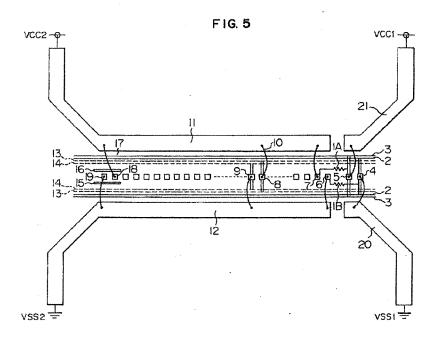

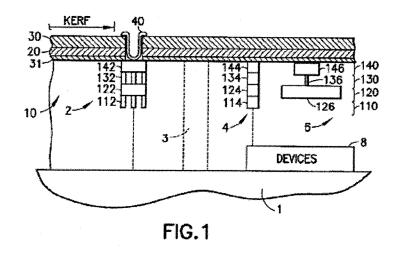

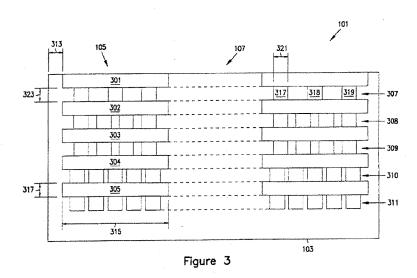

Respondents focus on Figure 2c of Maloney, which is reproduced below:

Fig. 2c. Improved input protection scheme, not affected by ground bus resistance.

#### (RX-205 at LSI-337-665-0061847.)

Regarding claim 1, there is no dispute that Maloney discloses a semiconductor component which includes a semiconductor body. (RX-205 at LSI-665-0061847-48; RX-774C at Q. 145; RDX-124.) Maloney discloses a terminal pad, labeled "PAD" in Figure 2c. (*Id.*) Maloney discloses a semiconductor function element, labeled as TPIN and TNIN in Figure 2c. (*Id.*) There is an electrically conductive connecting line connecting the terminal pad to the semiconductor function element in Figure 2c. (*Id.*)

Figure 2c discloses a protective element for protecting against electrostatic discharge, and the protective element is connected between the terminal pad and the semiconductor function element. (RX-205 at LSI-665-0061847-48; RX-774C at Q. 145; RDX-124.) Specifically, I find

that the protective element in Figure 2c comprises a thick field oxide device labeled "TFO," a series resistor, and a grounded gate NMOS device. (*Id.*) Maloney describes the TFO as "[t]he main protection device[.]" (RX-205 at LSI-337-665-0061848.) Maloney includes a first supply line being connected to the semiconductor function element. (RX-205 at LSI-665-0061847; RX-774C at Q. 145; RDX-124.) This is the line running from Vss (ground) to the semiconductor function element.

Maloney also includes the claimed second supply line, which is connected to the protective element and is electrically conductively connected to the first supply line, as both lines are connected to ground, Vss. (*Id.*) Finally, Maloney includes a clamp element for limiting a voltage to a clamp value. (*Id.*) The clamp element is labeled as TG2, and is connected to (1) the connecting line running between the terminal pad and the semiconductor function element; and (2) the first supply line. (*Id.*)

The only dispute between the parties is whether or not Figure 2c depicts two supply lines that are electrically conductively connected to each other, as required by claim 1. Mr. Fairbanks opines that there are two supply lines depicted in Maloney, while Dr. Cottrell opines that Figures 2b and 2c of Maloney show that the two "BUS R" labels represent resistance between circuit elements on a single wiring bus or on-chip track. (CX-1044C at Q. 31.)

Both parties focus on the following text from Maloney to support their conclusions:

Circuit designers will often separate power and ground buses on internal circuitry from "noisy" pad driver buses, so that *ground paths are returned to a common point (the Vss pad in this case) as shown in Fig. 2b*.

(RX-205 at LSI-337-665-0061847) (emphasis added.)

Qimonda and Dr. Cottrell state that Figure 2c of Maloney does not show a "pad driver," so there is no need for a separate ground bus. (CX-1044C at Q. 31.) Respondents argue that the

use of the plural "ground paths" demonstrates that there are two separate supply lines going to ground Vss.

I concur with Respondents. Both the figures and the text from Maloney clearly indicate that there are two separate conductive lines, one which goes from ground to the semiconductor function element, and another which goes from ground to the protective element. The above-quoted text of Maloney makes clear that there are multiple ground paths, demonstrating that there are two separate lines that connect to the ground potential Vss. While the quoted text refers to Figure 2b, Figure 2b is identical to Figure 2c, except that the clamp element TG2 is added in Figure 2c. (*Id.*) This change is not material to the above-quoted discussion, and thus I find that Maloney discloses multiple ground paths, which are the first and second supply lines.

The two lines each have their own bus resistance, which is depicted by the resistors "BUS R." (RX-205 at LSI-337-665-0061847.) Maloney makes clear that there are multiple buses (i.e. a first and second supply line) when it states that "[t]he ESD protection scheme as shown in Fig. 2a is an idelized one that does not recognize *ground bus wiring resistances* as shown in Fig. 2b." (*Id.*) (emphasis added).

In addition, Dr. Cottrell's analysis is based on an incorrect construction of "first supply line" and "second supply line." Dr. Cottrell states that the terms "should be properly interpreted to denote two on-chip conductor tracks being provided with the same supply potential, but spatially separated on-chip so that voltage fluctuations are decoupled." (CX-1044C at Q. 31.) As discussed *supra*, I construed "first supply line" and "second supply line" to mean "conductor track that carries a supply potential." I found that the claim did not require the additional language regarding voltage fluctuations, as this is discussed in the Background section of the specification when describing the prior art, and there is no indication that the claims should be so

limited. Thus, there is no requirement that voltage fluctuations are decoupled.

Claim 2 adds the requirement that there be at least one bond connection connecting the first and second supply lines together. I find that Maloney anticipates claim 2. Respondents identify the following language from Maloney:

Circuit designers will often separate power and ground buses on internal circuitry from "noisy" pad driver buses, so that ground paths are returned to a common point (the Vss pad in this case) as shown in Fig. 2b. Sometimes this common point is on a lead frame and *bond wire inductance* also appears on each separate path.

(RX-205 at LSI-337-665-0061847) (emphasis added.)

Mr. Fairbanks testified that when Maloney mentions bond wire inductance on the path, it means that there is a bond wire connection between the supply lines. (RX-774C at Q. 147.) Otherwise, there would not be any bond wire inductance without a bond wire connection. (*Id.*) I find that the identified language in Maloney makes clear that the first and second supply lines may be connected via a bond connection. Qimonda does not address this language from Maloney, instead relying on its argument that Maloney does not disclose the claimed first and second supply lines. (CIB at 105-106; CX-1044C at Q. 32.) For the reasons discussed *supra*, I have found that Maloney discloses the claimed first and second supply lines.

Claim 3 is dependent on claim 2 and adds the following limitations: "wherein said semiconductor function element has a terminal, said at least one bond connection has a terminal, said first supply line has a portion disposed between said terminal of said semiconductor function element and said terminal of said at least one bond connection, and said clamp element is connected to said portion of said first supply line." I find that Figure 2c of Maloney discloses these additional limitations. (RX-205 at LSI-337-665-0061847; RX-774C at Q. 149; RDX-124.)

Qimonda argues that claim 3 requires a specific spatial arrangement, and that is not

shown by the simplified circuit schematic in Figure 2c of Maloney. (CIB at 105; CX-1044C at Q. 33.) Claim 3 adds limitations regarding connections between components. Contrary to Qimonda's assertion, it does not require a specific spatial arrangement. Figure 2c of Maloney clearly depicts the connections required by claim 3, and thus anticipates the claim. (RX-205 at LSI-337-665-0061847; RX-774C at Q. 149; RDX-124.)

Claim 4 depends from claim 1 and requires that the "semiconductor function element is connected to said first supply line and to said connecting line at a given location, and said clamp element has a first terminal connected to said first supply line and a second terminal connected to said connecting line, in the immediate spatial vicinity of said given location." I construed "immediate spatial vicinity" to mean "connected to the connecting line at a point in the connecting line that corresponds to the portion of the first supply line that is between (1) the connection of the first and second supply lines; and (2) the connection of the semiconductor function element to the first supply line." Respondents fail to offer evidence that Maloney discloses this limitation as properly construed based on the intrinsic evidence. I find that Maloney does not clearly disclose this limitation. (RX-205 at LSI-337-665-0061847.)

Claim 5 is dependent from claim 1 and adds the following limitation: "wherein said clamp element includes an MOS transistor having a main current path connected to said connecting line and to said first supply line and a gate terminal connected to said first supply line." Maloney clearly discloses this claim element. (RX-205 at LSI-337-665-0061847; RX-774C at Q. 152; RDX-124.) Qimonda and its expert fail to present any argument to the contrary, instead relying on their argument regarding claim 1. (CIB at 106.)

Claim 7 is dependent from claim 1 and adds the following limitation: "wherein said connecting line has a given resistance, said protective element includes a resistor connected

between said terminal pad and said semiconductor function element, and said resistor has a resistance being adjusted for setting a sum of the resistance of said resistor and the given resistance to a predetermined value." Mr. Fairbanks testifies that this is disclosed in Maloney because Maloney discloses a resistor connected between the terminal pad and the semiconductor function element, and Maloney states that the resistance of the resistor is set at "typically a few hundred ohms." (RX-774C at Q. 155; RX-205 at LSI-337-665-0061848.)

I find that Maloney fails to disclose the limitation described in claim 7. While Maloney calls for a resistor to be placed between the terminal pad and semiconductor function element, there is no discussion in Maloney about the resistor having a resistance being adjusted for setting a sum of the resistance of said resistor and the given resistance to a predetermined value. Maloney only states that the resistor is typically a few hundred ohms. (*See* CX-1044C at Q. 35.) Thus, Maloney fails to anticipate claim 7.

#### 2. Krakauer-Mistry

**Respondents' Position**: Respondents contend that the paper titled "ESD Protection in a 3.3V Sub-Micron Silicided CMOS Technology," by David Krakauer and Kaizad Mistry, ELECTRICAL OVERSTRESS/ELECTROSTATIC DISCHARGE SYMPOSIUM PROCEEDINGS (Sept. 1992), at 250-257 ("Krakauer-Mistry") anticipates claims 1, 4, 5, 7, and 11 of the '434 patent. (RIB at 110.)

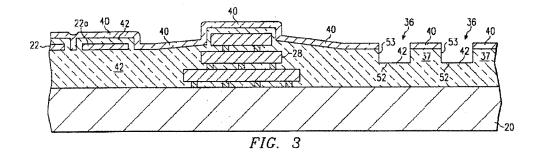

Respondents focus on Figure 7 from Krakauer-Mistry. Respondents assert that Krakauer-Mistry discloses a semiconductor component that includes a semiconductor body that has a terminal pad, a semiconductor function element, and an electrically conductive connecting line connecting the terminal to the semiconductor function element. (RIB at 111-112 (citing RX-774C at Q. 160; RX-188; RDX-125).) Respondents claim that Krakauer-Mistry discloses a

protective element for protecting against electrostatic discharge, with the protective element connected between the terminal pad and the semiconductor function element. (*Id.* at 112 (citing RX-774C at Q. 160; RX-188; RDX-125).)

Respondents argue that Krakauer-Mistry discloses a first supply line for the first supply potential (VSS), with first supply line connected to semiconductor function element. (RIB at 112 (citing RX-774C at Q. 160; RX-188; RDX-125).) According to Respondents, Figure 7 of Krakauer-Mistry discloses a second supply line for the first supply potential (VSS), with the second supply line connected to the protective element and electrically conductively connected to the first supply line. (*Id.* (citing RX-774C at Q. 160; RX-188; RDX-125).) Finally, Respondents claim that Figure 7 discloses a clamp element, which is connected to the connecting line and to the first supply line, for limiting a voltage applied to the clamp to a clamp value. (*Id.* (citing RX-774C at Q. 160; RX-188; RDX-125).)

Regarding claim 4, Respondents state that Krakauer-Mistry indicates that the clamp element should be connected to the first supply line close to the semiconductor function element, as the clamp element and the semiconductor function element share a common Vss symbol representing the first supply potential, whereas all other devices in Figure 7 connected by supply lines to the common supply potential have individual Vss symbols. (RIB at 113 (citing RX-774C at Q. 162; RX-188; RDX-125).) Additionally, according to Respondents, Krakauer-Mistry states that the clamp element in Figure 7 assists in protecting the semiconductor function element against Charged Device Model ("CDM") ESD events. (*Id.*) Respondents assert that one of ordinary skill in the art would appreciate that clamps that are meant to assist in CDM ESD protection must be placed close to the semiconductor function element they are meant to protect. (*Id.*)

Regarding claim 5, Respondents state that Figure 7 of Krakauer-Mistry discloses that the clamp element is a MOS device that has a main terminal connected to the first supply line and another main terminal connection to the connecting line , with the gate of the MOS device also connected to the first supply line. (RIB at 114 (citing RX-188).) Respondents claim that one of ordinary skill in the art would understand the reference to nMOST as a MOS device. (*Id.* (citing RX-774C at Q. 165; RX-188; RDX-125).)

Regarding claim 7, Respondents state that Figure 7 of Krakauer-Mistry discloses multiple resistances RI and RTC2. (RIB at 114 (citing RX-774C at Q. 166; RX-188; RDX-125).) Respondents assert that RI is part of the primary and secondary ESD protection structures, while RTC2 is part of the clamping element, including MTC2. (*Id.* (citing RX-774C at Q. 166; RX-188; RDX-125).) According to Respondents, the sum of the resistance values of RI and RTC2, and also the resistance of the connecting line is never arbitrarily chosen but always set to a predetermined value, or at least to a range of predetermined values. (*Id.* at 114-115 (citing RX-774C at Q. 166; RX-774C at Q. 166; RX-188; RDX-125).) Respondents state that if the sum of the resistance is not set appropriately, the resistors will fail. (*Id.* at 115 (citing RX-774C at Q. 166; RX-188; RDX-125).)

Regarding claim 11, Respondents state that Figure 11 of Krakauer-Mistry discloses typical bi-directional I/O [input/output] pin circuitry with ESD protection. (RIB at 115 (citing RX-774C at Q. 170; RX-188; RDX-126).) Respondents claim that Figure 11 comprises the "Input pin" configuration of Figure 7 plus two additional semiconductor function elements that form a classic CMOS output driver, which provide Input-Output or Bi-directional I/O capability at the Pin. (*Id.* (citing RX-774C at Q. 170; RX-188; RDX-188; RDX-188; RDX-126).) Respondents state that Semiconductor Function Elements MP1 and MN1 are output devices that are connected to the

terminal pad (PIN) by the connecting line and to the second supply line (flagged with the red line in the annotated figure, below). (*Id.* (citing RX-774C at Q. 170; RX-188; RDX-126).) According to Respondents, Semiconductor Function elements MP2 and MN2 are input stage devices as discussed above in regard to claim 1 and Fig. 7. (*Id.* (citing RX-774C at Q. 170; RX-188; RDX-126).)

In their reply brief, Respondents address Qimonda's arguments. Respondents argue that Qimonda attempts to improperly read limitations into claim 1 to save it from being found inval*id.* (RRB at 57.) Respondents reiterate that Krakauer-Mistry discloses two supply lines as depicted in RDX-125. (*Id.*)

In response to Qimonda's argument regarding claim 4, Respondents note that Krakauer-Mistry shows the clamp element MTC2 connected to the first supply line close to the semiconductor function element, and it states that the purpose of the clamp element is to "assist in protecting the semiconductor function element against CDM ESD events." (RRB at 58 (citing RX-188).) According to Respondents, one of ordinary skill in the art would know that clamps meant to assist in CDM ESD protection must be placed close enough to the semiconductor function element to provide effective protection. (*Id.* (citing RX-774C at Q. 162).)

Regarding claim 7, Respondents allege that Qimonda takes inconsistent positions when arguing infringement and validity. Specifically, Respondents state "when arguing invalidity, Qimonda contends that setting the value of one specific resistor does not address the sum of the resistance for the resistor and the connection line. Yet Qimonda takes a contrary position on infringement." (RRB at 59.)

Regarding claim 11, Respondents allege that Qimonda misreads the claim, as the claim requires an input switching stage, and not an output switching stage. Respondents state that

Krakauer-Mistry discloses an input stage or input buffer and an output buffer. (RRB at 59.) Respondents also claim that Qimonda is incorrect in arguing that Krakauer-Mistry does not disclose an output driver stage connected to the terminal pad and the second supply line. (*Id.* at 60 (citing RX-774C at Q. 169-170).)

**Qimonda's Position**: Qimonda argues that Krakauer-Mistry does not anticipate claims 1, 4, 5, 7, or 11. Regarding claim 1, Qimonda claims that Krakauer-Mistry does not describe the claim elements of "a first supply line for a first supply potential" and "a second supply line for the first supply potential . . . being electrically conductively connected to said first supply line." (CIB at 107 (citing CX-1044C at Q. 36, 37; CDX-38 at QAG-665-ITC-0233822).) According to Qimonda, a person of ordinary skill in the art at the time of filing of the '434 patent would have found no indications in Krakauer-Mistry that the various ground nodes collectively labeled "Vss" would be would be spatially arranged in any specific way, or coupled or decoupled in any specific fashion. (*Id.* (citing CX-1044C at Q. 37; CDX-38 at QAG-665-ITC-0233822. Qimonda contends that Krakauer-Mistry teaches only a single supply line, VSS, connected to ground. (*Id.* (citing RX-188 at LSI-337-665-0147597; CX-1044C at Q. 37; CDX-38 at QAG-665-ITC-0233822).)

In addressing the dependent claims, Qimonda argues that because Krakauer-Mistry does not anticipate claim 1, it does not anticipate any of the dependent claims. (CIB at 108-110).) Regarding claim 4, Qimonda argues that Krakauer-Mistry does not describe that "said semiconductor function element is connected to said first supply line and to said connecting line at a given location, and said clamp element has a first terminal connected to said first supply line and a second terminal connected to said connecting line, in the immediate spatial vicinity of said given location." (*Id.* at 108 (citing CX-1044C at Q. 38).) Qimonda asserts that the plain

meaning of the claim requires a specific spatial arrangement of circuit elements, which is not shown in Krakauer-Mistry. (*Id.* (citing CX-1044C at Q. 38).) Qimonda states that the reference in Krakauer-Mistry to Charged Device Model (CDM) ESD events does not teach any physical proximity, since physical proximity is only one of the many factors that determine the effectiveness of an ESD protection circuit. (*Id.* at 108-109 (citing CX-1044C at Q. 38).)<sup>47</sup>

Regarding claim 7, Qimonda argues that Krakauer-Mistry does not describe that "said connecting line has a given resistance, said protective element includes a resistor connected between said terminal pad and said semiconductor function element, and said resistor has a resistance being adjusted for setting a sum of the resistance of said resistor and the given resistance to a predetermined value." (CIB at 109 (citing CX-1044C at Q. 39).) Qimonda states that Krakauer-Mistry only teaches setting the value of the resistor R1 to a specific value (150  $\Omega$ ) and does not address the sum of the resistance of the resistor and the connecting line. (*Id.* (citing CX-1044C at Q. 39).)

Regarding claim 11, Qimonda states that Krakauer-Mistry does not describe that "said semiconductor function element is an output switching stage, and including an output driver stage being connected to said terminal pad and to said second supply line." (CIB at 110 (citing CX-1044C at Q. 40).)

In its reply brief, Qimonda reiterates the argument that Krakauer-Mistry does not teach a "first supply line" and a "second supply line" as required by claim 1. (CRB at 51.) According to Qimonda, a person of ordinary skill in the art at the time of filing of the '434 patent would have found no indications in Krakauer-Mistry that the various ground nodes collectively labeled "Vss" would be would be spatially arranged in any specific way, or coupled or decoupled in any

<sup>&</sup>lt;sup>47</sup> Qimonda does not raise any arguments unique to claim 5. Qimonda contends that because Krakauer-Mistry does not anticipate claim 1, it does not anticipate claim 5. (CIB at 109.)

specific fashion. (*Id.* (citing CX-1044C at Q. 37; CDX-38 at QAG-665-ITC-0233822).) Qimonda assert that Krakauer-Mistry teaches only a single supply line, VSS, connected to ground. (*Id.* (citing RX-188 at LSI-337-665-0147597; CX-1044C at Q. 37; CDX-38 at QAG-665-ITC-0233822).)

**Commission Investigative Staff's Position**: Staff argues that Krakauer-Mistry fails to anticipate claims 1, 4, 7, and 11 because it fails to clearly and convincingly disclose "a second supply line for the first supply potential...being electrically conductively connected to said first supply line" as required by claim 1. (SIB at 88.) Staff claims that when comparing Figure 7 of Krakauer-Mistry to Figure 3 of the '434 patent, it becomes apparent that Krakauer-Mistry does not clearly and convincingly disclose the above-quoted limitation. (*Id.* at 89.) Staff states that "Mr. Fairbanks' conclusion that this limitation is clearly and convincingly met based on Figure 7 of Krakauer-Mistry requires too big of an inferential leap and the application of impermissible hindsight to invalidate Claim 1." (*Id.*)

**Discussion and Conclusion**: Based upon the evidence before me, I find that Respondents have not clearly and convincingly demonstrated that Krakauer-Mistry anticipates any of the asserted claims of the '434 patent.

Krakauer-Mistry was published in 1992, meaning that it is prior art pursuant to 35 U.S.C. § 102(a), (b). (RX-188; JX-1.) Krakauer-Mistry was not before the examiner during the prosecution of the '434 patent. (JX-1; JX-2.)

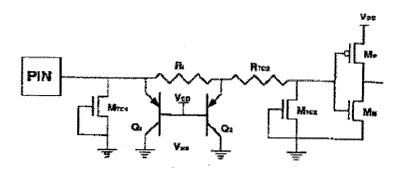

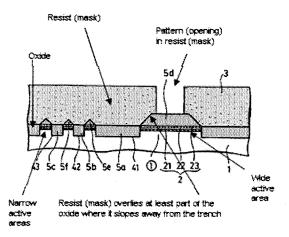

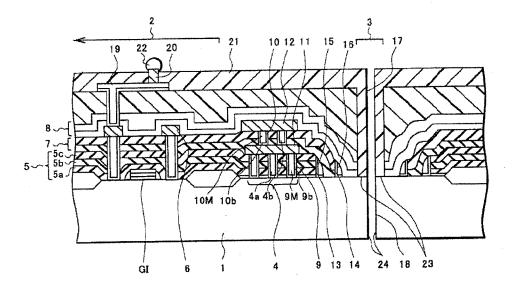

Respondents focus on Figure 7 of Krakauer-Mistry, which is reproduced below:

Figure 7: Typical 3.3V input pin with ESD protection.

(RX-188 at LSI-337-665-0147597.)

The only dispute between the parties is whether or not Figure 7 depicts two supply lines that are electrically conductively connected to each other, as required by claim 1. Mr. Fairbanks opines that Figure 7 depicts two supply lines that are electrically conductively connected to each other. (RX-774C at Q. 160.) Dr. Cottrell opines that this claim limitation is not met. (CX-1044C at Q. 37.) Dr. Cottrell states that the claim limitation should be interpreted to require two on-chip conductor tracks being provided with the same supply potential, but spatially separated on chip so that voltage fluctuations are decoupled. (*Id.*) Dr. Cottrell then states:

Based on my experience, a person of ordinary skill at the time of filing of the '434 Patent would have found no indications in the Krakauer-Mistry paper reference that the various ground nodes collectively labeled "Vss" would be would be [*sic*] spatially arranged in any specific way, or coupled or decoupled in any specific fashion.

(Id.)

Claim 1 requires two separate supply lines: the first supply line and the second supply line. It is undisputed that because the claim calls for two separate supply lines, the supply lines must be spatially separated. (CIB at 64; RIB at 78.) Figure 7 does not clearly and convincingly disclose two separate supply lines. Figure 7 merely shows the alleged protective element, clamp element, and semiconductor function element all connected to a common ground. (RX-188 at

LSI-337-665-0147597.) Nothing demonstrates that there are separate first and second supply lines running from ground to the elements as called for in claim 1. Mr. Fairbanks' demonstrative artificially creates two separate supply lines, labeled in red and green, but this goes beyond the disclosure of Krakauer-Mistry. (RDX-125.) Thus, Respondents have failed to prove that Krakauer-Mistry anticipates the asserted claims.<sup>48</sup>

#### 3. Strauss-White

**Respondents' Position**: Respondents contend that the paper "Protecting N-Channel Output Transistors from ESD Damage," by Mark S. Strauss and Marvin H. White, ELECTRICAL OVERSTRESS/ELECTROSTATIC DISCHARGE SYMPOSIUM PROCEEDINGS (Sept., 1991), at 110-119 ("Strauss-White") anticipates claims 1, 4, 7, and 11 of the '434 patent. (RIB at 116.)

Regarding claim 1, Respondents state that Strauss-White discloses a semiconductor component. (RIB at 116 (citing RX-774C at Q. 175; RX-187; RDX-127).) Respondents state that one of ordinary skill in the art would have understood Strauss-White to disclose a semiconductor body that has a terminal pad, a semiconductor function element, and an electrically conductive connecting line connecting the terminal to the semiconductor function element. (*Id.* at 117 (citing RX-774C at Q. 175; RX-187; RDX-127).)

Respondents point to Figure 2 of Strauss-White and state that it discloses a protective element for protecting against electrostatic discharge, with the protective element connected between the terminal pad and the semiconductor function element. (RIB at 118 (citing RX-774C at Q. 175; RX-187; RDX-127).) According to Respondents, Figure 2 of Strauss-White also discloses a first supply line for the first supply potential (VSS), with the first supply line

<sup>&</sup>lt;sup>48</sup> Claim 1 is independent, and all of the other asserted claims in the '434 patent are dependent on claim 1. Thus, these claims are not anticipated by Krakauer-Mistry for the same reasons that claim 1 is not anticipated by Krakauer-Mistry. *In re Fritch*, 972 F.2d 1260, 1266 (Fed. Cir. 1992); *In re Royka*, 490 F.2d 981, 983-985 (C.C.P.A. 1974).

connected to semiconductor function element. (*Id.* (citing RX-774C at Q. 175; RX-187; RDX-127).) Respondents next state that Figure 2 of Strauss-White discloses a second supply line for the first supply potential (VSS), with the second supply line connected to the protective element and electrically conductively connected to the first supply line. (*Id.* (citing RX-774C at Q. 175; RX-187; RDX-127).) Lastly, Respondents state that Figure 2 of Strauss-White discloses a clamp element that is connected to the connecting line and to the first supply line, for limiting a voltage applied to the clamp element to a clamp value. (*Id.* at 118-119 (citing RX-774C at Q. 175; RX-187; RDX-127).)