REAL TIME

PICTURE PROCESSOR:

DESCRIPTION AND SPECIFICATION

National Cancer Program NCI/IP Technical Report #7

March 31, 1976

Peter Lemkin, George Carman,\* Lewis Lipkin, Bruce Shapiro, Morton Schultz

U.S. Department of Health, Education, and Welfare / National Institutes of Health / National Cancer Institute

#### NCI/IP-76/03

REAL TIME PICTURE PROCESSOR: DESCRIPTION AND SPECIFICATION

NCI/IP Technical Report #7

March 31, 1976

Peter Lemkin, George Carman,\* Lewis Lipkin, Bruce Shapiro, Morton Schultz

Image Processing

Division of Cancer Biology and Diagnosis

National Cancer Institute

National Institutes of Health

Bethesda, Maryland 20014

\*Carman Electronics, Inc. Corvallis, Oregon 97330

"We here highly resolve . . . "

# TABLE OF CONTENTS

SECTION

|   |                | SECTION                                     |   |   | PAGE |

|---|----------------|---------------------------------------------|---|---|------|

|   |                |                                             |   |   |      |

| 1 | Introduction   |                                             |   | • | • 3  |

|   | 1.1            | Overview of this paper                      |   |   | . 4  |

|   | 1, 2           | RTPP design goals                           | • | • | - 4  |

|   | 1.2.1          | Picture operations                          |   |   | • 6  |

|   | 1.2.2          |                                             | • |   | - 7  |

|   | 1.2.3          | A level IV gray scale machine - 3           |   |   | •    |

|   |                | address machine                             |   | • | • 8  |

|   | 1.3            | The configuration of the RTPP               |   |   | - 10 |

|   | 1.3.1          | Axiomat microscope                          |   | ٠ | - 10 |

|   | 1.3.2          | Video input and output devices              |   |   | • 10 |

|   | 1.3.3          | Buffer memories - BM                        |   |   | • 11 |

|   | 1.3.4          | Triple line buffers for image addressing    |   |   | 12   |

|   | 1,3,5          | General Picture Processor                   |   | • | 19   |

|   | 1.3.6          | Quantimet controller                        |   |   | 20   |

|   | 1.3.7          | Control of the RTPP by the PDP8e            | _ | • | 20   |

|   | 1.4            | The RTPP as a picture processing peripheral | • | - | 21   |

|   | 1.5            | Cell Modeling System - CELMOD               | • | • |      |

|   | 1.6            | DDTG - the RTPP debugger/monitor            | • | • | 21   |

|   | 1.7            | RTPP Compiler/Assembler - MAINSAIL/GPPASM . | • | • | 24   |

|   | 1.8            | GPP Microprogram Assembler - MICROP         |   | • | 24   |

|   | •              |                                             | • | • | 25   |

| 2 | Quantimet subs | ystem                                       | _ |   | 26   |

|   | 2.1            | Quantimet modules                           | • | • | 26   |

|   | 2.1.1          | Scanner - System Control module             | • | • | 26   |

|   | 2.1.2          | System display module                       | • | • | 27   |

|   | 2.1.3          | Variable Frame and Scale module             | • | • | 27   |

|   | 2.1.4          | Detector modules                            | • | • | 28   |

|   | 2.1.5          | Timbs and                                   | • | • | 28   |

|   | 2.1.6          |                                             | • | • | 28   |

|   | 2.1.7          | 97 M (                                      | • | • | 28   |

|   | 2.1.8          |                                             | • | • | 29   |

|   | 2.1.9          | runction Computer module                    | • | • | 29   |

|   | 2. 1. 10       | m : • • •                                   | • | • | 29   |

| - | 2.2            |                                             | • | • | 29   |

|   | 2.3            | Microprogramming QMT modules                | • | • | 29   |

|   | 2.3.1          | PDP8e control of the Quantimet              | • | • | 30   |

|   | 2.4            | Quantimet status register - QSTAT           | • | • | 30   |

|   |                | The mask register module                    | • | • | 30   |

|   | 2.5            | QMT cursor                                  | • | • | 32   |

| 3 | Buffer memory  |                                             |   |   |      |

| , | 3.1            |                                             | • | • | 33   |

|   |                | Physical BM memory addressing               | • | • | 35   |

|   | 3.1.1          | BM controller accessing priorities          | • | • | 36   |

| Ц | mrinla lina bu | ff on in a                                  |   |   |      |

| 7 | Triple line bu |                                             | • | • | 37   |

|   | 4.1            | Programming the Triple Line Buffer          | • | • | 37   |

|   | 4.2            | Alternate Neighborhood Accessing Methods .  | • | • | 38   |

| 5 | CDD - conom-1  |                                             |   |   |      |

| , |                | picture processor                           | • | • | 41   |

|   | 5.1            | Operation of the GPP                        | • | • | 45   |

|    | 5.2                  | General regi              | ister  | addr   | ess    | spac       | ce          | •   | •           |       | • | • | • | 47  |

|----|----------------------|---------------------------|--------|--------|--------|------------|-------------|-----|-------------|-------|---|---|---|-----|

|    | 5.2.1                | GR Addres                 |        |        |        |            |             |     |             |       | • | • | • | 47  |

|    | 5.2.2                | Addressi                  | ng seg | uenc   | e.     |            |             |     |             |       |   | • | • | 48  |

|    | 5.2.3                | Auto-inde                 |        |        |        |            |             |     |             |       |   |   |   | 49  |

|    | 5.3                  | GPP input/or              |        |        |        |            |             |     |             |       |   |   |   | 49  |

|    | 5.3.1                | Line buf                  |        |        |        |            |             |     |             |       |   |   |   | 7.2 |

|    |                      |                           | isters |        | •      |            |             |     |             |       |   |   |   | 50  |

|    | 5.3.2                | PDP8e/GP1                 |        |        |        |            |             |     |             |       |   |   |   | 50  |

|    | 5.4                  | PDP8e/GPP s               |        |        |        |            |             |     |             |       |   |   |   | 51  |

|    | 5.4.1                | Software                  |        |        |        |            |             |     |             | _     | • | _ | _ | 71  |

|    | 55,4,                |                           | eral 1 |        |        |            |             |     | _           | _     | _ |   | _ | 51  |

|    | 5.5                  | Running the               |        |        |        |            |             |     | •           | •     | • |   | • | 51  |

|    | 3.3                  | numing the                | GLI    | •      | •      | •          | •           | •   | •           | •     | • | • | • | J.  |

| 6  | Implementation       | of the RTDD               |        |        |        |            |             |     |             |       | _ | _ | _ | 53  |

| U  | 6. 1                 | The GPP conf              |        |        |        |            |             |     |             |       | • | • | • |     |

|    | 6.1.1                | Micropro                  | tram i | netr   | 110+1  | On         | RNF<br>C    | σra | mma         | r     | • |   | • | 53  |

|    | 6.2                  | Microprod<br>Internal Con | gram ı | .usci  | ac De  | sein       | D W.T       | gru | . III III C |       | • |   | • | 53  |

|    | 6.3                  | Physical co               | netene | tion:  | o of   | +ha        | מיתים<br>נו | Ď   | •           | •     | • | • | • | 54  |

|    | 6.4                  | Buffer memor              |        |        |        |            |             |     |             |       |   |   | • | 54  |

|    | 0.4                  | parter memor              | гу тиг | teme   | in ca  | TOH        | •           | •   | •           | •     | • | • | • | 55  |

| 7  | References           |                           |        |        |        |            |             |     |             |       |   |   |   | 56  |

| ,  | References           | •                         | • •    | • •    | •      | •          | •           | •   | •           | •     | • | • | • | 50  |

| A  | GPP instruction      | get .                     |        |        |        | _          | _           | _   | _           | _     | _ | _ | _ | 58  |

| a  | A. 1                 | GPP operator              |        |        |        |            |             |     |             |       |   |   | - | 58  |

|    | A. 2                 | Effective a               |        |        |        |            |             |     |             |       |   |   |   | 59  |

|    | A. 3                 | Instruction               |        |        |        |            |             |     |             |       |   |   |   | 59  |

|    |                      | Operator gre              |        |        |        |            |             |     |             |       |   |   | • | 61  |

|    | A.5                  | List of GPP               |        |        |        |            |             |     |             | •     | • | • | • | 75  |

|    | R.J                  | PISC OF GIL               | Obere  | LEOLS  | , Di   | c i b      |             | •   | •           | •     | • | • | • | 13  |

| В  | GPP I/O regist       | ers and cont              | rol na | ופתו   | 1 i al | 1+9/       | ewi t       | che |             | -     | _ |   | _ | 78  |

| L) | B. 1                 | Status regi:              |        |        |        |            |             |     |             |       |   |   |   | 78  |

|    | B. 2                 | GPP line bu               |        |        |        |            |             |     |             |       |   |   |   | 79  |

|    | B. 3                 | GPP front p               | anol o | 'Ant I | 018    | , U L      | ~g~         |     | ~           | -     | • |   | • | 80  |

|    | B.3.1                | Lights of                 | n the  | CDD    | froi   | 1+ n       | anol        | •   | •           | •     |   | • | • | 80  |

|    | B.3.2                | Switches                  |        |        |        |            |             |     |             |       |   |   |   | 81  |

|    | D. J. Z              | DATIONES                  | On Ci  | ie Gi  | . L.   | LOHE       | Pui         |     | •           | •     | • | • | • | 01  |

| С  | PDP8e I/O tran       | for instruc               | tions  | for    | tho    | Bill D     | D           |     |             | _     |   | _ | _ | 83  |

| C  |                      | PDP8e IOTs                |        |        |        |            |             | · – | ~ ^1        | it ro | 1 | • | • | 0.5 |

|    | C. 1                 |                           | k.     |        |        |            |             |     |             |       | _ |   |   | 83  |

|    | C.1.1                | Allocation                |        |        |        | •<br>• • • |             |     | OPI         | enc.  | • | • | • | 0.5 |

|    | C. F. T              |                           | ds .   |        |        | • •        | _           |     |             |       |   | _ |   | 00  |

|    | . C.1.2              | Quantime                  |        |        |        |            |             |     |             | •     | • | • | • | 90  |

|    | C.1.3                | The QMT                   |        |        | _      |            |             |     |             | •     | • | • | • | 93  |

|    | C.1.4                | Quantime                  |        |        |        |            |             |     |             |       |   | • | • | 94  |

|    |                      | Shift re                  |        |        |        |            |             |     |             |       | • | • | • | 95  |

|    | C.1.5                | Reading                   |        |        |        |            |             |     |             |       | e | • | • | 97  |

|    | C.1.6                |                           |        |        |        |            |             |     |             |       | • | • | • | 98  |

|    | C.1.7                | Allocation                |        |        |        |            |             |     |             |       | • | • | • | 100 |

|    | C. 2                 | PDP8e IOT I               |        |        |        |            |             |     |             |       |   | • | • | 102 |

|    | C.3                  | PDP8e IOT I               |        |        |        |            |             |     |             |       |   | • | • | 103 |

|    | C.4                  | PDP8e IOT I               |        |        |        |            |             |     |             |       |   | • | • | 105 |

|    | C.5                  | PDP8e IOT I               |        |        |        |            |             |     |             |       | • | • | • | 106 |

|    | C.6                  | Allocation                |        |        |        |            |             |     |             |       | • | • | • | 107 |

|    | C.6.1                | Alphabet                  |        |        |        |            |             |     |             |       | • | • | • | 107 |

|    | c.7                  | PDP8e Devic               |        |        |        |            |             |     |             |       | • | • | • | 110 |

|    | c.7.1                | Numerica                  | I Lis  | ting   | oi     | 5 D B 8    | e I(        | )TS | •           | •     | • | • | • | 111 |

| D  | Examples of pr       | ogramming th              | e GPP  |        |        | •          |             |     |             |       |   | • |   | 115 |

| _  | THE THE PERSON OF PE | - ,                       |        | - '    |        | -          | -           |     |             |       |   |   |   |     |

|   |                |                                          | iii |

|---|----------------|------------------------------------------|-----|

| ı | D. 1           | Gradient used in Kirsch algorithm        | 11. |

|   | D.2            | Eight neighbor direction list processing | 11  |

|   | D.3            | Edge and curve detection                 |     |

|   | D. 4           | Highogram computation                    | 118 |

|   | D.5            | Histogram computation                    | 12. |

|   | •              | Haltpoint I/O example                    | 122 |

|   | D.6            | Random Neighborhood Accessing            | 123 |

|   | D.7            | Area and perimeter computation           | 124 |

|   | D.8            | Run length code of detected object       | 126 |

| E | GPPASM BNF Gra | ammar Specification                      | 127 |

L

#### LIST OF FIGURES

| • | • | 14  |

|---|---|-----|

|   | • | 15  |

|   |   |     |

|   |   |     |

|   |   |     |

|   |   |     |

|   | • | • • |

#### ν

## LIST OF TABLES

.

| lapre     | ۱.   | Examples of some RTPP | instructions |   |   | _ |   | _ | _ | _ | _ | _ | E 0 |

|-----------|------|-----------------------|--------------|---|---|---|---|---|---|---|---|---|-----|

| Table     | 2.   | GPP Instruction Croun | Colombias    | • | - | • | • | • | • | • | • | • | 20  |

| * u D * C | 44 4 | GPP Instruction Group | serection .  | • | • | • | • | • | • | • | • | • | 60  |

|           |      |                       |              |   |   |   |   |   |   |   |   |   |     |

NCI/IP-76/03

Real Time Picture Processor - Description and Specification

NCI/IP Technical Report #7

Peter Lemkin, George Carman\*, Lewis Lipkin, Bruce Shapiro, Morton Schultz

Image Processing Unit

Division of Cancer Biology and Diagnosis

National Cancer Institute

National Institutes of Health

Bethesda, Md. 20014

\*Carman Electronics, Inc.

Corvallis, Oregon

March 31, 1976

#### ABSTRACT

The concepts and general design specifications of a new hardware picture processor are presented. The design was strongly influenced by the characteristics of biological images. This device, now in the early stages of construction at the National Institutes of Health, will meet some of the requirements for interactive design, specification and testing by biologists of algorithms for cell classification, description and measurement. The RTPP is but one component, albeit a major one, of our entire system which is intended to permit on-line description construction by the cytologist.

#### SECTION 1

#### Introduction

This paper discusses the functional hardware design specification of a Real Time Picture Processor (RTPP) ([Lem74], [Carm74]) for use in designing image processing systems for biological materials. Real time, as is used here, denotes time proportional to that required for comfortable human interaction.

The concepts and general design specifications of a new hardware picture processor are presented. The design was strongly influenced by the characteristics of biological images This device, now in the early stages of construction at the National Institutes of Health, will meet some of the requirements for interactive design, specification testing by biologists of algorithms for classification, description and measurement. Additional detailed hardware specifications of the Real Time Picture Processor, RTPP, are documented [Carm76]. The RTPP is but one component, albeit a major one, of our entire system which is intended to permit on-line description construction by the cytologist. The overall discussion of the system components in [Lem76c].

The Real Time Picture Processor in its role as a microscope controller is designed to perform at least the set of operations performed by the NCI Grain Counter-1.1 [LipL74]. These operations include joystick control of an optical microscope stage in X, Y, and focus. The RTPP, in addition, allows stepping motor control of a 4:1 microscope zoom, a rotary monochromator, and a rotary neutral density filter.

The system is designed for extremly rapid serial digital processing of digitized images to be carried out in what for the user, seems like, real time. Special purpose hardware makes this speed possible. Output from the RTPP is in the form of images to be displayed, lists of properties of objects in the image, or processed images. Because of powerful gray scale manipulation instructions, computations are not limited to processing planes of binary valued images.

These capabilities allow flexible experimentation with an on-line microscope image picture processing facility. Employing this facility, users have the ability to generate precise definitions of biological cell classifications using the RTPP as input for an interactive relational data model residing on a remote PDP10 computer. Furthermore, the system will allow the user to make measurements of cell parts and to develop heuristic measures for cell characterization.

Because processing is fast (on the order of tenths to a few seconds), the interaction between user and the system is

well matched to allow for experimentation with more complex algorithms than usually attempted with serial systems. Several papers ([Lem74] and [Lem75]) give reviews of some recent special purpose image processing hardware.

# 1.1 Overview of this paper

Section 1 introduces the rationale on which the structure of the RTPP is based. Sections 2 through 5 discuss components: i.e. the Quantimet (QMT), buffer memories (BMs), triple line buffers, and General Picture Processor (GPP) respectively in more detail. Section 6 discusses the physical implementation of the RTPP while Section 7 comprises references. Appendix A details the GPP instruction set while Appendix B lists the GPP I/O registers and GPP I/O lights and switches. Appendix C presents the PDP8e Input Output Transfer instructions used in the RTPP. Appendix D gives several examples, including estimated running times, of several algorithms programmed for the RTPP.

# 1.2 RTPP design goals

There were several (sometimes conflicting) design goals used in defining what should go into a picture processing facility such as the RTPP. Long experience in picture processing on general purpose serial machines has resulted in the production of picture processing packages such as PAX [John E70]. Some of these operations consist of simple pixel boolean binary planar operations, 4 and 8 neighbor operations, and then more complex operations such as blob finding, etc. Obviously, as the complexity of an operation increases, so does complexity of its hardware implementation. decided that neighborhood processing was the upper limit of complexity that the resources availiable to our group would allow us to undertake. Several years of biological experience posed another requirement: i.e. that grayscale texture measure algorithms be easy to implement. This means doing integer arithmetic on gray scales images rather than boolean arithmetic on planes of binary images.

A general gray scale parallel processor is an unrealistic goal. The complexity of such a device, (at the current state of the hardware art and occasioned by the combinatorics of the required hardware interconnections) place it well beyond the construction abilities of a small group. The cost of such a device also would make it difficult to justify if it were to be dedicated rather than a shared resource.

As will be seen we have drawn often from the good efforts of other computer and picture processing system designs, (especially [Dec71], [Dec72a], [Dec72b], [Dec67], 1.1 - 1.2

[Thor70]) as well as many other influences. It was hoped that some of the best (and not necessarily the most complex or costly) features of some of the above machines could be incorporated into our design.

Before going into the design of the RTPP the definitions of some of the terms used in the rest of this paper are given.

# Picture - set of gray values

A image part of a picture is a square approximation of the corresponding real image. Each element in this sampling array is said to have an integer gray value called a pixel. This gray value is a measure of the darkness or whiteness of that pixel. In our discussion, white will be zero and black 255. This representation is said to have 256 linearly resolvable gray levels or values. The gray value is generaly given in the range of the powers of a binary number as it is usually derived from the output of an analogue to digital i.e. 8, 16, 32, 64, 128, converter. 256 etc. alternative view (which lies at the basis of implementations as PAX) of an image is as a set of overlying binary arrays more commonly called binary planes. Thus 256 gray values is represented by 8-bits or 8 binary planes.

#### Neighborhood

Within a image, one usually deals with the concept of neighborhood. A neighborhood is a set of pixels close to (usually touching) a given pixel. An example of this is all pixels touching a given pixel in a array. For a square array there are 8 such pixels and consequently this 3x3 set of pixels is called the 8 neighborhood or 8 nearest neighbors. In this paper and in the RTPP the labeling of the 3x3 neighborhood is as follows:

3 2 1 4 8 0 5 6 7.

This choice of neighborhood labeling facilitates chain coding as the pixel index corresponds to its angle with the central pixel divided by 45 degrees.

#### Current pixel

The current pixel is the central pixel (8) in this 3x3 array. The current neighborhood is the 3x3 array surrounding the current pixel.

# Neighborhood operation

A neighborhood operator is a unary or binary operator which maps neighborhoods into pixels. One of the ways the neighborhood operator works is to do various operations on parts of the neighborhood array as specified by an ordered list

1

of pixels to be operated on. When this list is ordered in terms of the orientation of neighborhood elements, it is called a direction list.

#### Pixel operator

A pixel operator is a unary or binary operator which maps pixels into pixels in a 1 to 1 (x,y) mapping.

The RTPP performs neighborhood operations by executing a program on a neighborhood for each neighborhood in the plane. This is actually done using special purpose hardware called the General Picture Processor (GPP) which will be discussed below. The GPP is designed to allow pixel operations to be performed on all pixels of a 3x3 neighborhood within a single I/O access, thus allowing 3 lines to be processed at a time.

### 1.2.1 Picture operations

Image data processing in particular consists of doing mostly binary argument algebraic operations. These can be enumerated in an interesting way as shown below. The following are binary algebraic picture operations where "o" is a general operator. Let I1, I2 and I3 be images. Then,

I1 o I2 --> I3

I1 o -->I3

I1 o I2 --> a property list

I1 o I2 --> a relational data structure.

The operation I1 o -->I3 may be thought of as either a unary operation or a binary operation with a null second operand.

These picture operations might include such operations as boolean: bit set, bit clear, bit complement, and, or, exclusive or, equivalence; direction list processing; maxima; minima; Fourier transforms; threshold slicing: scaling: component labeling: propagation of edges: edge finding: pixel-wise addition, subtraction, multiplication, division; of images; gradient; gray level and shifting histogram. Run-length/gray-scale texture histograms should also be computable by the GPP as well a large class of other picture operations. The PAX functions mentioned above are described by Johnson [LipB70].

In Appendix D sample GPP programs are shown, which compute some of the above mentioned operations and for which timing estimates are given.

## 1.2.2 Picture operations as binary operations

These basic binary argument relations on picture data are typical of picture processing in systems. What varies is the complexity of the operation "o". The increasing complexity of operations in the binary image plane is shown below in five increasingly complex levels I to V. Let "x" below be a pixel in a NxN neighborhood. As will be shown, an analogous hierarchy also exists for gray scale machines.

Let Ij(k) be the k'th pixel in picture j.

(I) Pixel (picture element) operations:

$$I1(k) \circ I2(k) --> I3(k)$$

.

(II) Neighborhood operations around a pixel into a pixel:

(III) Neighborhood contextual operations into a pixel:

(IV) Neighborhood operations into a neighborhood:

(V) special high level functions: edge detection, differentiation, smoothing, propagation, etc.

With progress from level I to IV and V, the increasing complexity (number of connections, number of nodes, number of modules) for a hardware circuit to perform such an operation increases. We use this wiring complexity as an estimate of the "complexity" of the operation and thus to characterize the complexity of a given level of operation.

Most small neighborhood parallel binary machines exhibit maximum complexity of levels II or III. For an NxN 2 binary plane image these have complexity levels between N and N (e.g. for a 3x3 array this is 9 to 81). The ILLIAC III is an

example of a level IV binary machine.

The same five levels of operations could be applied to the class of gray scale image machines. There is only one known existing gray scale processor, the ILLIAC IV.

It is interesting to examine the complexity of gray scale parallel processing operations. Assume a K bit gray scale (for binary images K is 1) and an NxN image. A binary machine having level II complexity would be interconnected on the order of NxNx1. Then a gray scale machine (having K bits of gray scale) of level II complexity would be KxNxN interconnected. The complexity of level III operation is on the

order of (KxNxN)x(KxNxN)xN or (K)(N). For level IV the complexity is of the order of (KxNxN)x(KxNxN)x(KxNxN) or 3 6

(K)(N). Obviously, the costs of implementing a machine rise with its complexity. The cost of debugging, documentation, and maintenance follow a similar increase with increasing complexity.

# 1.2.3 A level IV gray scale machine - 3 address machine

A gray scale picture processor of at least level IV complexity is needed to meet the requirements of the Real Time Picture Processor delineated above. This is the least complex machine that permits full generality. The use of such a level IV machine as a design tool will, we believe, allow the proper selection of some level V functions.

Although a K bit gray scale machine can be simulated using K binary planes, the expression of algorithms is awkward and usually inefficient.

Not surprisingly, a parallel gray scale machine of level IV is beyond the resources of our laboratory. Our solution to the design/maintenance dilemma has been to design a fast serial machine which operates on neighborhoods of rectangularly tessellated gray scale picture arrays. The machine's speed and a felicity in expressing algorithms is achieved partly through the use of triple operand instructions. In this machine a neighborhood has a serial representation.

The following example illustrates serial representation. Let us consider the images I1 and I2 (one of which may be the temporal successor of the other, or they may represent members of a set of serial sections etc). It is desired to find a measure of pattern similarity (in order to spatially or temporally align the images). The problem is solved by finding a measure of pattern similarity between neighborhoods I1 and I2 by computing their product and summing this product into the central pixel of I3. All neighborhoods are 3x3. Neighborhood I1, for example, comprises pixels I1(8) (its central pixel) and boundary pixels I1(0) through I1(7).

1.2

```

The operation to be performed is I3(8) = SUM I1(i) I2(i).

i=0

The neighborhood processor could perform the following sequence of operations:

```

```

Form the products array I3 from I1 and I2.

I3(0) <--I1(0) MUL I2(0) ; product of I1(0), I2(0) into I3(0)

I3(1)<--I1(1) MUL I2(1)

I1(1), I2(1) into I3(1)

I3(2)<--I1(2) MUL I2(2)

: etc.

I3(3)<--I1(3) MUL I2(3)

; naturally there is a way

I3(4)<--I1(4) MUL I2(4)

: to do this with a loop

I3(5) \leftarrow I1(5) MUL I2(5)

: structure

I3(6)<--I1(6) MUL I2(6)

13(7)<--11(7) MUL 12(7)

13(8)<--11(8) MUL 12(8)

Form the sum of the pixels in the 13 neighborhood.

13(8) < --13(8) ADD 13(0)

; sum the pixel product into I3(8)

13(8) < --13(8) ADD 13(1)

I3(8) <-- I3(8) ADD I3(2)

13(8)<--13(8) ADD 13(3)

I3 (8) <-- I3 (8) ADD I3 (4)

13(8)<--13(8) ADD 13(5)

13(8) < --13(8) ADD 13(6)

I3(8) <-- I3(8) ADD I3(7)

; The sum of the entire neighborhood

: product is now in I3(8)

```

These operations, performed over the entire set of corresponding neighborhoods and resulting in the construction of a third image, where the gray value at the point is a measure of the local simillarity of the anticedent images, constitutes a solution to the problem.

These iterative neighborhood operations, prohibitively expensive in time and computer cost on standard machines are to be implemented on the General Picture Processor (GPP). This is the fast serial 3-address component of the RTPP. As will be further detained below, the 3-address machine is closest to the triple operand concept at the base of the mapping: I1oI2-->I3.

# 1.3 The configuration of the RTPP

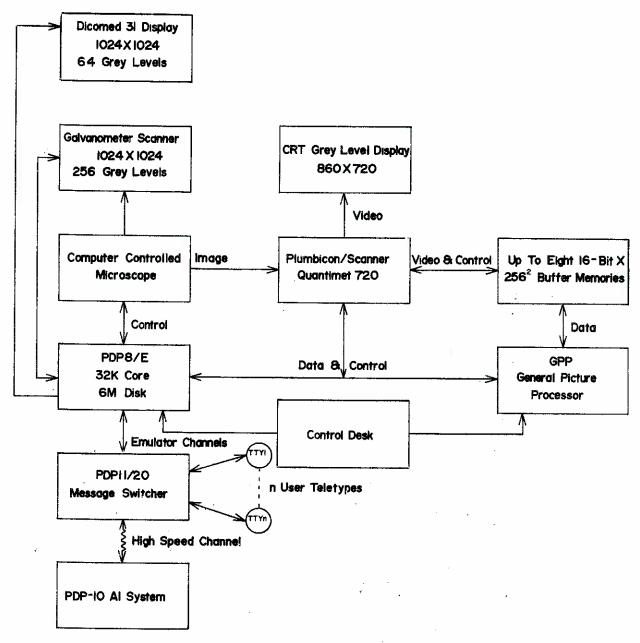

The real time picture processor hardware shown in Figure 2 consists of an Imanco Quantimet 720 (QMT); a Zeiss Axiomat microscope with stepping stage, focus and light source; a galvanometer mirror precision scanner; a Dicomed model 31 64-gray level storage display; up to eight 256x256 16-bit gray level buffer memories (BM); a general picture processor (GPP); a PDP8e computer with 32K core; a four 1.5 million word disk cartridge drives; an interactive control desk shown in Figure 3, and a high speed connection to a PDP10 computer on which the modelling programs are run.

#### 1.3.1 Axiomat microscope

A Zeiss Axiomat microscope is used to supply images to the RTPP system. It has been modified so that the focus and 4:1 zoom knob controls are under computer actuated stepping motor control. In addition, the stage X and Y positions of the slide are moved by computer driven stepping motors. The light illumination subsystem contains variable wavelength interference and variable neutral density filters. These two functions are implemented by use of continuous rotary wedge filters which are controlled by the computer via high speed stepping motors. Currently, a Quantimet plumbicon or vidicon scanner and a precision galvanometer mirror scanner are interfaced to output ports of the Axiomat. There is an additional viewing port within the viewer's reach. Thus there are three image planes accessable simultaneously.

# 1.3.2 Video input and output devices

The video input, display, and certain image processing functions can be performed by various I/O devices connected to the multiple output ports of a Zeiss Axiomat Microscope.

A Quantimet 720 image analyzer has been incorporated into the RTPP. The plumbicon camera video is digitized to 8-bits for sampling by the system (at a 8 MHz rate) and is then reconverted to an analogue signal for reinsertion into the Quantimet video input chain. The Quantimet includes a 10.1 frame/second television display and some minimal feature extraction and measurement hardware to be discussed below.

A precision galvanometer mirror scanner with a 1024x1024 pixel random access window and 256 gray level video output can also be used as a digitizing input device to the RTPP from the microscope. The PDP8e may route mirror scanner data to a buffer memory for display on the Quantimet or further processing by the RTPP. In addition, a Dicomed model 31

1024x1024 picture point 64-gray level precision storage display may also be used as a storage output device in the RTPP. Presently, hardcopy images from the system are produced by photographing the Dicomed display.

The Quantimet is the preferred I/O device for real time interaction because of its rapid frame rate. The digitized picture from the plumbicon scanner video is a 256 (64 usable) gray level digitized image within a 880x680 pixel window. QMT display may also be used to post images from buffer memory windows inserted within original scanner image data. There are two types of cameras: a plumbicon and a vidicon. The plumbicon linearity for use with densitometry while the qives better vidicon has a larger dynamic light input range. When one these cameras is used on the Axiomat at the same time the galvanometer scanner is used the difference in dynamic range of light intensities required is a problem. This is solved by putting N.D. filters in front of the TV camera. In addition, shutter protection circuit is used to turn off the image when no TV scanning is being done or if the light level into the camera is too great.

#### 1.3.3 Buffer memories - BM

Although a histologic slide can be used as a random access read only memory, it is inadequate for use in processing the information it contains. It is necessary to retain images and their transforms in buffer memories, and to be able to access them and display them rapidly. In order to do this our Real Time Picture Processor needs facilities to store at least four entire images or transforms at once (e.g. to store a Fourier transform and a Fourier filter takes 4 images - 2 real and 2 imaginary), and the ability to access part of them very quickly. This rapid pixel accessing is the primary reason for the use of buffer memories.

Our approach has been to design buffer memories each of which can contain a reasonable size of working image (256x256 pixels). At a nominal maximum optical resolution of about 0.25 microns, a biologically usable picture window is approximately 50 microns or more corresponding to about 200 pixels. The RTPP uses a 256x256 pixel window.

Eight 256x256-word 16-bit/word gray scale buffer memories are being built which may be accessed by either the Quantimet video scanner/display, the GPP (general picture processor), or the PDP8e computer. Each buffer memory holds two 8-bit gray scale images, one in the low and one in the high half of the 16-bit BM word. When a BM is not reading or writing data to the GPP, it can be used to continuously recycle a picture for posting on the Quantimet display and/or as input to the Quantimet video-input chain using a fast 8-bit digital to analog converter. The PDP8e controls the scanning (into) and the posting of images (from) the buffer memories. In addition, the PDP8e computer can read/write data from/to buffer

memories using rapid direct memory access (DMA) techniques. The BM can also be used as a binary data mask for Quantimet or other BM data.

A BM can acquire a selected 256x256 window of a QMT scanner image or an image loaded from the PDP8e. This image can then be accessed pixel by pixel or line by line from the GPP or PDP8e. Its contents may also be posted on the Quantimet display (using a fast D/A and digitized video multiplexing). When used in this mode, the QMT is able to process synthesized video. Using a direct memory access (DMA) channel, the PDP8e can then access the buffer memories. The GPP also can directly access the buffer memories for performing transformations on the image.

The buffer memories are organized so that it is most economical to transfer entire horizontal lines of data between them and the GPP processing unit. Vertical lines or randomly accessed pixels can also be transferred but at only 1/4 the data rate.

# 1.3.4 Triple line buffers for image addressing

Given the basic architecture of the GPP, an addressing mode to implement the fast triple operand processing is needed. It was decided that the NxN neighborhood should be directly addressable for all I1(i), I2(j) and I3(k) in the three current NxN neighborhoods (i,j,k), letting the neighborhood be tessilated through the entire image.

The NxN selected is a 3x3 neighborhood because of the combinatorial constraints which increase intolerably rapidly for any larger neighborhood. Three NxN neighborhoods are required for the images I1, I2 and I3; therefore 27 directly addressable pixels are needed for N=3. Forty-eight and 75 directly addressable pixels would be needed for N=4 and N=5 respectively. For any size N one could argue that some algorithm would need N+1. Since a 3x3 neighborhood is the minimum size that intrinsically handles 4 and 8 neighborhood processing (a symmetrical central pixel), at least a minimum of processing power exists with this size. If necessary N+1 can be simulated in software for any N. Therefore, it was decided to hold down the complexity of the hardware and let N=3.

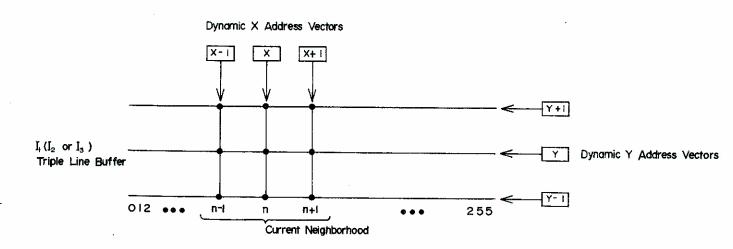

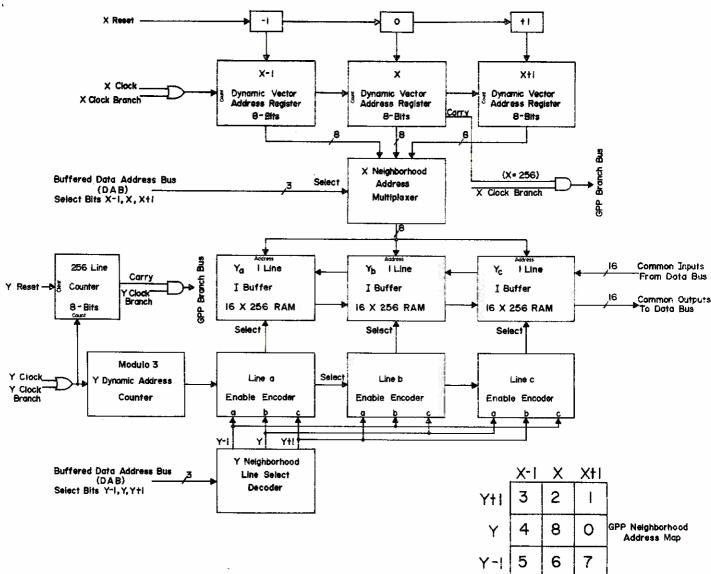

Finally, to make an entire neighborhood directly addressable, the processor has three line-buffers, each capable of holding N entire lines of image data (N=3). Figure 1 illustrates an N-line buffer with K-bits/pixel and M pixels/line. In this design (N,K,M) = (3,16,256). Three triple line buffers are implemented.

The processor can transfer an entire line at a time either between a buffer memory and the line buffer or vice versa. The line buffers, being implemented with fast registers, constitute a kind of cache memory (a special type of

hardware used to optimize data rates between a processor and its main data memory).

The problem of addressing a neighborhood is reduced to of addressing the line-buffers. neighborhood processing of an entire image can be accomplished by a sequence of actions: first, processing is done on each current neighborhood of an 3-line-deep Then a processed line (usually the oldest) is 3-pixel-wide line-buffer. moved out of the line-buffer to a buffer memory and a new line, usually the next line in the raster source image, replaces it. The processing loop is then repeated, until the entire image has been processed. Three line buffers, providing 8 neighbor processing, maintain the full generality of level operations. A more complete description of the hardware is given later in this document.

|     | X-I | X    | X+I  |      |           |       |

|-----|-----|------|------|------|-----------|-------|

| Y+I | 3   | 2    | 1    |      |           |       |

| Y   | 4   | 8    | 0    |      |           |       |

| Y-1 | 5   | 6    | 7    |      |           |       |

| •   | GPP | Neiç | hbor | hood | Addressin | у Мар |

Figure 1. GPP triple line buffer addressing

Associated with each line buffer is a set of three X and one Y dynamic address vectors. These dynamic address vectors define the current 3x3 neighborhood pixels in the line buffer. Therefore tessellation through different neighborhoods is easily performed by changing these address vectors. An instruction is available to selectively increment or decrement (X-1,X,X+1) in I1, I2, and I3 at one time thus effectively moving the current neighborhood to the left or right respectively.

Figure 2. Block diagram of RTPP

The PDP8e computer directs the microscope stage to positions determined either manually by the operator or automatically by the PDP10 system. Images may be acquired by the buffer memories for processing by the GPP. Raw images as well as processed images may be displayed on the Quantimet 720. Precision scanning and display are implemented by the galvanometer mirror scanner and Dicomed display respectively. The user may interact with the system either through a control desk or a teletype.

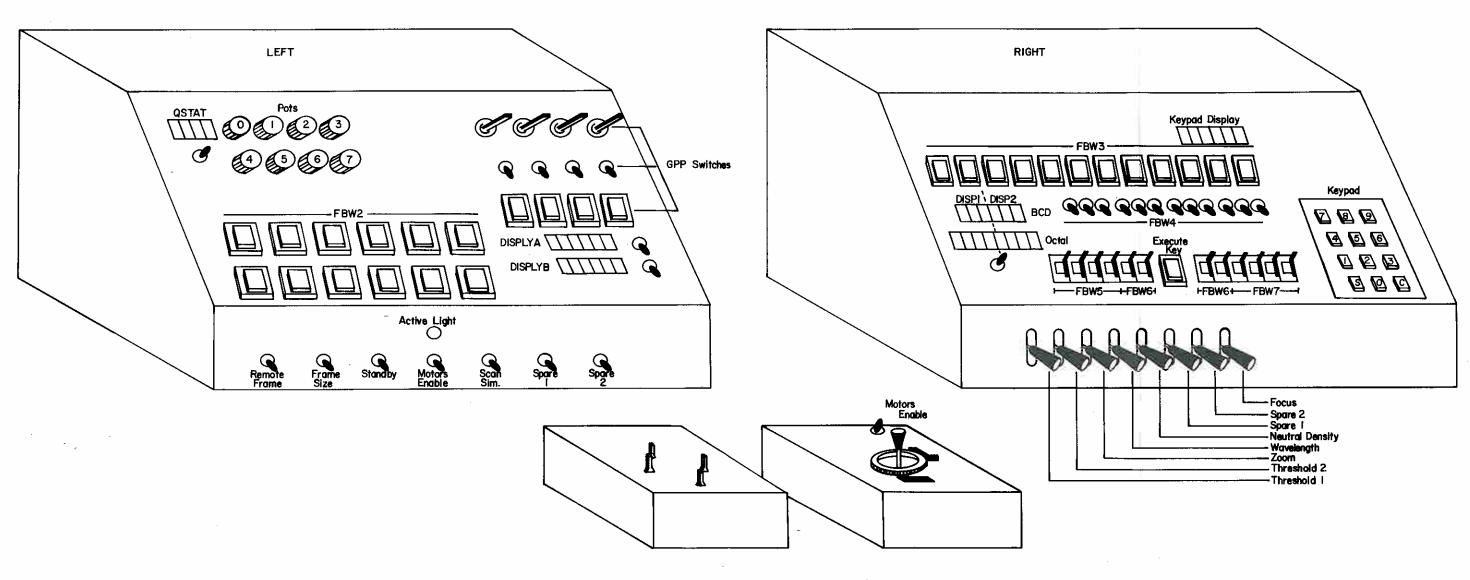

#### Figure 3. Interactive control desk

The RTPP interactive control desk is situated next to the RTPP with Quantimet video display to the rear of the control desk and the Axiomat microscope off to the side. A Graf-Pen spark tablet is located immediately in front of the operator with the pushbuttons and lights mounted in two large boxes to the left and right. The remote Quantimet variable frame and scale keys are located in a small box with a movable cable as is joystick for the Zeiss Axiomat (x,y) stepping stage. latter has a long cable and may be used at the microscope for control of the stage while viewing thru the eyepiece of the microscope. control desk controls are listed as follows going from left to right and top to bottom (for the left box first): the QSTAT lights indicate the status of the Quantimet interface; the pots are connected to A/D channels in both the PDP8e and the GPP; the GPP switches are read by the SWITCHA register; FBW2 are lighted "command" keys for the PDP8e; DISPLA/B are GPP display registers. the remove frame switch enables the remove frame and scale switches even when the PDP8e has not enabled them; the frame size switch freezes the frame and scale sizes so that a frame of fixed size may be moved around; the standby switch places the Quantimet display and system control in standby mode; the motors enable switch (also in joystick box) enables the stepping motors when the light above it is on; the scan simulation switch moves the galvanometer scanner independently of the PDP8e so that the gain/baseline controls may be setup with using the PDP8e. For the right control box, the controls are: keypad display of keypad input for the PDP8e; FBW3 "classification" keys for the PDP8e; DISP1/2 PDP8e display lights which are decoded as BCD in the top lights and as octal in the bottom lights; FBW4 PDP8e toggle switches; keypad to input 6 BCD digits to the PDP8e; FBW5/6/7 PDP8e octal digiswitches: Execute key used to execute (interpretively by the PDP8e) instructions given in the digiswitches; eight 5-position spring loaded toggle switches control various stepping motors with a fast and slow speed in both forward and reverse directions.

Remote Variable Frame and Scale Keys

Zeiss Stage X, Y Joystick Control

# 1.3.5 General Picture Processor

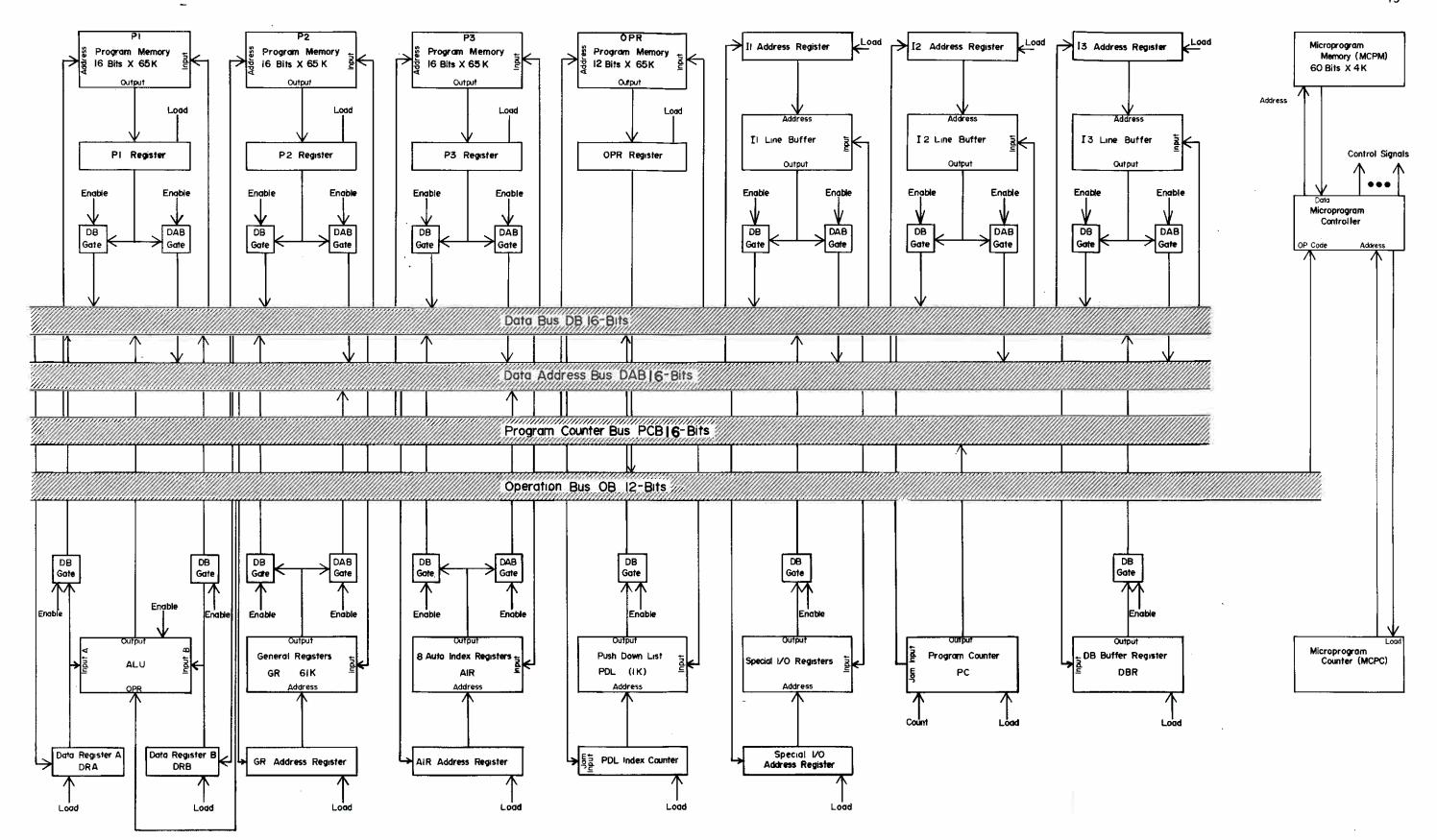

The General Picture Processor (GPP) is a stored program very fast serial processor which can rapidly access and process image data through current picture neighborhoods. It uses the concept of triple operand instructions on up to 3 different current neighborhoods. These current neighborhoods may be taken from three diffent triple line cache memory buffers which in turn are backed by the slower buffer memories.

The programs which the GPP executes are loaded into a GPP program memory (PM) by the PDP8e which controls the GPP as a peripheral device. The GPP programs will be written and compiled on the the PDP10 system and assembled on the PDP8e. The PDP8e interacting with the PDP10 will be able to load the binary compilation files into the GPP or to save (get) these files on its own local disk for later use.

The PDP10 system, which is described subsequently in other documents ([Lem76b], [Lem76c], [Lem76d]), and in sections (1.4-1.5,1.7) is written in PDP10 SAIL [Van173] language. It consists of a high level procedural description language PRDL which will be used interactively to build morphological descriptions of biological images. PRDL will cause the low level picture processing functions to be evaluated on the RTPP rather than on the PDP10. An image processing program PROC10 [Lem76d] is currently being used on the PDP10 to emulate various image processing procedures which could run on the RTPP. Various often called procedures such as fetching a picture neighborhood have been shown PROC10) to be useful image processing primitive operations which are time consuming using normal PDP10 instructions. such operations are committed to GPP hardware instructions (both through actual hardware and through microprogram implementation).

Running RTPP programs will be accomplished by having PRDL functions for the RTPP be compiled by the MAINSAIL cross-compiler [Wil75] on the PDP10. The output of MAINSAIL is then sent to the PDP8e where it is assembled by the RTPP assembler GPPASM [Gros76a] on the PDP8e. Thus PRDL functions which run on the RTPP can be constructed and later be called by PRDL through the RTPP monitor DDTG [Lem76a] (see section 1.6). The communication between these various processors must be intimate and the ultimate responsibility for insuring this lies with the PRDL system.

# 1.3.6 Quantimet controller

The interface between the Quantimet and the PDP8e consists of an interface to "program" the Quantimet (e.g. use thresholded video (by some criteria) to measure the total area); acquire QMT data; display numbers on the right QMT number display; load various QMT detector threshold and sizing limit registers and "live frame" frame and scale window coordinates.

In addition, special hardware is used to acquire a set of 2-properties/object for all objects in the scene (up to 1024 objects). The properties are taken from the set of object features computed by the intrinsic Quantimet Function Computer modules. These properties include: integrated density, area, perimeter, horizontal and vertial projections, and horizontal and vertical ferets. This acquisition is accomplished during a single scan of 0.1 second. The additional hardware constructed by us includes, a 1024 datum deep stack of the bottom most end points of blobs called Anti-Cooincidence-Points (X-ACP, Y-ACP); a stack of 1 bit/word detector-bit of the associated detected level; and a associated dual data stack which accepts two QMT data words from the function computers of 6 BCD digits each.

At the occurence of each ACP (which corresponds to the recognition of a discrete blob) all the above stacks have data pushed into them. The PDP8e can unload the data after it has been acquired by the Quantimet. In addition, data can be pushed on matching the (X,Y) coordinates of the QMT with those of the front of the (X-ACP, Y-ACP) stack. Since the ACP stack may be loaded by the PDP8e, this offers further possibilities for data acquisition by measuring the detection at the coordinates of the synthetic ACPs.

Other Quantimet related hardware includes a specially constructed Mask register for acquiring and, storing and using arbitrary convex shapes and a programmable display cursor. Both of these devices are described in more detail in Section 2.

### 1.3.7 Control of the RTPP by the PDP8e

The RTPP complex, (Figure 2), under control from the PDP8e minicomputer, may position the active microscope elements (eg. focus, stage, zoom, etc) and adjust the live frame image of the Quantimet according to program requirements or in response to the operator's directions at the control desk. The PDP8e has full control over the Quantimet to program it and acquire single data scans. Live frame video (within specified 256x256 windows) may be stored in any or all eight buffer memories, and displayed on the Quantimet at the direction of the PDP8e. To process image data in the buffer memories, the

PDP8e loads a specific program into the instruction memory of the GPP and initiates execution. Results may be passed back to the PDP8e for storage or transfer to other computers, or displayed on the Quantimet, or both.

# 1.4 The RTPP as a picture processing peripheral

The RTPP is really a specialized peripheral processor, a level of complexity beyond the now accepted class of display controllers. The latter usually consists of a programmable special purpose computer with a moderate amount of memory and a digital image display. The display controller is intended to remove from its large general purpose host computer a large portion of the burden of interactive display programs. In terms of the host computer and its associated facilities there can be little doubt that such a solution to the display problem is usually economically and computationally justified.

It may be noted that the RTPP, as a picture processing peripheral, removes a proportionately greater burden from the host computer's CPU and core memory than does the display controller. There is no need now to devote as much channel capacity for the transmission of raw picture data and their transforms. Instead, a system of distributed computing, made possible by the RTPP, allows the exchange of higher level data such as property lists, effectively resulting in marked information compression. This in turn allows more effective use of a wide range of facilities available on the general purpose host computer.

RTPP output would usually be images and/or lists of properties of objects contained in the images. The major component of the RTPP real time interaction is the General Picture Processor (GPP). This hardware processor allows extremely rapid serial digital processing of digitized gray scale images using special purpose hardware including image buffer memories and fast addressing schemes. Because the GPP/image buffer memories handle gray scale data (not merely binary black and white images) a larger set of useful picture functions can be quickly designed and executed than with a strictly binary image processor.

## 1.5 Cell Modeling System - CELMOD

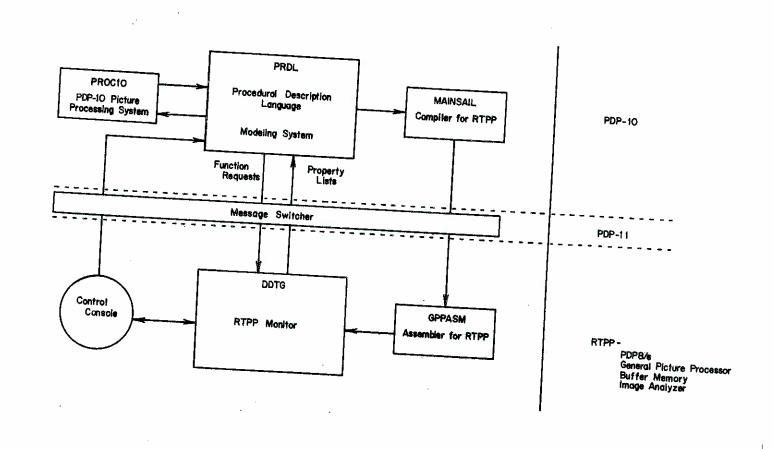

A biological cell relational data modeling system will analyze the scene using RTPP generated picture primitives as in ([Lem72], [ShapB74]) and involves the use of procedural definition on a semantic data base. This modelling system is called CELMOD [Lem76c]. It consists of the three PDP10 programs (PRDL [Lem76b], PROC10 [Lem76c] and MAINSAIL [Wi175]) and the RTPP. A block diagram of CELMOD is given in Figure 4.

define what he means by a particular class of cells and manipulate properties and relations of objects in the images. The biologist by means of iterative composition of processes can build up explicit connections between his semantic information and the image information represented at the individual pixel level. Being an interactive system, it will be easier for him to elicit the subconscious clues that he uses in making these decisions.

The decription language is called the Procedural Description Language (PRDL) which runs on a PDP10 and is described in [Lem76b]. The RTPP will thus also serve as a feature extractor for PRDL. Figure 4 shows a block diagram of the CELMOD system. The overall connection between the RTPP and PRDL is described in more detail in [Lem76b].

The CELMOD system will be able to perform image processing operations on the PDP10 using PROC10 while the RTPP is being constructed.

Figure 4. CELMOD system block diagram

CELMOD is composed of two major software systems running on different machines. The PRDL program runs on a DECSYSTEM-10 and is used to model cell images assuming the features are extracted. The RTPP has a resident monitor called DDTG which executes functions requested by the PRDL system and returns feature lists. The user sits at the RTPP control desk communicates with PRDL through a GT40 line graphics-teletype video terminal. The microscope data are visible on the RTPP display. The switcher which is an operationally invisible high speed link between the two systems.

# 1.6 DDTG - the RTPP debugger/monitor

DDTG [Lem76a], a monitor/debugger is constructed for user and/or computer control of the RTPP. Functionally, DDTG is more than a simple combination of monitor and debugging facilities. As the RTPP operating system, it is required to interpret direct (i.e. via control console) user commands, a string of commands generated by user-PDP10 interaction. In addition, it is required to provide access and control machine language word level) of major memory structures (PDP8e core, GPP program memory, GPP general register memory (GR) buffer memories ). It provides full control for a variety of image acquisition and low level analytic peripheral devices Axiomat microscope stage, focus, etc. the Quantimet 720 and a variety of its plug in modules, a special mirror scanner, a sonic tablet, and a rapid scan spectrometer). Display control functions of DDTG also include the Dicomed and Quantimet displays.

DDTG has the ability to store, retrieve and execute (from PDP8e disks) PDP8e and/or GPP programs (user or PDP10 generated) (cf. Figure 4). Since in stand alone mode, DDTG is to be used as much by biologists as by computer scientists, the user interface allows many high level and seeming English command constructs. This in turn permits easy construction of understandable control programs for stand alone use, exploration and debugging at a very high level.

DDTG, written in standard PDP8e FortranII-Sabr consists of 4 major parts: an interpreter, parser, symbol table, and a large set of worker routines. The last include such features as loaders for the various component computers of the RTPP, as well as extensive and flexible disk I/O routines, a wide variety of stylized data structures.

DDTG has capabilities which allow it to load and run programs in the RTPP and to monitor their activity. An extensive set of commands are implemented to facilitate image data acquisition and display, and the running of small picture operation programs called "special segments". The General Picture Processor (GPP) portion of the RTPP will, in performing picture operations, require special segment support from DDTG. In addition, mechanisms are available for RTPP program interaction with OS/8 in order to facilitate the implementation of image processing programs (exclusive of DDTG) to process DDTG produced data.

# 1.7 RTPP Compiler/Assembler - MAINSAIL/GPPASM

The RTPP will have access to a very powerful cross-compiler MAINSAIL [Wil75] and a low leve assembler GPPASM [Gros76]. MAINSAIL will run on the PDP10 and compile a dialect of PDP10 SAIL which includes teletype I/O and records but not LEAP or file structured I/O. As the initial RTPP has no

floating point hardware, the initial MAINSAIL to be used has no real arithmetic constructs. Registers (such as line buffers Ij(k)) will be represented as reserved symbols (Ijk). MAINSAIL will output assembly language source code for GPPASM.

GPPASM is a low level assembler which produces non-relocatable load modules. It has labels and limited arithmetic capabilities as it was designed to run efficiently on a PDP8e. This last aspect is important for the debugging and maintenance of the RTPP. The GPPLDR which loads the absolute binary files produced by GPPASM is part of DDTG. GPPASM permits the use of REQUIRE <file> LOAD or SOURCE statements and thus a run time library can be assembled or loaded with main programs.

The GPPASM grammar was designed to be easily parsed by a simple finite state acceptor with a small auxillary stack. The assembler has either 2 or 3 passes depending on whether an assembly listing file is to be generated. The first pass incorporates declaration, PM and GR label resolution; the 2nd pass generates the PM and GR output code segments while the 3rd pass optionally generates an assembly listing. The PDP8e special (PAL8) segment is stripped out during the 1st pass and is later assembled by a modified version of PAL8 and concatinated with the PM and GR segments. The GPPLDR in DDTG is able to analyze and load such GPP binary load files. The BNF grammar for the GPPASM assembly language is given in Appendix E.

# 1.8 GPP Microprogram Assembler - MICROP

The actual GPP implementation employs microprogram control. The microprogram is stored in a 60-bitx4K RAM by the PDP8e. Microprograms are assembled on the PDP8e using the MICROP assembler [Gros76b]. The microassembler is discussed in more detail in Section 6.1.1.

#### SECTION 2

#### Quantimet subsystem

The Quantimet 720 [Fish71] is a modular low level image processor which is used primarily as an I/O device rather than as an stand alone image processor. In addition to the basic scanner and display modules of the QMT, other hardware modules are used to accomplish elementary functions such as object area as determined by thresholded detected video: perimeter, number of objects in a field, integrated density under a mask, and several intercept properties. The Quantimet functions are controlled and programmed by the PDP8e minicomputer or may be used as a stand alone device.

The Quantimet part of the Real Time Picture Processor consists of the following Imanco Quantimet 720 modules:

Plumbicon (or vidicon) non-interlaced TV raster scanner

System Control module

System Display module

Variable Frame and Scale module

Standard Detector module

Digitizer/Densitometer module

1-Dimensional detector module

Amender module

Standard Computer module

MS3 Computer module

2 Function Computer modules (with Density option)

Light pen module

Classifier Collector module

The Classifier Collector module is added primarily for maintenance of the Function Computer modules.

#### 2.1 Quantimet modules

The basic functions of these modules are enumerated here as an aid in understanding the design of the real time

picture processor system. For further details see [Fish71]. The basic design for some of the Quantimet modifications was done initially for the NCI Grain Counter-I [LipL74].

# 2.1.1 Scanner - System Control module

The TV scanner (either a Plumbicon or vidicon camera) and system control produce a 10.1/second 880x720 digitally derived TV image. Actually, a smaller window is used which is called the big frame consisting of 860x680 lines. Inside the big frame is still a smaller frame called the live frame. Data inside the live frame is the data which is used by the rest of the Quantimet. The live frame is derived from many sources, some of which are the variable frame and scale, detected video, light pen mask output, buffer memory derived detected video and computed video of the various modules.

The TV camera is physically connected to the Zeiss Axiomat microscope through an IPU designed and constructed mechanical interface. This interface includes a Zeiss electromechanical shutter which is closed either by the computer (which can also open it) or by an automatic shut-off circuit which senses too much light entering the Quantimet camera. This latter feature prevents camera damage with too much light. The interface also has room for several neutral density filters so that the light levels can be balanced for running both the galvanometer scanner and the Quantimet camera at the same time.

#### 2.1.2 System display module

The system display module is used to mix the system input video with the output display signals from the Standard computer, MS3 computer, Amender, Frame and Scale, 1-D detector, Digitizing detector, Function computers, Classifier Collector, and light pen modules. These display signals will either fully intensify or partially blank the system display. This mixed video signal is then displayed on a 10.1 rasters/second orange phosphor TV monitor. This phosphor is designed for slow decay times to reduce flicker. However, it does so at cost to the gray scale resolution.

The RTPP will be able to blank out the scanner video and substitute synthesized video in its place inside of buffer memory 256x256 pixel windows. This is discussed in more detail in Section 3 on the buffer memories. The Quantimet display cursor and mask register displays are added to the Quantimet display inputs (Scale mixer knob and Guard mixer knobs respectively).

# 2.1.3 Variable Frame and Scale module

The Variable Frame and Scale module generates a live Variable Frame by generating a rectangular computing window specified by (hor-position, hor-size, vert-position, vert-size). When in variable frame mode, any data inside this window will be enabled for detection by the Quantimet hardware; otherwise detection takes place within the standard live frame.

# 2.1.4 Detector modules

There are three detector modules: the Digitizer/Densitometer, the 1-D detector and the Standard detector modules. The Digitizer can be used as a detector (high speed comparator) to transform the analog video into a detected/not-detected digital signal according to the selected threshold values. The 1-D detector performs auto thresholding in 1 dimension (X-axis) to detect objects in a background phase. The Standard detector performs simple thresholding. The Digitizer and 1D detectors have a 64 gray level range while the Standard Detector maps up the white to black range into 4096 divisions. The thresholds in the Digitizer/detector and Standard Detector have been modified so as to be able to be loaded by the PDP8e.

# 2.1.5 Light pen

The light pen module will generate a mask of a detected object selected with the light pen. There is a restriction that the object be vertically convex so as to generate the complete mask.

# 2.1.6 Digitizer/densitometer

The Digitizer/densitometer also functions as a densitometer. It integrates detected gray scale data in the range of [0:63]. It does this by using a fast 125 nanosecond A/D converter and taking an optional log of the signal. It gives relative density directly. Using this module one can perform densitometry when suitably calibrated.

#### 2.1.7 MS3 Computer

The MS3 computer module uses the detected video from the detector modules to compute global area, perimeter, intercept and count. The "pattern recognition" mode of operation activates two Function computer modules for acquiring object specific data.

### 2.1.8 Function Computer module

The Function computer computes for each detected object area, integrated gray-value or log-gray-value, perimeter, vertical projection, horizontal projection, horizontal feret, and vertical feret. An object is marked by the occurance of its anti-coincidence point (ACP). Data is not acquired for partially represented objects (in which the ACP falls outside of the live frame).

# 2.1.9 Classifier Collector module

A Classifier Collector module may be used to accept 2 Function Computer module outputs for stand alone operation. It is also able to compare function values from the function computer output against a range of values to determine whether the ACP (object label) should be used.

# 2.1.10 Standard Computer module

The Standard Computer module is similar to the MS3 Computer except that it does not compute perimeter and has no pattern recognition mode.

### 2.2 Microprogramming QMT modules

Many of the QMT modules mentioned above may be microprogrammed to select either modes of operation for functions to compute. This is done by enabling a rear status register on each of the modules called the "programmer" input. On the RTPP this is done by loading, for each QMT scan, a program word which consists of eight 12-bit status words called the Quantimet Program registers denoted QPROG1 through QPROG8. These registers and their allocation in the Quantimet subsystem is discussed in Appendix C.3.

# 2.3 PDP8e control of the Quantimet

The Quantimet may be controlled by the PDP8e in a single step data acquistion mode. When the System Control module 'Continuous/Auto' switch is put in 'Auto', it is placed under control of the PDP8e. Essentially, PDP8e control is effected by manipulation of the eight 12-bit static programming words and the QSTAT status register. The PDP8e STQMT instruction will start the Quantimet data acquistion when the Quantimet scanner reaches the start (top) of the next scan frame. The QMSKP skip instruction can be used to test when the data acquisition is done. At this time, the whole field Quantimet data is available to the PDP8e in the QDAT1, QDAT2, and QDAT3 input instructions which will read 7 BCD digits (LSD to MSD) into the PDP8e accumulator. This whole field data is displayed automatically in the left Quantimet display. The right Quantimet display may be loaded by the PDP8e load instructions LQDT1, LQDT2 and LQDT1 (MSD to LSD).

Function computer data as well as ACP (x,y) coordinates may be acquired in a single Quantimet scan through a 1024 word (69-bits/word) shift register. This is described in more detail in Appendix C.1.2.

# 2.3.1 Quantimet status register - QSTAT

A status register QSTAT controls operation of the Quantimet/PDP8e interface and various options on the Quantimet. This control includes enabling the Frame and Scale control desk switches, shift register data acquistion system for Function Computer data, standby and camera shutter activation. These are discussed in Appendix C.1.7.

### 2.4 The mask register module

Detected video is used to generate a 720 picture line Quantimet mask of entry and exit line intercept positions stored in a hardware Mask register. This Mask register can be used to supply the QMT with a detection region mask by reading the mask as the QMT goes through a scan. The mask register is a (1024 word) RAM which is loaded either from with the QMT detected video on a command from the PDP8e (GETMSK) or from the PDP8e directly. On the PDP8e issuing the GETMSK instruction, detected video is used to determine "DET-ENTRY" and "DET-EXIT" for the entire QMT live frame.

When the mask register is not being loaded, it cycles with the QMT and outputs a (QPROG selected) mask of either variable frame, mask or various logical comginations of variable frame and mask (see QPROG2[0:3]). The QPROG2 selected mask display intensity is controlled by the display "guard" knob. A display of the Mask register output alone (without the

frame and scale) is also available and is selected by QPROG7[0:1]. The display intensity for this display is controlled by the display "scale and figures" knob.

The addressing in the mask register is the same as that of the frame and scale window. The QMT VTRIG. SYNC, (HTRIG), signals are used to generate the actual addresses. The entrance/exit acquisition algorithm works as follows. detected video first goes true (enter a solid blob) the "X" coordinate at the Y'th line inside the frame is entered into the Y'th (0 to 719) "DET-ENTER" of the mask register. When the detected video first goes false again (leaving a blob), the "DET-EXIT" "X" coordinate is entered for the Y'th line. default a line's "DET-ENTER" when "getting" a mask is assumed to , be 1023 before a line is processed. This takes care of the case where no data or only entry data is present. that only the first object in a line is detected and that objects with concave inward tops or bottoms will not be acquired properly because horizontal slices of such objects have multiple entrance/exit points.

The mask register can be loaded or read from the PDP8e. The main use of the mask register would be in masking QMT data with synthesized masks or in accessing actual perimeter X-Y coordinates.

Control of the mask register from the PDP8e is done with the GETMSK, MSKADR, RMASKE, RMASKX, LMASKE, and LMASKX PDP8e instructions. GETMSK enables the acquiring the next QMT detected video mask into the mask register. Now doing a STQMT command starts the actual mask acquisition from the input detected video. MSKADR loads the line number for subsequent I/O. Then RMASK- and LMASK- do I/O on that MSKADR's entrance/exit pixels.

Note that RMASK- and LMASK- are allowed at any time except during mask acqusition. the mask generated for an object will be a fairly good approximation to its boundry given that the object has no concave upward or downward regions. The following OS8 Fortran II program will get a mask from the detected video inside the current frame and save it in the PDP8e memory.

```

DIMENSION IENTER (720), IEXIT (720)

S

GETMSK /enable a mask to be accessed

S

STQMT /start mask acquisition

S NOTDONE,

OMSKP

S

JMP NOTDONE

DO 100 I = 1,720

S

TAD

I

S

MSKADR

S

RMASKE

S

DCA JENTER

S

RMASKX

S

DC A

JEXIT

IENTER (I) = JENTER

100

IEXIT(I)=JEXIT

```

## 2.5 QMT cursor

An X-Y cursor is available which can be loaded from the PDP8e using the same coordinate system as the Frame and Scale and mask register devices. It appears as a 10 pixels line segment to the right on the actual (x,y) position on the "scale" display control. It is programmed in DDTG software to be used with the Graf-Pen to track the pen on the QMT screen whether the pen is actually using the data or not. To make the cursor disappear, load XP or YP. The PDP8e commands LDXP and LDYP load a binary coordinate pair into the cursor controller. The cursor display intensity on the Quantimet display is controlled by the "scale and figures" knob.

#### SECTION 3

## Buffer memory

The RTPP is designed to use up to eight gray scale buffer memories (BM). The memories may be simultaneously selected by the PDP8e for posting of images (displaying on the Quantimet display) or acquiring QMT scanner data. However, there is a restriction that no two active BM windows can intersect during display or scanning as data will be lost from one of the memories.

A BM consists of 65K (256x256 pixels) 16-bit/words with gray scale data being stored in both the high and low 8-bit bytes of a 16-bit word. Binary detected video images are stored as signed 8-bit bytes. Since each BM is synchronized with the QMT independently, up to 512 X 1024 pixels "could" be posted in real-time (if the Quantimet display were large enough). Usually, a 256x256 window will be displayed and the other BMs may contain variants of that displayed window. One may select the high or low 8-bit bytes in a given buffer memory. Each 8-bit slice may then be used to store separate images or alternatively, for example the high and low 8-bit fields may be used to store the real and immaginary portions of a Fourier transform.

### Synthesized Quantimet video

The QMT video (level adjusted by the system control module) is digitized using the fast A/D converter to 8 bits (using 8-bits of the 9-bit Computer Labs model 7910 10MHZ A/D). This digitized image is them multiplexed digitally with the buffer memory data to be synthesized as Quantimet input video - that is substituting buffer memory data for Quantimet TV scanner data. The digitized video is then resynthesized using a fast D/A converter (Computer Labs RDA-0815A, 15 MHZ).

Synthesized video, selected for display posting, is substituted in the window (Quantimet active frame) [[XB:XB+255],[YB:YB+255]] for the QMT scanner video input to the rest of the QMT. This results from our modification of the video train which allows the QMT to process synthesized video!

In order to synthesize QMT video, the BM first synchronizes with the QMT. That is, it waits until the QMT reaches the (XB,YB) pixel and then starts dumping 256 pixels into the digital video multiplexer. This digitized video is then converted with a fast D/A to analogue video for Quantimet video input. Successive lines are then synchronized similarly.

#### GPP use of BMs

The GPP can perform I/O with the BMs. That is, BMs are used for storing and retrieving intermediate pictures while

doing picture processing. This is done synchronously by line after the line's row or column address is specified by the GPP LINE instruction. The GPP can also random access the BM in single word or neighborhood mode.

It is possible for two different devices to access two different BM's simultaneously under certain conditions. The eight BMs are divided into parallel memory systems (group A - BMs 0 to 3, and group B - BMs 4 to 7). Provided each device access is to a different group of 4 memories then parallel access is possible. The BM access priorities from highest to lowest are: BM input from QMT scanner, GPP I/O, PDP8e I/O, BM posting on the QMT display.

If two devices require I/O on the same BM group memories simultaneously, then the highest priority device obtains access. For example, if the GPP requests I/O during a posting on the QMT sequence, then the "would be" BM posted data becomes the actual QMT scanner data. If the scanner data were a dark object then the resulting posted image would have light holes in it representing a higher priority access conflict.

# BM scan and display selection

Two types of images may be acquired: 8-bit grayscale and binary images. Binary images are stored in the buffer memories as signed 8-bit bytes. Images are stored and used by selecting a high or low byte to be accessed. PDP8e commands GETA, GETB, POSTA, and POSTB perform these control functions.

They all load 12-bit command registers (from the PDP8e AC) which selects which byte to use, which buffer memories to enable, and whether to perform gray scale or binary (leading bit of a byte) I/O. The actual scan is started with the STQMT operation. The command register format (the same for all four GET-/POST- instructions) is as follows:

- [0:3] (0) use low byte for pix, high byte for binary mask

(1) use high byte for pix, low byte for binary mask

- [4:7] (0) use gray scale data

(1) use binary mask data

- [8:11] (0) don't select a BM (1) select a BM

## BM window and scan acquisition

A buffer memory can accept a 256 X 256 x 8-bit gray scale image from the Quantimet video (digitized via Computer Labs 8-bit A/D) starting at the upper left hand corner coordinates denoted (XB,YB). This is done in less than one QMT scan cycle of 0.1 second. During this time the BM group is unavailiable to both the GPP and the synthesized video generator But other BM I/O operations, GPP or PDP8e I/O, may take place. The lesser priority operation will be disconnected

only during the part of the horizontal scan line that the BM recieves data from the QMT. All other lines in that BM group during this 'GET' function are available for lower priority I/O except posting.

At the end of acquiring the QMT image, the BM is disconnected from the digitizing video channel. During a scan, the BM accepts 256 sequential pixels/line starting at the X coordinate XB of each line for each of 256 lines beginning with line YB. The BM window so defined is determined by comparing (XB,YB) with the real-time (xreal,yreal) coordinates. Each BM has a pair of window coordinates (XB(i), YB(i)) which may be loaded by the PDP8e. The eight window coordinate pairs are loaded from the PDP8e by the commands (BMXi,BMYi) where i=[0:7].

In addition, the detected Quantimet video may be acquired as a binary mask into buffer memories using the GETA/B command with the appropriate bits [4:7] set. It may be inserted into the Quantimet frame input using the POSTA/B instruction with the appropriate bits [4:7] set. The resulting mask may be used for further Quantimet data acquistion.

It should be noted to avoid confusion that BM window positions are independent of the frame and scale window position.

# PDP8e accessing of BM data

The PDP8e can transfer up to 4K PDP8e 12-bit words using direct memory accessing (DMA) to/from a BM. Thus the transfer of a complete BMs contents would take several DMA Four PDP8e/BM DMA packing modes are available, transfers. all of which optimize the 12/16 bit word size differential. The first 2 modes transfer three 8-bit bytes (either high or low byte) in three BM words into two (OS8 packed format) PDP8e The third mode transfers three 16-bit BM words in four words. (OS8 packed format) PDP8e words. The fourth mode transfers two PDP8e 12-bit words in BM data in sign-extended EAE (extended arithmetic element of the PDP8e) double precision format so that the PDP8e can do arithmetic on full BM words without extensive packing and unpacking.

# 3.1 Physical BM memory addressing