RING STUDIES

Laboratory

ISSN - 0735-2867

# TURE INDEPENDENT ENVIRONMENT LOPING ENGINEERING SOFTWARE ON MIMD COMPUTERS

by

P-152.

KARIM A. VALIMOHAMED L. A. LOPEZ

Technical Report of Research

Supported by

National Aeronautics and Space Administration - Langley Research Center

THE THE REST OF STATE OF THE ST

Unclas 63/61 0278793

# ARCHITECTURE-INDEPENDENT ENVIRONMENT FOR DEVELOPING ENGINEERING SOFTWARE ON MIMD COMPUTERS

BY

KARIM A. VALIMOHAMED L. A. LOPEZ

FINAL REPORT

For Research Sponsored by NASA Langley (CSM) Grant #NAG-1-5-25622

| _           |

|-------------|

| _           |

| _           |

| _           |

| <del></del> |

|             |

| _           |

| -           |

|             |

| <u></u> .   |

|             |

|             |

|             |

|             |

#### **ABSTRACT**

Engineers are constantly faced with solving problems of increasing complexity and detail. They frequently rely upon numerical methods to solve these problems, and their insatiable appetite for improved performance from computing hardware has reached a point where the computational requirements exceed reasonable expectations of the performance of Von-Neumann (serial) computers.

Multiple Instruction stream Multiple Data stream (MIMD) computers have been developed to overcome the performance limitations of serial computers. The hardware architectures of MIMD computers vary considerably and are much more sophisticated than serial computers. Developing large scale software for a variety of MIMD computers is difficult and expensive. There is a need to provide tools that facilitate programming these machines.

The first part of this report examines the issues that must be considered to develop those tools. The two main areas of concern were architecture independence and data management. Architecture independent software facilitates software portability and improves the longevity and utility of the software product. It provides some form of insurance for the investment of time and effort that goes into developing the software. The management of data is a crucial aspect of solving large engineering problems. It must be considered in light of the new hardware organizations that are available.

The second part of the report describes the functional design and implementation of a software environment that facilitates developing architecture independent software for large engineering applications. The topics of discussion include: a description of the model that supports the development of architecture independent software; identifying and exploiting concurrency within the application program; data coherence; engineering data base and memory management.

The scope of the research is restricted to the development of the conceptual design of the environment and the implementation of a prototype system on a distributed memory system. The results obtained from developing two application problems related to finite element analysis are discussed. It is shown that the application program is indeed architecture-independent however the implementation of a shared memory prototype is left for future work.

- >

#### **ACKNOWLEDGEMENTS**

This report is based on the dissertation submitted to the Graduate College of the University of Illinois at Urbana-Champaign by Karim A. Valimohamed in partial fulfillment of the requirements for the Doctor of Philosophy degree in Civil Engineering. The research was conducted under the supervision of Professor Leonard A. Lopez.

Financial assistance for this study was provided primarily by the Computational Structural Mechanics Group at NASA – Langley. Initial support was also provided by the Apollo Computer Company. This support is gratefully acknowledged.

The authors wish to thank Dr. Norman Knight and Mr. William Greene of NASA for suggesting the problem, and for their help and encouragement throughout the investigation. A special thanks goes to Ms. Linda Schub, Dr. Scott Schiff, and Ms. Nan Fancher for their contributions to various parts of the investigation.

|  |  | • |

|--|--|---|

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  | , |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  | • |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  | • |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  | - |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  | • |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  | - |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  | _ |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  | _ |

|  |  | _ |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  | - |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  | - |

|  |  |   |

|  |  |   |

|  |  | 7 |

|  |  |   |

|  |  | - |

|  |  |   |

# TABLE OF CONTENTS

|   |                                                                     | Page |

|---|---------------------------------------------------------------------|------|

| 1 | INTRODUCTION                                                        | 1    |

|   | 1.1 OVERVIEW OF THE PROBLEM                                         | . 1  |

|   | 1.2 MIMD ARCHITECTURES                                              | . 2  |

|   | 1.3 CONCURRENCY IN THE FINITE ELEMENT METHOD                        | . 5  |

|   | 1.3.1 The Assembly Process                                          | . 6  |

|   | 1.3.2 Solution of the System of Equations                           | . 7  |

|   | 1.4 APPLICATIONS OF FEM ON MIMD MACHINES                            | . 8  |

|   | 1.4.1 Hardware Approaches                                           | . 8  |

|   | 1.4.2 Software Approaches                                           | . 8  |

|   | 1.4.3 Observations on Existing FEM Applications on MIMD Computers . | . 9  |

|   | 1.4.4 Tools to Facilitate Software Development for MIMD computers   | . 10 |

|   | 1.5 RESEARCH OBJECTIVES                                             | . 12 |

|   | 1.6 OUTLINE OF REPORT                                               | . 13 |

|   | 1.7 ACRONYMS                                                        | . 13 |

| 2 | BACKGROUND                                                          | . 15 |

|   | 2.1 SPEEDUP                                                         | . 15 |

|   | 2.2 TASKS, DATA, AND GRANULARITY                                    | . 16 |

|   | 2.3 SCHEDULING, SYNCHRONIZATION AND LOAD BALANCING                  | . 17 |

|   | 2.4 DATA STRUCTURES AND COHERENCE                                   | . 19 |

|   | 2.5 DATA AND MEMORY MANAGEMENT                                      | . 22 |

|   | 2.6 OTHER FACTORS INFLUENCING PERFORMANCE                           | . 23 |

| 3 | MIMD ENVIRONMENTAL ISSUES AND NEEDS                                 | . 25 |

|   | 3.1 PROGRAMMING ENVIRONMENTS                                        | . 25 |

|   | 3.1.1 Introduction                                               | 25         |

|---|------------------------------------------------------------------|------------|

|   | 3.1.2 Why We Need a Broader Based Environment                    | 25         |

|   | 3.2 TYPES OF TOOLS IN THE ENVIRONMENT                            | 27         |

|   | 3.3 EVOLUTION OF LANGUAGE LAYER ENVIRONMENTS                     | <b>3</b> 0 |

|   | 3.4 PROGRAMMING ISSUES                                           | 35         |

|   | 3.4.1 Data Definition Issues                                     | <b>3</b> 5 |

|   | 3.4.2 HLL Control Structure                                      | <b>3</b> 6 |

|   | 3.4.3 Task Granularity                                           | 38         |

|   | 3.4.4 References to Data Objects in the HLL - Data Access Issues | 39         |

|   | 3.4.5 Task Common Areas                                          | 41         |

|   | 3.4.6 Low Level Fortran Procedures                               | 41         |

|   | 3.5 RUN TIME SUPPORT ISSUES                                      | 42         |

|   | 3.5.1 Synchronization and Scheduling                             | 42         |

|   | 3.5.2 Data and Memory Management                                 | 43         |

|   | 3.5.3 Memory Configurations                                      | 44         |

|   | 3.5.4 Data Coherence                                             | 45         |

|   | 3.5.5 Parallel I/O                                               | 47         |

|   | 3.6 SUMMARY OF NEEDS                                             | 48         |

| 4 | OVERVIEW OF THE CONCEPTUAL DESIGN                                | 49         |

|   | 4.1 SYSTEM CONCEPT                                               | 49         |

|   | 4.2 SYSTEM PROGRAMS AND OPERATION                                | 51         |

| 5 | FUNCTIONAL DESIGN OF THE SERVER PROGRAM                          | 55         |

| 5 |                                                                  |            |

|   | 5.1 GENERATING THE RUN-TIME SYSTEM                               | 55         |

|   | 5.1.1 The Data Definition Compiler                               | 55         |

|   | 5.1.2 The High Level Language Compiler                           | 56         |

|   | 5.1.3 The Procedural Compiler                                    | 57         |

|   | 5 2 DUN TIME CYCTEM COMPONENTS                                   | E 7        |

|   | 5.3 DETAILED DESIGN OF THE SERVER                       | 62         |

|---|---------------------------------------------------------|------------|

|   | 5.4 Considerations for Implementation                   | 67         |

| 6 | CONCEPTUAL DESIGN OF THE DISK MANAGER PROGRAM           | <b>6</b> 9 |

|   | 6.1 INTRODUCTION                                        | <b>6</b> 9 |

|   | 6.2 DISK MANAGER CONFIGURATION                          | <b>6</b> 9 |

|   | 6.3 CONSIDERATIONS FOR IMPLEMENTATION                   | 71         |

| 7 | CONCEPTUAL DESIGN OF THE CLIENT PROGRAM                 | 73         |

|   | 7.1 INTRODUCTION                                        | 73         |

|   | 7.2 ORGANIZATION OF THE CLIENT PROGRAM                  | 73         |

|   | 7.3 SYSTEM INITIALIZATION / TERMINATION                 | 75         |

|   | 7.4 USER INTERFACE                                      | 75         |

|   | 7.5 SCHEDULING AND SYNCHRONIZATION MECHANISM            | 76         |

| 8 | IMPLEMENTATION                                          | 79         |

|   | 8.1 FUNCTIONAL TOOLS FOR SUPPORTING THE SYSTEM PROGRAMS | 79         |

|   | 8.1.1 Multitasking                                      | 80         |

|   | 8.1.2 Messages                                          | 80         |

|   | 8.1.3 Queues                                            |            |

|   | 8.1.4 Events                                            |            |

|   | 8.1.5 Locks                                             |            |

|   | 8.2 IMPLEMENTATION OF THE SERVER PROGRAM                |            |

|   | 8.2.1 Virtual Memory                                    |            |

|   | 8.2.2 Software Virtual Memory                           |            |

|   | 8.2.3 Maintaining Data Coherence                        |            |

|   | 8.2.4 Organization of the Server Program                |            |

|   | 8.3 IMPLEMENTATION OF THE DISK MANAGER PROGRAM          |            |

|   | 8.3.1 Mapping the Data Objects to Disk Files            |            |

|   | 8.3.2 Object Pointers and Data Base Size                | 93         |

|    | 8.4 IMPLEMENTATION OF THE CLIENT PROGRAM                    | 95  |

|----|-------------------------------------------------------------|-----|

|    | 8.4.1 Relative Granularity                                  | 95  |

|    | 8.4.2 Processor Granularity                                 | 96  |

|    | 8.4.3 Mapping Relative Granularity to Processor Granularity | 96  |

|    | 8.4.4 Automated Synchronization and Scheduling              | 97  |

|    | 8.5 SPECIAL CONSIDERATION FOR PARALLEL PROCESSING           | 100 |

|    | 8.5.1 Mapping the Environment on Apollo Workstations        | 101 |

|    | 8.5.2 Observations On Message Passing Systems               | 101 |

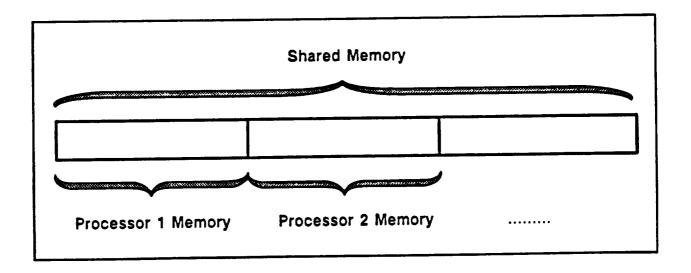

|    | 8.5.3 Shared Memory Considerations                          | 102 |

| 9  | APPLICATION PROBLEMS                                        | 105 |

|    | 9.1 HARDWARE USED FOR DEMONSTRATION PROBLEMS                | 105 |

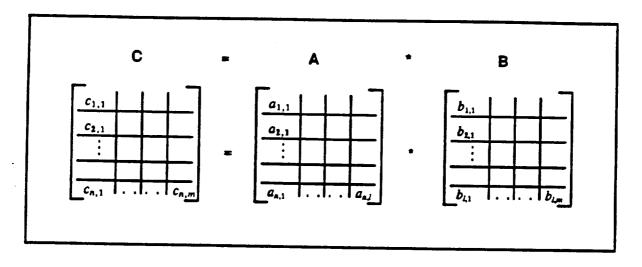

|    | 9.2 APPLICATION 1: MATRIX MULTIPLICATION                    | 105 |

|    | 9.2.1 Description of the Problem                            | 105 |

|    | 9.2.2 Programming notes                                     | 107 |

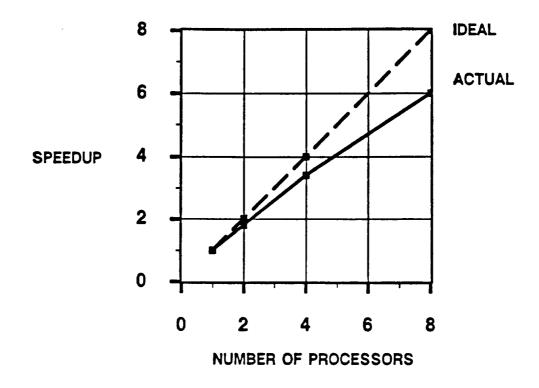

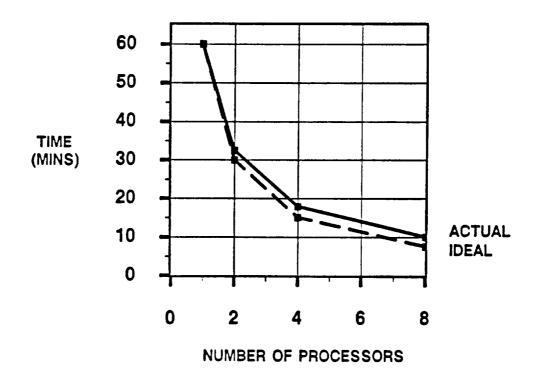

|    | 9.2.3 Results and Observations                              | 110 |

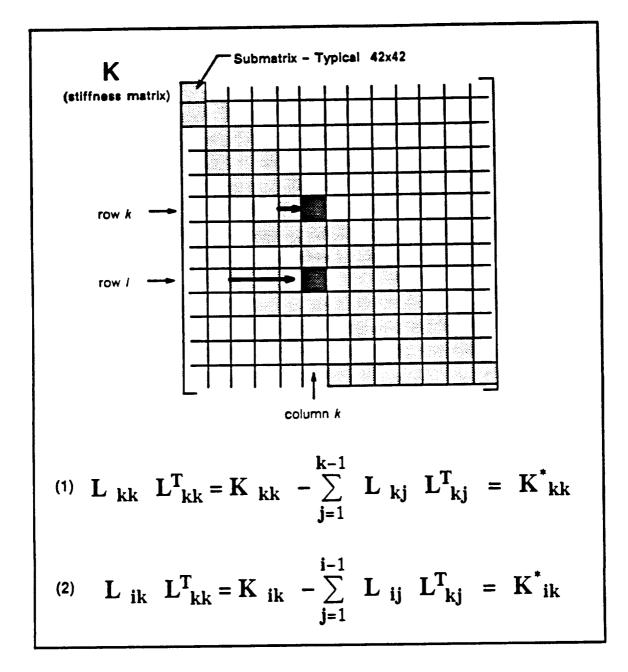

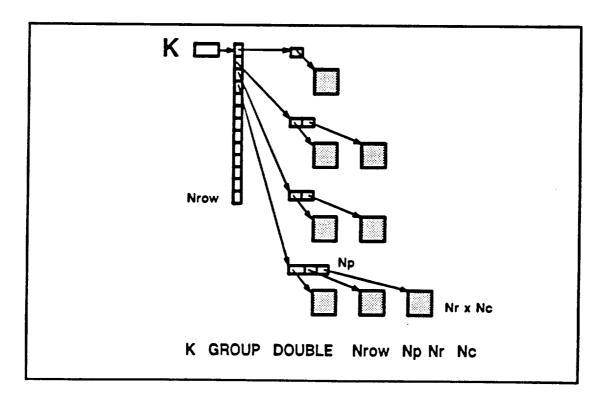

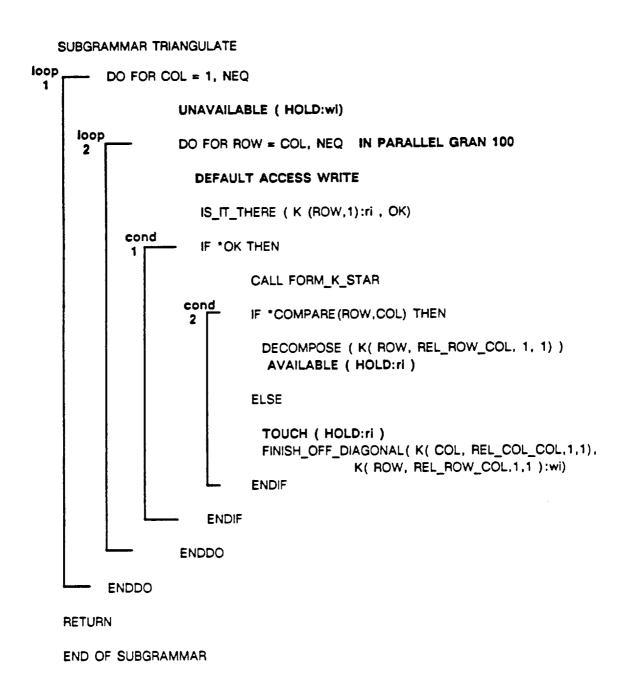

|    | 9.3 APPLICATION 2: BLOCK CHOLESKY DECOMPOSITION             | 113 |

|    | 9.3.1 Description of the Problem                            | 113 |

|    | 9.3.2 Programming notes                                     | 116 |

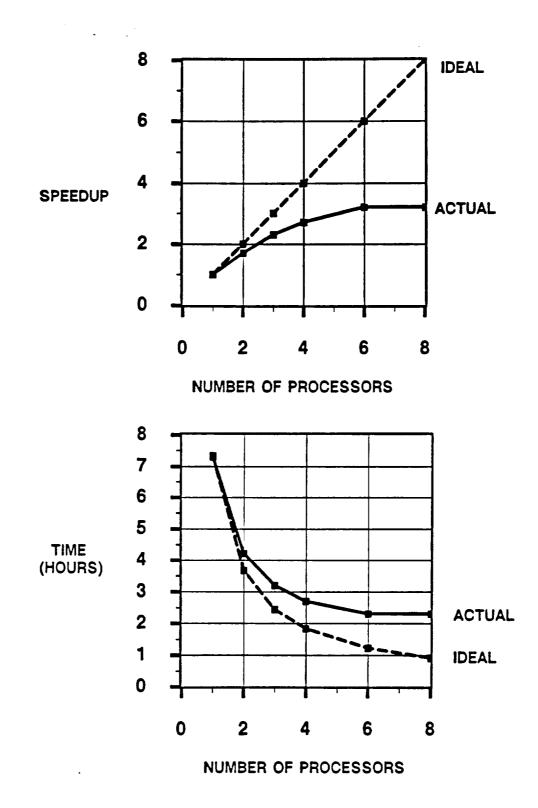

|    | 9.3.3 Results and Observations                              | 122 |

| 10 | CONCLUSIONS AND RECOMMENDATIONS                             | 127 |

|    | 10.1 SUMMARY OF OBSERVATIONS AND CONCLUSIONS                | 127 |

|    | 10.2 RECOMMENDATIONS FOR FUTURE WORK                        | 131 |

| RE | FERENCES                                                    | 135 |

|    |                                                             |     |

# LIST OF FIGURES

| Figure  | P                                                             | age |

|---------|---------------------------------------------------------------|-----|

| 1.2-1   | MIMD Architectures                                            | 3   |

| 2.4-1   | Data Conflicts During Stiffness Matrix Generation             | 20  |

| 3.1.1-1 | Function of the Programming Environment                       | 26  |

| 3.3-1   | Evolution of Programmer View of the System                    | 32  |

| 3.3-2   | HLL instruction and corresponding FORTRAN subprogram          | 33  |

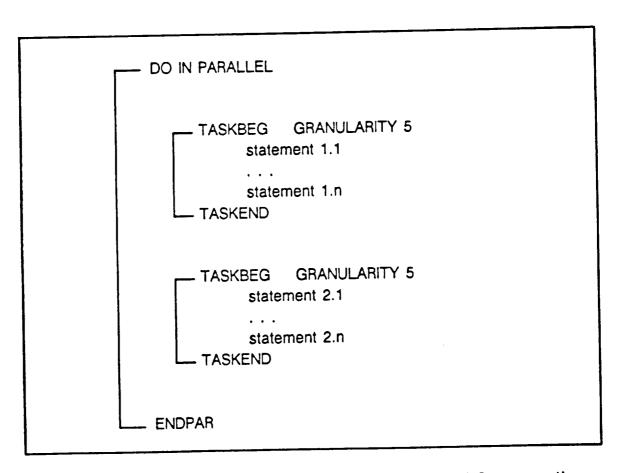

| 3.4.2-1 | Mutually Exclusive Tasks to be Executed Concurrently          | 37  |

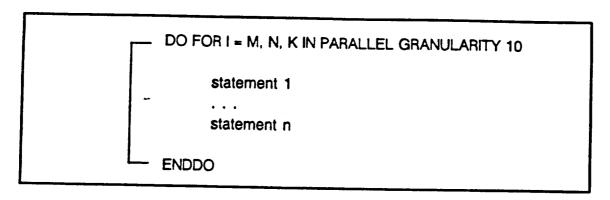

| 3.4.2-2 | Parallel Do-Loop                                              | 38  |

| 3.4.4-1 | Examples of using Data Attributes                             | 40  |

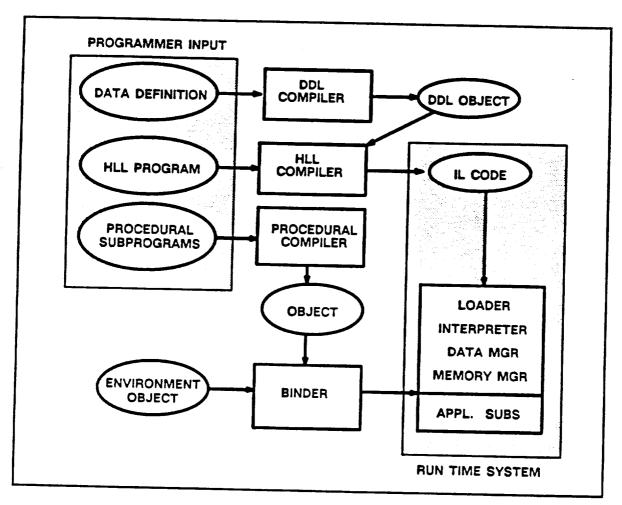

| 4.2-1   | Functional Components Of The Environment                      | 52  |

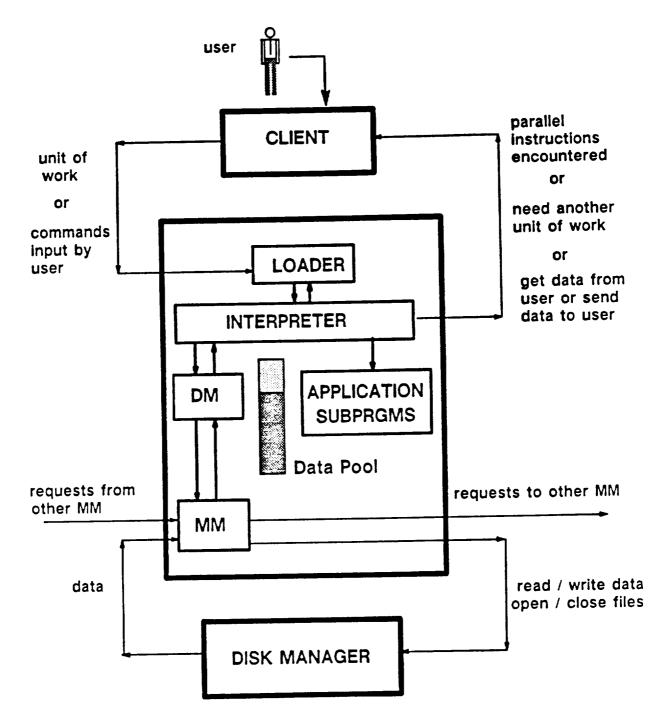

| 4.2-2   | Client - Server - Disk Manager Interaction                    | 53  |

| 5.1-1   | Developing the Run Time Executive                             | 56  |

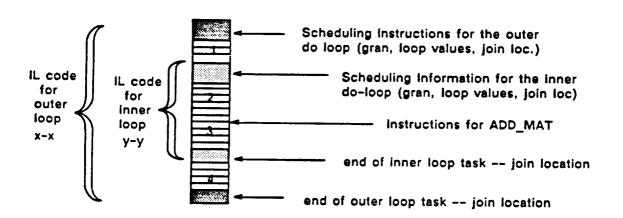

| 5.1.2-1 | HLL - IL Code Transformation                                  | 58  |

| 5.2.1-1 | Interaction Of Server With Other Components                   | 59  |

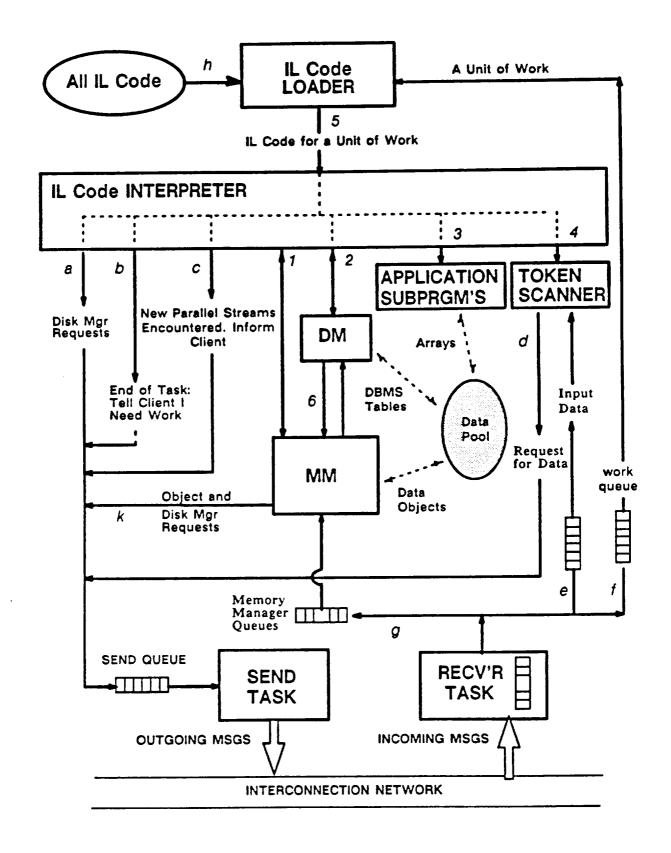

| 5.3-1   | Functional Details of the Server Program                      | 63  |

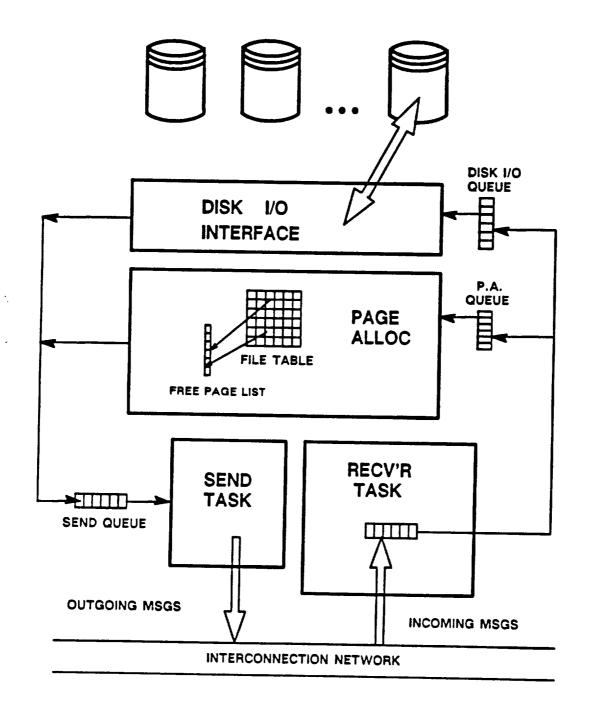

| 6.2-1   | Disk Manager Configuration                                    | 70  |

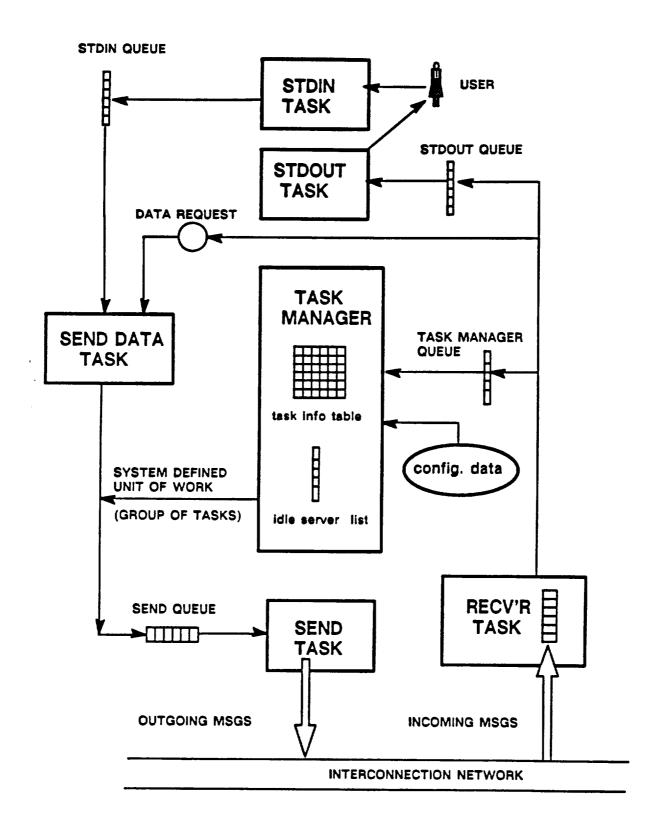

| 7.2-1   | Conceptual Design of the CLIENT Program                       | 74  |

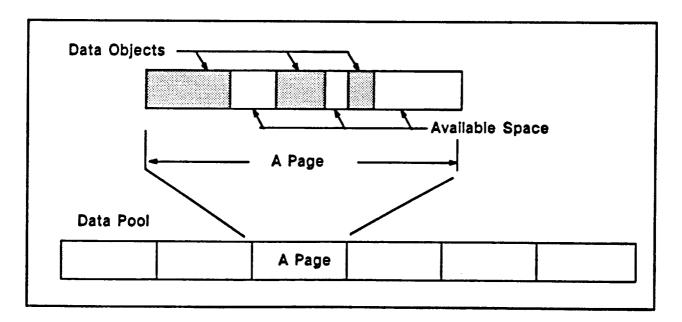

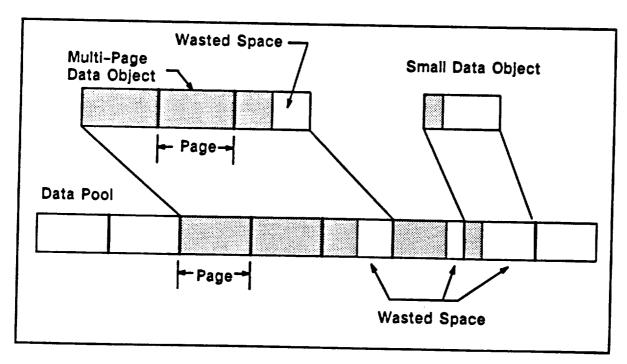

| 8.2.2-1 | Mapping Objects in a Paging System                            | 84  |

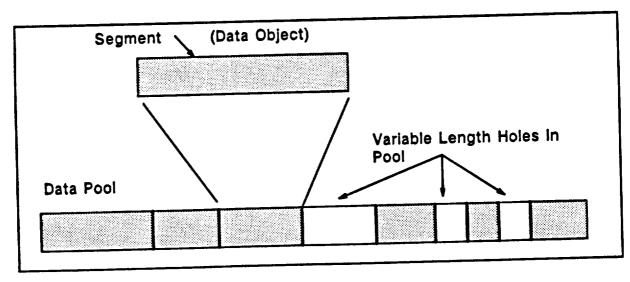

| 8.2.2-2 | Mapping Objects in a Segmentation System                      | 85  |

| 8.2.2-3 | Mapping Objects in a Paged-Segmentation System                | 86  |

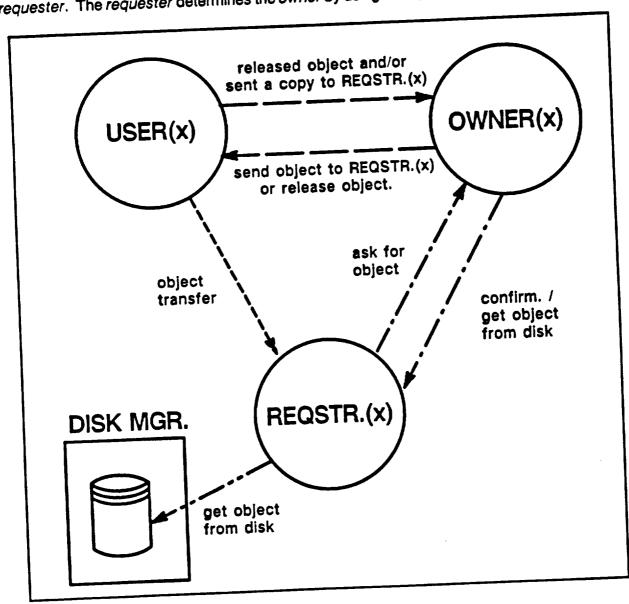

| 8.2.3-1 | Owner / User / Requester / Disk Mgr. Interaction              | 88  |

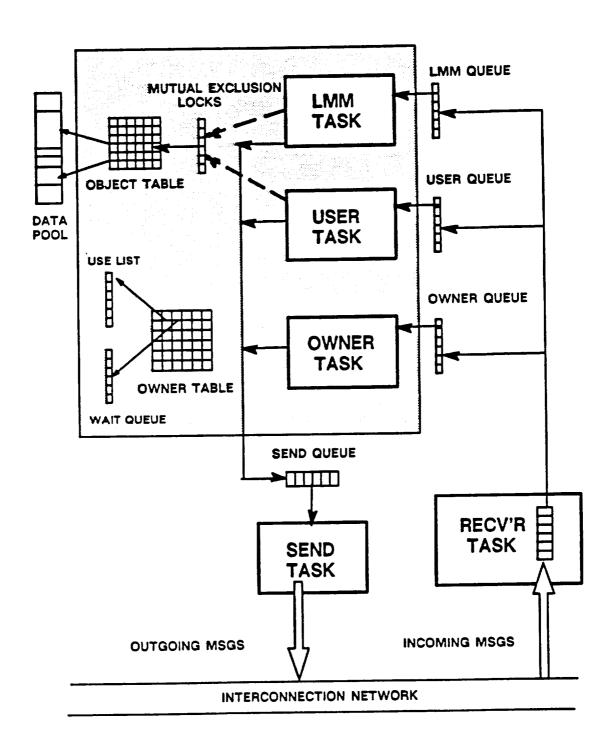

| 8.2.4-1 | Implementation of the Server Program                          | 91  |

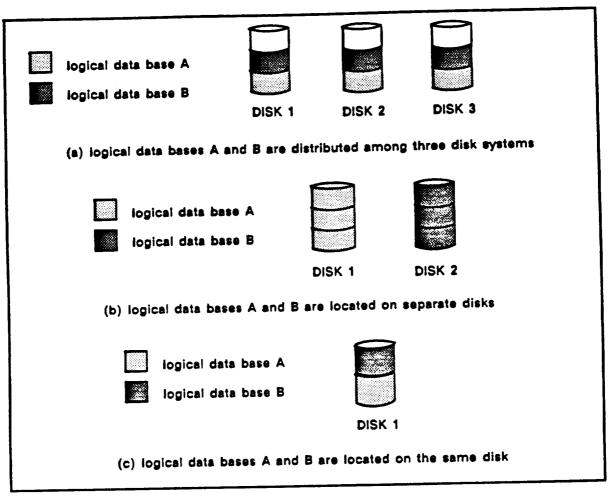

| 8.3.1-1 | Mapping Logical Data Spaces onto Disks                        | 93  |

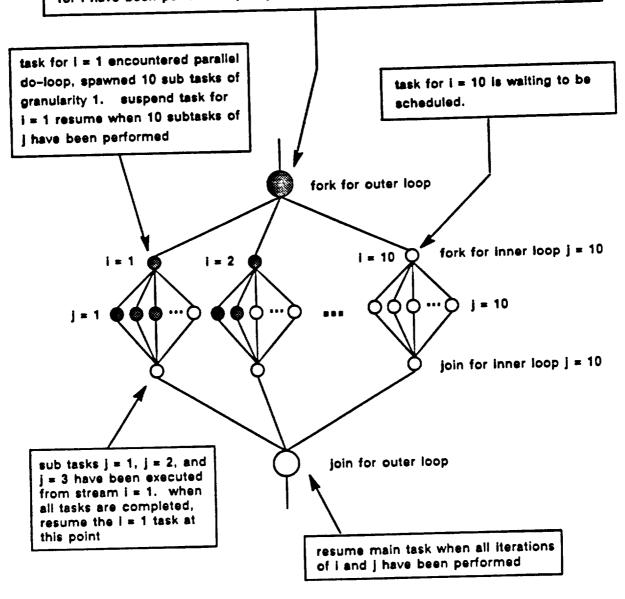

| 8.4.4-1 | Task Scheduling for Matrix Addition Example of Figure 5.1.2-1 | 99  |

| 8.5.3-1 | Segmented Shared Memory 103                                |

|---------|------------------------------------------------------------|

| 9.2.1-1 | Hypermatrix Multiplication Problem 106                     |

| 9.2.2-1 | Data Definition of Hypermatrices A, B and C                |

| 9.2.2-2 | HLL Code for the Hypermatrix Problem                       |

| 9.2.3-1 | Performance for the Matrix Multiplication Problem          |

| 9.3.1–1 | Block Cholesky Decomposition Equations                     |

| 9.3.2-1 | Data Structure for the Stiffness Matrix 116                |

| 9.3.2-2 | Main Routine (algorithm 1) for Cholesky Decomposition      |

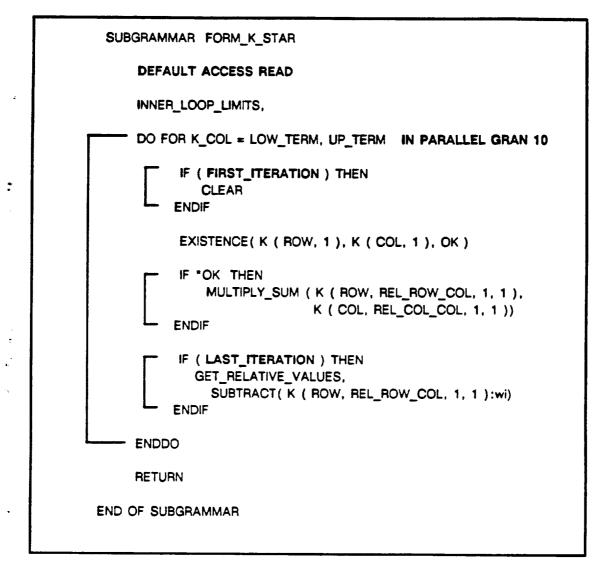

| 9.3.2-3 | HLL Code for the K* Operation                              |

| 9.3.2-4 | Alternative Algorithms for Cholesky Decomposition 121      |

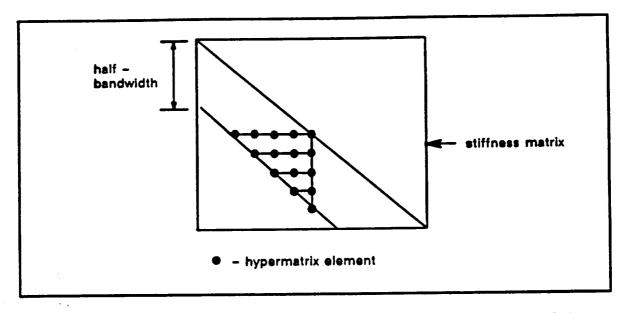

| 9.3.3-1 | Terms Involved for the K* Operation for a Given Column 123 |

| 9.3.3-1 | Performance of the Cholesky Decomposition Application 125  |

#### CHAPTER 1

#### INTRODUCTION

# 1.1 OVERVIEW OF THE PROBLEM

Engineers and scientists rely upon numerical methods to solve complex analytical problems. The analysis of such problems has been facilitated by technological advances in electronic computation. The availability of general purpose computers has influenced the development and application of numerical methods in both engineering and in the sciences. This report addresses the issues related developing large scale software for engineering applications on computing hardware known as Multiple Instruction stream Multiple Data stream (MIMD) computers. The issues examined herein include the ability to develop architecture-independent software applications and the data management aspects of engineering problems.

The finite element method (FEM) is used as a focus problem throughout the report. The method grew out of the need to solve structural analysis problems in the aerospace industry during the late 1950's. Since then, FEM techniques have evolved rapidly, and are now established as a basic method for the analysis of complex engineering problems [15]. The method is widely used in the areas of soil mechanics, heat conduction, aerodynamics, and fluid flow. In structural engineering, it has been used for linear, nonlinear, static, and dynamic analysis of complex problems. In the remainder of this paper, reference to the FEM will be made in the context of its application in structural analysis

Engineers are constantly faced with solving problems of increasing complexity and detail. Their insatiable appetite for improved computational performance from the hardware has reached a point where computational requirements often exceed reasonable expectations on the capacity of Von–Neumann type computers. The latter are generally referred to as "serial computers" herein. Although the revolution in microelectronics has resulted in tremendous advances in computing power on a single chip, the speed of light ultimately constrains the performance that can be obtained from a single chip. Therefore novel computer architectures have been developed in an attempt to satisfy the performance requirements of compute–intensive problems. These architectures incorporate multiple processors

that cooperate with each other to achieve the solution to a single problem. These multiprocessor computers are also referred to as parallel computers.

History shows that the development of the finite element method has been closely linked to advances in computer technology; each new generation of hardware and software has permitted users to solve problems of increasing complexity. Recent developments in hardware technology provide parallel processing capabilities that are suited to exploit the natural parallelism inherent in the finite element method [52].

The idea of exploiting parallelism is not new, and various forms of parallelism exist to differing degrees in all computers at the arithmetic and and storage levels. Historically, parallelism at the processor level was an integral part of the early ILLIAC IV design but was obviated by progress is microelectronics [15]. Early parallel machines like ILLIAC IV were not very popular with engineers because they were too expensive, too cumbersome to program, and were not available for general use. Today, parallel computers are commercially available and, in some instances, may be a worthwhile investment.

#### 1.2 MIMD ARCHITECTURES

The number and type of processors, memory modules, and their interconnecting network are among the many distinguishing features that are used to classify the architectures of parallel computers. Various other taxonomies[49] [39] [38] [30] [29] [40] and type architectures [76] have been developed in order to classify machines that have similar salient features.

In this paper, only those architectures referred to as Multiple Instruction Multiple Data stream computers are considered. This group of machines is based on a a taxonomy developed by Flynn. It classifies machines by the number of instruction and data streams. Despite its generality, Flynn's taxonomy is commonly used in the scientific and engineering communities.

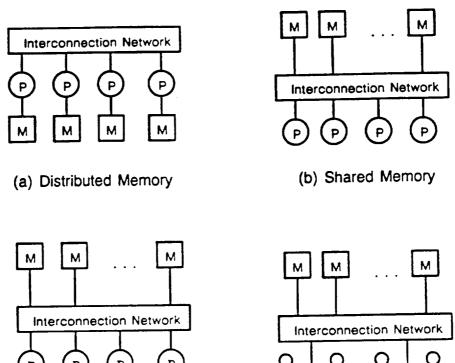

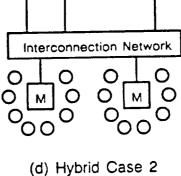

The term MIMD provides a rather obscure definition for the classification of computers. Therefore, for the purposes of identifying the machine architectures that will be referred to in this report, a simple scheme proposed by Karp [45] is used. It consists of three types of machines, namely shared memory, message-passing, and hybrid systems. Their features are described below and their schematics are illustrated in figure 1.2-1.

(c) Hybrid Case 1

KEY

Memory Module

Processor

Cluster of Processors with Shared Memory

Figure 1.2-1. MIMD Architectures

Distributed-memory or loosely coupled systems, are networks of computing elements each having its own memory. No memory is globally accessible. Communication and data transfer is accomplished by "message passing". Examples of homogeneous message passing systems include the Hypercube [71] and Intel IPSC. General networks containing nonhomogeneous computing elements also fall into this category. The processing elements are combined by a multicomputer interconnection network that can be classified as asynchronous, decentralized, or packet-switched (fig. 1.2-1.a) [13].

Shared-memory or tightly coupled systems, have a single global memory that is shared by all the processing elements. Each processor may have its own local memory, such as vector registers on the Cray X-MP [50] or the cache on the IBM 3090 [83]. The use of such local memory is transparent to the user. Communication is accomplished via shared variables. An example of such a computer is the Alliant FX/8 [4]. The processors and memory modules are combined using a multiprocessor interconnection network that can be classified as being shared buses, crossbars, or multi-stage (fig. 1.2-1.b) [13].

Hybrid systems exist between the two extremes. They are systems which have properties of both shared memory and message-passing systems (figs. 1.2-1.c, 1.2-1.d). They are programmed as shared-memory machines but can have data access delays like message passing systems. These delays are much smaller than on message passing systems, but they can be significant [45]. Memory hierarchies can be found in some architectures like the ETA 10 [27] and Cedar [48], while other machines such as the IBM-RP3 [67] and Flex-32 [81] can be configured to suit the needs of the application.

The majority of commercially available MIMD computers are either shared or distributed memory type architectures. Hybrid machines (Cedar and RP3) are still in the experimental stages of development. MIMD machines provide a significant improvement in peak performance over serial machines, and therefore attract many large scale engineering applications that are inherently amenable to parallel processing.

MIMD computers are best utilized when they exploit both the concurrency and the vectorization that exists within the application code. Concurrency is the ability to execute multiple stream of instruction on multiple streams of data, whereas, vectorization is the ability to work on multiple stream of data for one stream of instructions. A sophisticated processor on an MIMD machine (e.g. Cray–XMP, Alliant–FX80) is usually equipped with a vector facil-

ity, thereby providing the capability to exploit both vectorization and concurrency within the application. Typically, such potential exists within do-loop type programming constructs of procedural languages. The finite element method has much potential for improved performance on MIMD computers because of the inherent concurrency and vectorization in the procedure. How can we exploit this technology?

#### 1.3 CONCURRENCY IN THE FINITE ELEMENT METHOD

The finite element method algorithm for a linear static problem using the direct stiffness method consists of three major stages. In the preprocessing stage, the problem is defined by identifying the elements, the boundary conditions or constraints, and the applied loadings. In the processing stage, the stiffness matrices and internal load vectors for all of the elements are generated and are assembled into a global structure stiffness matrix and the global load vector. Given the load vector and stiffness matrix, the displacements of the structure are obtained by solving a linear system of equations (see equation 1.3–1). Finally, in the postprocessing stage, element quantities such as stresses and strains for some or all of the elements are computed.

There is potential for concurrency and vector processing in all three stages of the method. The time spent in both the pre and post processing stages is dominated by the user. In the preprocessing stage, engineers develop the FEM model by using advanced graphics software on workstations. In the near future, graphics systems will be augmented with knowledge based systems that guide the engineer in developing the model. In the post processing stage, the engineer interacts with the system to interpret the results. This requires the use of advanced graphics/visualization software. Although there is a significant

amount of computation in the pre and postprocessing stage, the processor time used in these areas is overshadowed by the time spent in the processing stage.

The processing stage is the most computation intensive part of the finite element problem. There is very little interaction with the user (with the exception of nonlinear solutions), and there is a tremendous potential for the use of concurrent and vector processing. Generating the individual stiffness matrices and load vectors for the elements can be performed concurrently since the computation of one element quantity is independent of all other elements. A large portion of the assembly of the global stiffness matrix can also be done in parallel. In systems employing the direct stiffness method, the solution to the system of equations can begin once the global stiffness matrix and load vector have been assembled. Direct methods of solving such equations exist in many of the existing large scale systems. The assembly and solution procedures are described in more detail in the following subsections.

#### 1.3.1 The Assembly Process

An examination of the details of the global stiffness assembly process can help explain some of the aspects of parallel computing that should be considered.

A structure can be composed of a hierarchy of substructures or simply an array of a distinct element types. The elements can vary from a special purpose element, to a complex 3D shell element, to a simple truss component. There are several algorithms that can be used to compute the global stiffness matrix. Carey [14] has identified three categories, namely: (1) subdomain splitting; (2) substructure techniques; and (3) splitting.

In the first method, the domain is subdivided into overlapping regions. The original problem is decomposed into one that involves the solution of boundary value problems on the subdomain. In the second approach, the structure is divided into substructures. Each substructure is treated as a separate domain. The third approach, splitting, can be used to reduce the number of dimensions in the split problem by replacing a two-dimensional problem by a series of one-dimensional problems.

Substructure techniques are most commonly used for the FEM because they map directly to the procedures for describing problems and for solving problems. The process of

describing a complex structure by the use of components (which in turn can be defined using sub-components) naturally lends itself to the substructure approach. Static condensation of substructures is used to reduce the size of stiffness matrix and to produce "super elements" [14]. In parallel processing, the calculation of the stiffness matrix for a substructure may be an ideal task unit. Furthermore, a substructure may be defined such that its interaction with other substructures is minimal, hence it is well suited for concurrent processing.

#### 1.3.2 Solution of the System of Equations

Traditionally, direct methods such as the Gaussian Elimination and Cholesky decomposition have been used to solve the system of equations associated with the FEM. Iterative methods are also used but to a lesser degree. The latter are inherently concurrent, and were used in the past when there were severe limitations on the amount of RAM available. However, since design problems in structural analysis frequently involve many right-hand side vectors (e.g. various load combinations), factorization of the system matrix followed by repeated sweeps is both preferable and possible with today's large memory configurations. As a result, direct methods have become the prevalent approach and are used widely with such sparse solution schemes as banded solvers, envelope (or profile) solvers, frontal solvers, and hypermatrix solvers.

For problems with a single load vector, iterative techniques may be a viable alternative, particularly when very large problems are considered, and when memory limitations become a significant constraint. Iterative methods are most effective when the matrix is symmetric, positive-definite, and diagonally dominant. Generally this is not the case for nonlinear problems.

In many cases the success of iterative methods depends on special preconditioning strategies. In such cases, the method may fail or not be practical, and the current trend back toward iterative methods because of memory limitations on MIMD computers may be a serious mistake. It may be better to examine other methods of using the memory that is available.

In the analysis of time-dependent and nonlinear problems using implicit integration, sparse linear system solution techniques are still required, and the above considerations apply. Such solution techniques are well suited to machines with large fast memories.

#### 1.4 APPLICATIONS OF FEM ON MIMD MACHINES

The advent of parallel processing has again escalated the research efforts on computer methods related to finite element techniques. The work associated with implementing the finite element method on MIMD machines has progressed on various topics. They include: (1) developing new algorithms for various components of the problem such as equation solving: (2) the development of special purpose software for a particular type of MIMD machine; (3) development of special purpose hardware; and (4), the transfer of existing finite element software systems to MIMD machines.

#### 1.4.1 Hardware Approaches

- Finite Element Machine [1] developed at NASA-Langley: consists of a lattice architecture with a global bus connecting all the processing elements.

- FEM-2 [69] developed at NASA-Langley: incorporated a different approach

to developing a finite element machine. The main feature was the use of

several layers of virtual machine concepts developed using a top-down rather

than a bottom-up approach.

- Parfem [61] developed at the University of Calgary: consists of several special purpose hardware modules used to generate element data, assemble the stiffness matrix, and solve the system of equations.

- Macropipelining approach proposed by Teng and Hwang [80]: intended to improve overall system performance by matching the processor bandwidth of all the component subsystems. The subsystems include: a host computer; preprocessor, linear system solver, and the postprocessor.

#### 1.4.2 Software Approaches

Since the processing stage is the most compute intensive portion of the finite element procedure, most of the research related to exploiting the concurrency in the finite element method has been focused on solving the system of equations. They include:

strategies for exploiting concurrency on both the assembly and solution processes. In particular, conjugate gradient multitasking [58], subdomain splitting [9], multicolor iterative methods [10], adaptive grids [1], gaussian elimination [2], and cholesky factorization [12] have been examined. An overview of other developments in this area can be found in [9].

- an applications library known as the uniform system. It has been developed

on the Butterfly [3],[2],[16], and has been used for the development of

CoFEM, a special purpose finite element program developed at BBN laboratories.

- PISCES [70]. This system was developed at the University of Virginia in cooperation with NASA-Langley, and is an environment to support parallel computing for scientific applications. An implementation exists on both the Flex-32 machine and on the Hypercube.

# 1.4.3 Observations on Existing FEM Applications on MIMD Computers

None of the hardware solutions that were just described has been completely developed and implemented. Furthermore, the author has not heard of any new proposals for developing special purpose finite element machines.

A large proportion of the software research has been focused on addressing very limited aspects of the finite element problem – developing and implementing better algorithms. However, these algorithms are suited to solving a restricted sets of problems, or focus on a relatively small aspect of the problem.

With the exception of PISCES, the projects identified above have not addressed the data management issues related to the solution of very large problems and, although, the concept of "windows" was proposed in the PISCES concept, the implementation of such a scheme has not been accomplished.

To develop general purpose solutions, all aspects of the problem must be examined. Very little work has been done on the development of complete general purpose systems. Examples of such systems for serial computers are ASKA, ADINA, ABAQUS, ANSYS, FINITE, and NASTRAN. These systems incorporate the concept of element libraries, various material models, and linear, nonlinear, and dynamic analysis capabilities; they operate on a wide variety of computers that embrace the FORTRAN model of computation.

Several commercial FEM programs have been ported to MIMD machines, but they have achieved limited success. Although larger problems are being solved faster, for the most part, the improvement is due to the faster clock speed and vector processing. When two or more processors are used, the improvement in performance seems to peak at a small number of processors [79]. This is because the conversion of these codes is often a simple compile combined with a few changes to obtain the best performance possible from the matrix operator packages. In essence, the codes have been vectorized by making use of the automatic vectorization algorithms built into the compilers. They have not been re-written to any extent so that the explicit concurrency inherent in the finite element method is exploited. It is not easy to exploit the latter in the context of just the FORTRAN model.

#### 1.4.4 Tools to Facilitate Software Development for MIMD computers

Programmers have found writing software for these machines to be difficult and expensive [74]. Unlike serial computers, there are many variables to consider when developing software for MIMD machines.

Several software options have been proposed to facilitate programming. They include: extending existing languages to express concurrency and synchronization; developing compilers that will identify the concurrency in programs; adding a "language layer" on top of existing languages to describe the desired concurrency and necessary synchronization, while allowing the basic applications program to remain "relatively" unaltered; defining new languages and compiler systems [60]. In addition, efforts are being directed towards developing systems capable of restructuring existing FORTRAN programs [17]. Currently, multiprocessor computers offer a rather restricted set of software tools with which to develop parallel programs [45], and for many applications, the full potential of parallel computing has not been realized yet [74].

The approaches described above are machine dependent – they are not totally portable. Generally, such tools are available only for tightly coupled multiprocessor systems in which compilers can generate the synchronization and scheduling instructions based on a data dependency analysis. Such features are not available for loosely coupled systems. This is a crucial issue when considering the longevity of software and the investment associated with its' development. A case in point is the failure of ETA systems. Developing

software for one type of machine can be very expensive! There are some developments in environments and programming tools [70][24][64] that assist programmers in developing portable code. However, these efforts have been restricted primarily to the control aspects of the program; i.e., describing to the computer when and how to do things in parallel.

The objective of developing these tools was to obtain improved performance by solving existing problems as fast as possible. These efforts have encountered various degrees of success. In some cases the approaches were focused on a rather small aspect of the total problem. In others, they were prohibitively expensive for general use because they incorporated special purpose hardware or software which was not portable. These approaches have not addressed the crucial data problems encountered when trying to solve very large problems. A key element in developing successful engineering systems is successful management of the large data spaces. Very little work has been done in this crucial area on MIMD machines.

In order to make progress in the development of engineering software on MIMD computers, it is necessary to restructure both the data and algorithms at a high level, as well as to vectorize the code at the lowest level [52]. This would simply be history repeating itself in the case of the finite element method. The development of the finite element method and its use for the analysis of large structural engineering problems has been directly linked with advances in computer technology. As computers changed, the algorithms changed.

The increased storage capacity of existing hardware has permitted larger problems to be analyzed – however this new technology is capable of doing much more. Thus, the philosophy employed herein is to find methods to solve the largest problem possible within a given time frame rather than trying to solve existing problems faster. Typical expected problem sizes will require data spaces of between 40 and 100 Gigabytes. This may seem large by today's standards, but not unreasonable; one Gigabyte problems are being solved on today's mini-supercomputers.

The solution of large problems must incorporate methods to manage data efficiently. Data management is the dominant system issue with serial computers. On MIMD computers, process control, load balancing, granularity of tasks, data access, and data coherence, must all be addressed along with data management and the finite element problem itself.

These considerations are further complicated when portability between shared and distributed memory computers is considered.

In serial computation, the FORTRAN model of computing provided a mechanism for developing portable code. Portability is still a major issue in parallel computing. With rapidly changing architectures, it would be foolish to develop codes based on one MIMD configuration. Unfortunately, there is no simple model of all MIMD computers that has been mapped into a simple portable implementation language.

#### 1.5 RESEARCH OBJECTIVES

The need to solve large structural engineering problems in the near future is the motivating factor for this investigation. This need calls for the development of a system that is capable of serving as an environment in which large scale engineering problems can be solved on a variety of MIMD machines. The objectives of the research are to develop a prototype system that provides engineering programmers with an easy and efficient means of developing large scale engineering software. It is imperative that the resulting engineering systems be portable, easy to program and maintain, and capable of exploiting the computational power offered by the next generation of computers. It is expected that such software systems will last for at least one or two decades.

The overall goal of this research is not simply to develop a computer program that will solve problems faster. The main emphasis is focused on developing a new approach to applying advanced computing technology to solve real engineering problems. The objectives are in keeping with the recent observations and recommendations of the Scientific Supercomputer Subcommittee [74]. They identified the need for high-level representation of algorithms with no machine-dependent semantics. Furthermore, it was noted that certain aspects such as the details of memory hierarchy management – vector registers, cache, virtual memory – should not be part of the user's program, but instead be optimized by the software itself. These notions have been the foundation of this research.

The scope of this research is restricted to the development of the conceptual design of the environment and the implementation of a prototype on a distributed memory system. A network of Apollo workstations was selected for the implementation of the prototype because of accessibility to the hardware and existing software tools.

#### 1.6 OUTLINE OF REPORT

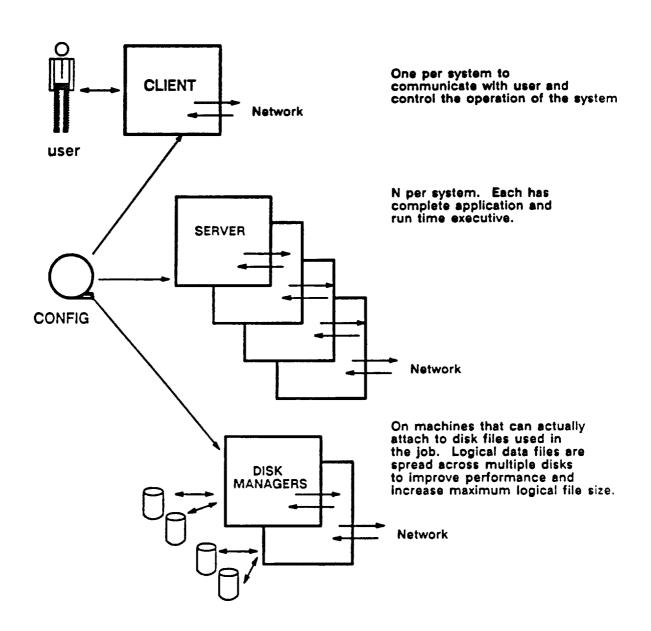

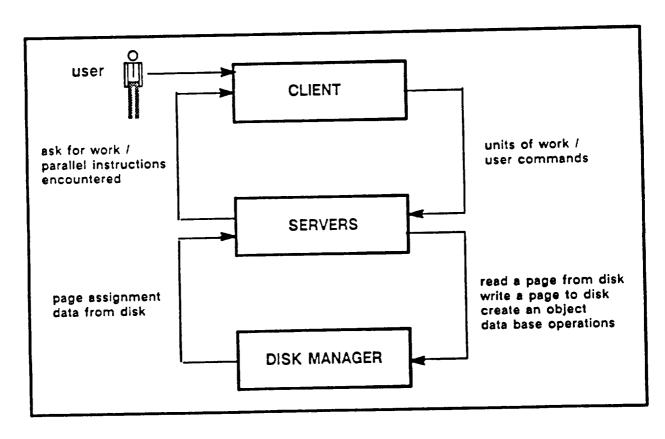

The report is divided into ten chapters. The first has been an introduction to the problem from an engineering point of view. However, the content of the report is interdisciplinary in nature. Hopefully, the result of the work will be used by engineers, but the concepts for achieving the results necessarily have a strong computer science flavor. Many engineers are not familiar with the problems associated with developing systems on MIMD computers. Hence, chapter two provides the reader with an introduction to the related issues, concepts, and terminology. Chapter three describes the evolution of a certain class of software environments that have been used successfully in the past on serial computers, and then develops the requirements for a new software environment for MIMD computers. Chapter four develops the general overview for an MIMD architecture independent environment that satisfies the needs expressed in chapter three. The environment calls for a three part system consisting of a Client program, multiple Server programs, and multiple Disk Manager programs. Chapters five through seven describe the functional design of each type of program in the environment, how they work, how they relate to each other, and to how they will relate to the application programs that they will support. Chapter eight addresses the functional details, and the reasoning used to arrive at the details of some of the major components of the three programs. Special emphasis is placed on the development of a virtual address space for the distributed memory architectures and how it can also be mapped to shared memory architectures. Chapter nine presents the details of two example applications problems and the corresponding programs that were used to solve them using a prototype of the environment. Finally, chapter ten presents a summary of the findings and identifies the potential for continued work in this area.

#### 1.7 ACRONYMS

The following is a list of acronyms that are used in this report. A description of each term is provided where it is first referenced in the text.

CPS Concurrent Programming System

CPU Central Processing Unit

DBMS Data Base Management System

DDL Data Definition Language

Disk Manager

DOF Degree Of Freedom

GB Gigabytes

GSS Guided Self Scheduling

HLL High Level Language

I/O input and Output

IL Intermediate Level

KB Kilobytes

MB Megabytes

MIMD Multiple Instruction Multiple Data

MM Memory Manager

OS Operating System

P.A. Page Allocation

RAM Random Access Memory

UDP User Datagram Protocol

#### **CHAPTER 2**

#### BACKGROUND

This chapter contains an overview of the computer related issues that arise when developing applications like the finite element method on MIMD computers. The purpose of this chapter is to familiarize non-computer-science readers with both the terminology used herein, and some of the more important programming issues.

#### 2.1 SPEEDUP

The actual speedup is an indication of how well a given application performs on an MIMID machine. It is defined as the ratio of the time to execute an efficient serial program for an application, to the time to execute a parallel program for the same application on n processors identical to the serial processor. The wall-clock time is used in the speedup calculation because it measures the actual time required to run the application – it includes the time for I/O and any overhead that is incurred in order to execute concurrently.

This definition for actual speedup specifies the best serial time rather than the time required to run the application on one processor, because sometimes there is a disparity between the two values. For example, a given algorithm may be very inefficient when applied on one processor. If such an algorithm is used to establish the serial time, the computation of the actual speedup will be misleading because the actual speedup value may appear to be very good despite the algorithm being very poor in reality.

The equation for determining the *theoretical speedup* provides a very useful indication of the potential limits on performance. It is not unusual for the uninitiated to believe that increasing the number of processors working on an application will automatically decrease the wall–clock time for that application. Yet, the sustained rates for some applications tends to be between 5 and 15 percent of peak performance [48]. An examination of the equation for theoretical speedup gives an indication why that happens.

The potential for speedup in a given application is significantly influenced by the amount of code present that must be executed serially, and by the system overhead. Amdahl's law characterizes the possibility for improved performance, or speedup, that can be

exploited for a given application. The law very simply states that if a machine has two modes of operation; a slow and fast mode, the overall performance will be heavily influenced by the slower mode. In the context of MIMD computers, the slow mode corresponds to the execution of serial parts of the code on a single processor, while the fast mode corresponds to concurrent execution of those parts of the code that can be done in parallel on multiple processors. A simplified version of Ware's equation (eqn 2.1–1) below, defines the theoretical speedup of an application given the percentage of code that can be executed concurrently and the number of processors used.

$$S(n,f) = \frac{1}{1 - (1 - \frac{1}{n})f}$$

(eqn 2.1-1)

where: S = speedup.

f = fraction of the number of instructions executed in parallel,

n =number of processors.

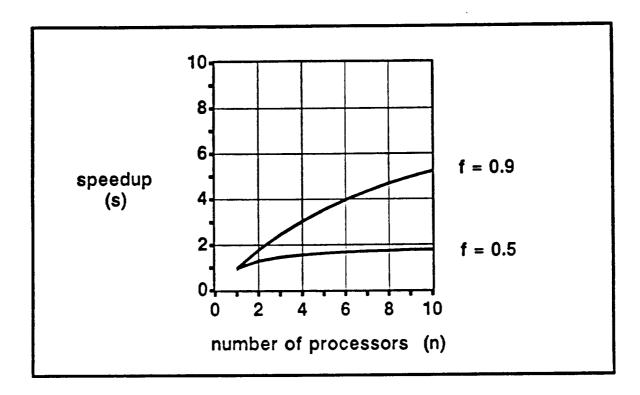

Equation 2.1–1 is overly simplistic and optimistic because it excludes the overhead required to operate with n processors. However, the point of this equation is that the amount of code executed in the serial mode must be minimized if any gains are to be made. For example, if the fraction of parallel code (f) is 50%, the maximum speedup will approach a factor of 2 as n approaches infinity. When the fraction of parallel code (f) is 90%, the speedup is only 5.3 for 10 processors, and it approaches 10 in the limit. This is illustrated in figure 2.1–1.

#### 2.2 TASKS, DATA, AND GRANULARITY

A task is a unit of work that consists of one or more computer instructions. An example of a task is the instructions that make up the body of a DO LOOP. DO LOOPs that are defined so that each iteration can be executed concurrently are called *parallel do loops* herein. A data object, or just object, can consist of anything from a single word of data, to a matrix, to an entire tree structure. The term *granularity* refers to the size of a task or a data object, and the terms *Fine*, *Medium and Coarse* are often used to characterize the granularity.

Figure 2.1-1 Illustration of Ware's Equation

Both data and task granularity influence the performance of an application program. The granularity of tasks is an important factor to consider when examining the issues related to load balancing, task scheduling, and task synchronization. Further details of these subjects are described in section 2.3. Data granularity affects the issues related to the access and modification of data. The performance issues affected by data granularity are discussed in section 2.4.

#### 2.3 SCHEDULING, SYNCHRONIZATION AND LOAD BALANCING

The stiffness matrix of a structural model can be generated by concurrently executing tasks at various granularity levels. For example, the tasks can consist of computing the contributions to the matrix at the: substructure level (coarse grained tasks); element level (medium grained tasks); or integration point level (fine grained tasks). Alternatively, a task can consist of computing two or more substructures, elements or integration points. How does a software engineer decide which is optimum? The answer depends on the number and type of processors that will execute the job. Tasks consisting of large substructure

calculations are best suited to architectures with a few very sophisticated processors (e.g. Cray-XMP). At the other extreme, computing the stiffness contribution at the integration point level is best suited to a machine that has thousands of simple processors (e.g. Connection Machine). For most commercially available multiprocessor computers (Alliant, Intel-iPSC), an ideal task would consist of one or more element calculations – the ideal number of elements is a function of the computational complexity of the element and the speed of the processors.

The Efficiency of an application is defined as the actual speedup of the application divided by the number of processors used for that application. Processor Utilization is the average percentage of processor time used. By definition, optimum efficiency is obtained when the speedup is maximized. The case of optimum efficiency may not coincide with the situation in which the system has the highest value of processor utilization or when optimum load balancing occurs. Generally, optimum efficiency occurs when minimal time is spent waiting for processors to complete their tasks and synchronize with each other. Hence, the efficiency of an application program on a given MIMD system depends on the ability to schedule and synchronize the execution of tasks effectively and efficiently.

Load Balancing is the ability to assign tasks to all the processors so that they are utilized evenly. Optimal load balancing of an algorithm generally does not guarantee the best system utilization because of the overhead and uncertainties associated with task scheduling and synchronization.

The process of allocating tasks to the processors is known as scheduling. There are two general methods of determining how to schedule tasks. *Static scheduling* (also called pre-scheduling) means that all decisions are done at compile time. *Dynamic scheduling* (also called self-scheduling) means that all decisions are made at run time.

There are many questions that need to be answered in order to schedule tasks effectively. For instance, when allocating iterations of a parallel do-loop to the processors on an MIMD system, how many iterations should each processor get? What happens when the number of instructions executed increases or decreases with every iteration? If there are conditional statements within the loop body, how much time will be spent processing an iteration? How should the scheduling algorithm incorporate disparities in processor perform-

ance? From a performance point-of-view, is it better to avoid the overhead of scheduling and synchronization by executing the loop serially or on a limited number of processors?

The programming aspects of synchronization that occur during the assembly procedure appear to be easy. The concurrent computation of the elements or substructures can be specified via simple parallel do loops. Each outer loop can do a substructure, each second level loop an element, and each third level loop an integration point on the element. The implication of the end of a parallel inner loop is that all processors working on the loop must complete their tasks prior to resuming the corresponding next higher level loop. To accomplish this, a synchronization operation known as a *barrier* is established. Synchronization mechanisms are often automatically generated by the compiler using the hardware of the machine. However, this feature is not available on all machines, especially loosely coupled processor systems. Therefore, the programmer has to explicitly define synchronization operations within the program.

Barriers are also used at a higher level. For example, when using direct methods to solve the stiffness equations, it is necessary to wait until the contribution of the last element has been made in the stiffness matrix before beginning to solve the system of equations. That wait constitutes a barrier.

Scheduling the tasks needed to solve the system of equations is much more difficult than in the assembly process because of the complex data dependencies involved with decomposition, forward elimination, and back substitution. Various types of task related barriers and object related barriers are needed. The latter are barriers that prevent a task from accessing a data object before it should. This is done to insure that correct results will be obtained. The details of this concept are discussed in chapter nine.

### 2.4 DATA STRUCTURES AND COHERENCE

In order to ensure that correct results are obtained, data coherence must be maintained during the execution of a job. Data coherence means that multiple copies of a datum must be consistent when referenced by multiple processors. This implies that a datum cannot be modified by two or more processors simultaneously. In engineering programs, a data object often consists of more than one word. Typically, the objects are vectors and matrices. There are two general ways of maintaining coherence:

- a) objects to be modified are only available to one processor at a time -- object protection;

- a) programmers write their code so that processors operate on mutually exclusive sections of the same object programmed protection.

The ability to perform operations concurrently is a function of how well conflicts related to access of shared data objects can be avoided. A data dependency analysis may determine how to synchronize tasks and operations so that conflicts are avoided. Sometimes, the dependency analysis cannot yield conclusive results at compile time because the nature of the conflict is a run-time problem; i.e., it is a function of the data used in the program. For example, when a global stiffness matrix is generated, the contributions of a given element will often coincide with those of adjacent elements.

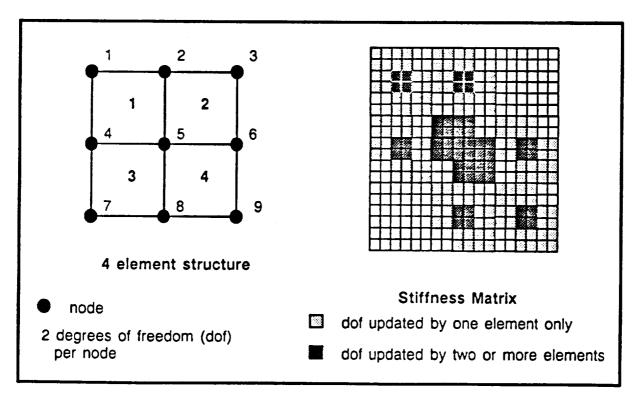

Figure 2.4–1 illustrates the conflicts that can occur when assembling the stiffness matrix. If one assumes that the contribution of one of the four elements in the model on the left of the figure is handled by a different processor, the figure on the right side shows areas of the matrix accessed by two or more processors. In order to avoid conflicts the programmer

Figure 2.4-1 Data Conflicts During Stiffness Matrix Generation

would need a priori knowledge of the structure or develop an algorithm that sorts the elements into groups of non-conflicting element calculations.

To further illustrate this problem, consider how the program would be written. If the stiffness matrix is defined as a single physical data object, and if any processor can make an arbitrary modification to the matrix via an element contribution, then only one processor can be allowed to modify the matrix at any given time to ensure data coherence. If other processors wish to update it they must wait their turn; there is very little room for concurrency.

On a shared memory machine, a *critical section* can be used in the program when the stiffness matrix is updated. A critical section is analogous to a lock; one processor obtains a lock on the object thereby preventing all other processors from accessing the object. On a distributed memory machine, two alternatives exist; a) pass the stiffness matrix around from processor to processor or b), all of the processors can be programmed to send their element contributions to a given processor that will update the global matrix. In general, both of these processes degrade overall performance considerably.

If the stiffness matrix can subdivided into smaller physical objects like submatrices, the potential for concurrency is improved because multiple processors can simultaneously update different parts of the stiffness matrix. This approach does not eliminate the data coherence problem because potentially there will always be submatrices that must be accessed by more than one processor.

In distributed memory systems, concurrent operations on the stiffness matrix can only proceed if the matrix is split into smaller objects, thereby permitting different parts of the stiffness matrix to migrate to various processors in the network. The engineer is still faced with maintaining data coherence in the program because a given block may be updated by two or more processors. Maintaining data coherence in a distributed memory machine is much more difficult to accomplish than in a shared memory machine because the address space is fragmented. This implies that a given processor must unequivocally establish that no other processor is using the object that is about to be modified. This complicates programming the application considerably.

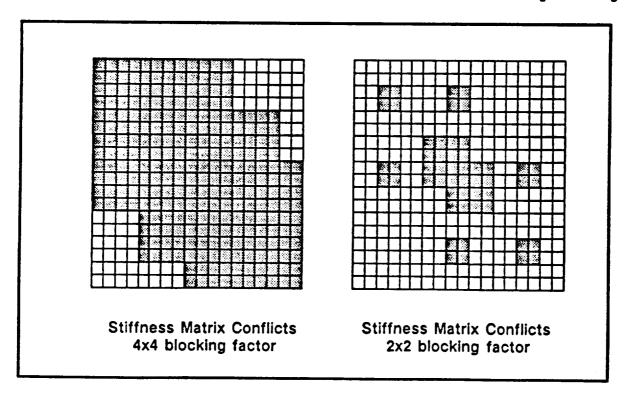

If a data object is subdivided into blocks, how large should the blocks be? The disadvantage of using large blocks instead of smaller blocks is the greater potential for a conflict to occur. The disadvantage of using smaller blocks instead of larger blocks is the increased

overhead of managing more data objects. Figure 2.4–2 illustrates the differences between using small and large blocks for the sample problem described in figure 2.4–1. The figure shows the effect of using two different block sizes. When the two by two blocking factor is used, fewer conflicts occur than in the four by four scheme.

Hierarchical data structures that can support multiple levels of data granularity are ideally suited for parallel computation because the concurrency can be exploited at many levels.

#### 2.5 DATA AND MEMORY MANAGEMENT

Forming and managing the complex data structures that result when a programmer segments large data objects is called data base management. It consists of two parts; managing the logical data structures, and managing the memory that holds the data objects.

Data and memory management are problems encountered with serial as well as parallel systems. Most engineering programmers have difficulty with problems requiring large data spaces. The data spaces envisioned for the future are two orders of magnitude larger

Figure 2.4-2 Data Conflicts for the sample problem of figure 2.4-1

than for today's problems; the fact that programmers may need to handle a disparity of memory types complicates the problem further.

It is important to recognize that engineering data base management is not the same as classical data base management as described in the computer science text books. Engineers must work with complex array structures – not simple relations and tuples. Engineers typically create a large data space in a short period of time; rapid access and high throughput are very important. The data space often disappears immediately after problem solution. Classical DBMS deals with large data spaces built over time and maintained forever. Security and longevity are very important.

The mappings inherent in classical DBMS are needed to provide flexibility; they are too cumbersome and inefficient for the kinds of engineering problems envisioned herein. Objects must be passed directly to the application. This results in some loss in flexibility and security; these disadvantages are offset by corresponding gains in throughput.

### 2.6 OTHER FACTORS INFLUENCING PERFORMANCE

There are several performance factors that must be considered when developing parallel programs [77]. These factors are unique to the machine. They are:

- computational bandwidth: how fast data can be processed by the cpu,

- memory bandwidth: how fast data can be processed by the memory.

- communication bandwidth: how fast data can be processed by the interconnection network,

- cache memory or vector registers: high speed buffer areas.

- and the amount of primary and secondary storage.

When developing a parallel program, the algorithm can be "fine tuned" to the machine architecture in order to exploit the machine to the fullest potential. References to data objects are programmed in a manner that reflect the memory bandwidth and the organization of the available cache, primary and secondary storage. For distributed memory machines, the communication bandwidth is a very important factor. If is is slow relative to the proces-

sor bandwidth, the program must be designed with a minimal amount of inter-processor communication (message passing).

Since no two machines are likely to have identical specifications, it is reasonable to expect that the performance of a given application on two machines will be different. It is important nonetheless that a given application should be somewhat comparable and easy to port, especially when considering the spiraling costs of software development.

In the future, it will become necessary to develop software that will span different types of machine architectures. Algorithms and data structures must be expressed independently of the architecture.

#### CHAPTER 3

# MIMD ENVIRONMENTAL ISSUES AND NEEDS

This chapter develops the concept of a software environment for MIMD computing. The benefits of using various types of tools that can exist within the environment are analyzed. The pros and cons of the various alternatives are outlined. The language layer approach is selected.

# 3.1 PROGRAMMING ENVIRONMENTS

### 3.1.1 Introduction

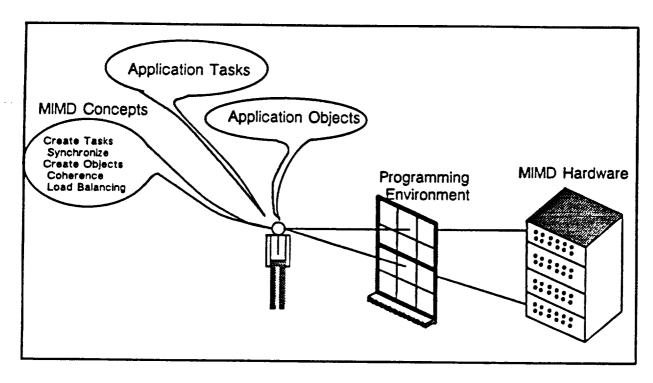

The previous chapter described several factors that need to be considered when developing finite element (engineering in general) software on MIMD computers. The software engineer is responsible for correctly integrating all of these concepts into his system. The magnitude of the problem is expressed visually in figure 3.1.1–1. Engineers can express the application software in terms of mathematical algorithms; they probably can think of it in terms of high level tasks that can be done concurrently, and in terms of the associated data objects; they have some knowledge of the MIMD related problems that were discussed in chapter two. The problem is to synthesize all of that information, and to convert it to a working engineering system on specific MIMD hardware. The mapping from software concept to hardware is accomplished via the programming environment, which acts as the programmers software window to the hardware. Typically, the programming environment delivered with the hardware consists of an operating system, compilers, and various tools to achieve concurrency and parallelism in programs.

On serial computers the "standard environments" are often augmented with broader based environments that are more in tune to specific applications. This chapter will make the case for extending such environments to MIMD systems too.

# 3.1.2 Why We Need a Broader Based Environment

The examples in the previous chapter illustrated that there is a significant amount of large grained parallelism that exists within the finite element method. It is difficult to exploit

Figure 3.1.1-1 Function of the Programming Environment

this type of parallelism without detailed knowledge of the problem. That depth of knowledge is generally not available to compilers — even those capable of performing an extensive data dependency analysis. Consequently, exploitation of this concurrency is generally left to the software engineer. He must simultaneously contend with the engineering problem, all aspects of task control, and all aspects of data and memory management.

The task scheduling mechanisms for loosely-coupled machines are significantly different from those on tightly coupled machines. There is even a disparity within the group of tightly-coupled machines. The data dependency-synchronization approach cannot be incorporated on loosely-coupled systems because of the segmented address space combined with the hardware and communications overhead. Hence, developing portable application codes that exploit this concurrency is a very difficult task. What works on one machine will often not work on another.

In order to overcome these difficulties, an environment that will facilitate developing machine and architecture independent application code is needed. The engineer should be able to express the problem, generic information about concurrency, and which data objects

are to be used, in a procedural language. The environment should provide the engineer with a uniform approach to programming the application on all MIMD computers. The system that supports the language must be responsible for mapping the application to the hardware architecture of the target machine. It should handle the scheduling and synchronization of tasks in addition to resolving data coherence conflicts and managing memory for a variety of hardware architectures. In effect, the programmers view of the system as seen through the window of figure 3.1.1–1 should be invariant and opaque to the hardware behind the window.

Hence, the object of this research is to develop a new programming approach by prototyping a software environment that does all of the above on a distributed memory MIMD system. Unlike most other work in this area that primarily emphasizes task control, data and memory management are treated as crucial aspects of the problem in this concept.

### 3.2 TYPES OF TOOLS IN THE ENVIRONMENT

There are several alternatives for identifying and expressing the concurrency in an existing application developed in a serial programming language. They include:

- modifying / extending the programming language to incorporate the requisite features to express concurrency (e.g. FORTRAN and FORCE[44]);

- developing compilers that are capable of identifying and optimizing the concurrency in the program automatically (e.g. Parafrase [17]);

- re-programming the application using new languages that already have the constructs needed (e.g. ADA) or developing a new programming language.

Various solutions to the first method are presented in [31], [44]. They include the use of a language layer, new library routines, and new constructs and features required to identify concurrency and address the related aspects. McGraw [60] identifies some of the advantages and disadvantages of such techniques; minimal changes are required in the application.

The use of special purpose routines leaves the original language and its compiler untouched. However, the compilers lack of knowledge about how parallelism is being used in

the program results in some difficulties. These difficulties include the analysis of how data is being shared between tasks and, the possibility of incorrect optimization. Furthermore, incorrect code can easily be written because the programmer is only weakly restricted in the ways synchronization constructs and shared data can be used.

The FORCE [44] is an example of a special purpose software tool that is used to exploit concurrency within an application. The FORCE insulates the programmer from process management, however the programmer is responsible for the data coherence issues of parallel programming. The FORCE consists of a set of FORTRAN 77 callable macros that support the parallel execution of DO loops using pre-scheduling and self-scheduling schemes. The FORCE includes constructs to allow for mutual exclusion, synchronization, and/or sequential execution when necessary, and constructs for data based control of execution. In this approach, the programmer is largely responsible for identifying the concurrency within the application.

Another alternative that can be used to identify and express the concurrency within an application program is to extend the programming language by incorporating parallel constructs. Hardware manufacturers provide unique language extensions for the software they support. For example, the language extensions for FORTRAN on the Cray XMP and the ALLIANT are not the same. Hence, language extensions are not standard; neither are they machine or architecture-independent.

Significant efforts have been directed towards developing special compilers that automatically identify concurrency in existing programs [17], [60]. This approach requires the use of an extremely sophisticated compiler. Most of the emphasis of this technique is focused on the analysis of do-loops. The question of how much concurrency the compiler can detect still needs to be answered. This depends on both compiler technology, and the nature of the program being analyzed. The performance of a program depends on detecting data dependencies so that the instructions can be scheduled and synchronized in order to produce correct results while still maximizing the amount of concurrency and vectorization within the program.

A data dependency is an implicit sequential ordering of the access to a data element. The order of access must be enforced to ensure that correct results are obtained. Hence, dependencies can limit the amount of parallelism that exists in a program. Data dependen-

cies are very difficult to detect when multiple levels of subroutine calls are present within the program. This is exactly the problem when identifying coarse-grained concurrency in a program. A well written program will have many levels of subprograms; the potential for concurrency is not obvious to a compiler. In such cases, the programmer has to use compiler directives. The directives assist the compiler in generating the scheduling and synchronization instructions for concurrent operations. Compiler directives, like language extensions, are very machine dependent.

Yet another alternative is to develop the program in a new language e.g. ADA. The use of ADA for scientific applications has also been considered as a viable alternative programming language. Its success within the scientific community depends on whether mathematical and scientific libraries can be developed, and on its future popularity among programmers [73], [84].

Finally, developing a new procedural language can be a formidable task, depending on how sophisticated the language constructs need to be. Such an option is very manpower-intensive and hence extremely expensive. Given the tremendous investment in existing application codes, this option must be viewed either as a last resort, or as a means for developing ideas on how existing systems would gradually "evolve" into structures more amenable for parallel processing. The advantage of developing a new language is that it can be tuned to enhance possibilities for expressing algorithms that contain concurrency. More detailed discussions related to developing a new language can be found in [60]. Since hardware architectures may vary dramatically, it may be very difficult to develop a compiler that will optimize the new language for high performance on each target machine.

None of the approaches described above addresses the issues related to management of the large complex data spaces associated with engineering systems.

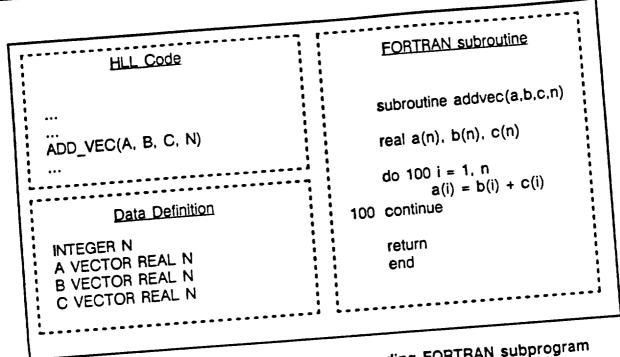

A slight variation on the new language theme is to use a language layer approach. The application is developed using two languages. The first language, a High Level Language (HLL), is both architecture and machine independent. It is used to specify the overall algorithm in terms of tasks, objects used by the tasks, and the potential for coarse grained concurrency of tasks. The HLL program also acts as a driver for routines written in a lower level procedural language.

The "guts" of the program are implemented in a procedural language like FORTRAN. These routines become the workers for the tasks defined in the HLL. They receive data objects as arguments and perform the needed operations. Consistency of data objects and proper task synchronization is guaranteed by the HLL program that invokes the procedural program.

The procedural subprograms can be "fine tuned" to a given machine by taking advantage of the capabilities of the procedural language compiler on the target machine. This can be done by either using compiler directives for the target machine (machine dependent) or by introducing machine independent compiler directives that can be filtered out as the application is moved to a new target computer.

This two level approach provides a number of advantages over the approaches described earlier. Application programs written in the HLL program are machine and architecture independent. They expresses a solution to the application in a manner that would work on any MIMD configuration. Thus it eliminates one of the major objections to using other "more standard" techniques. In addition, since the HLL is specific to the MIMD problem, it can be designed with features that relieve the programmer of the need to consider the details of how tasks are assigned to processors, and how to express the details of the synchronization necessary to make the program work properly. These concepts can be implicitly imbedded in the language constructs, hence the programmer need only concern himself with the application problem. Such language constructs already exist in application languages like SISAL, FP and KRC [60].

The language layer approach is very flexible, permitting one to easily experiment and implement new concepts in the language and the underlying support system. It facilitates the development of prototype systems for MIMD computers. Hence it was the alternative selected for the environment developed herein. The next section describes how the language layer concept has evolved over the years.

### 3.3 EVOLUTION OF LANGUAGE LAYER ENVIRONMENTS

The purpose of the software environment is to provide the programmer with a consistent view of the hardware regardless of what it really looks like. This view is referred to as the virtual machine because such a hardware configuration generally does not exist. The pro-

grammer develops the application program for the virtual machine. The environment is responsible for mapping the program written for the virtual machine onto the actual hardware provided.

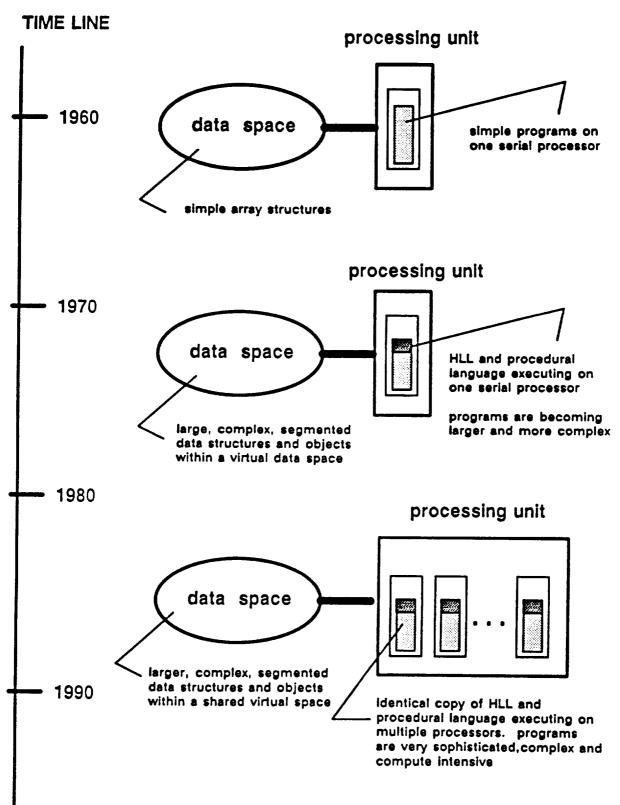

In order to give the reader a better appreciation of what is involved in supporting the programmers view of the system, a brief history of the changes that have taken place puts things in perspective. Figure 3.3–1 illustrates how the programmers view of the system has evolved over the years. It also shows how the language layer concept has evolved based on the engineers need to solve large problems.

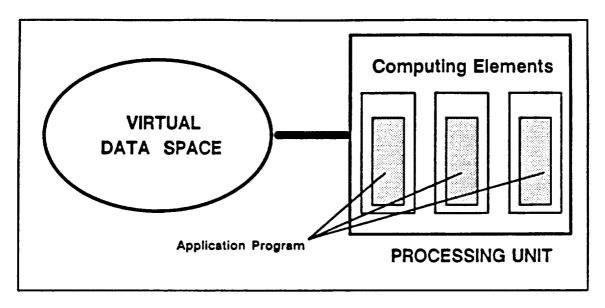

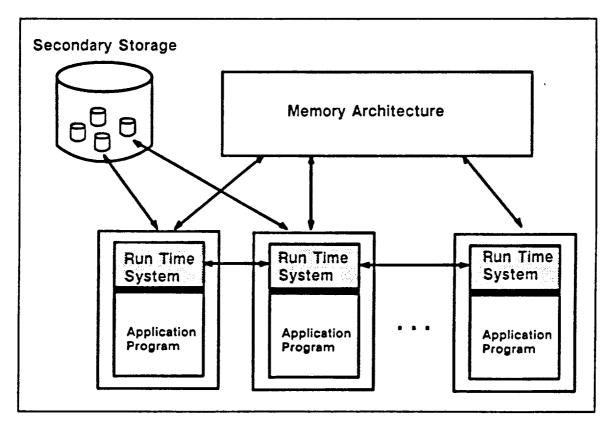

In the 1960's, the view of the hardware consisted of a single processor that operated on data. The processor executed the program and referenced data that resided within a data space. This is shown as the figure at the top of figure 3.3–1. Engineers traditionally programmed their applications in FORTRAN. The engineer's expectation of the computer's capability grew with time; he attacked larger and more complex problems. The programs that had to be developed were more complex and sophisticated. The application problems required the manipulation of large volumes of data — large enough to exceed the storage capacity of main memory by several orders of magnitude.

In order to solve these problems, more complex data structuring techniques were developed and a High Level Language Layer (HLL) was used to access and manipulate data. The data structures were not available in earlier procedural languages. The increased complexity and details of managing data were hidden from the engineer by the environment. The HLL served as an interface between the procedural subprograms and the new sophisticated data structures. Conceptually, operations in the HLL were mapped to procedural subprograms as shown in the simple example illustrated in figure 3.3–2.