# Design and Initial Application of the Extended Aircraft Interrogation and Display System

Multiprocessing Ground Support Equipment for Digital Flight Systems

Richard D. Glover

(NASA-TM-86740) DESIGN AND INITIAL N87-16820

APPLICATION OF THE EXTENDED AIRCRAFT

INTERFOGATION AND DISFLAY SYSTEM:

MULTIPROCESSING GROUND SUPPORT EQUIPMENT FOR Unclas

DIGITAL FLIGHT SYSTEMS (NASA) 93 p CSCL 01C G3/05 44002

January 1987

# Design and Initial Application of the Extended Aircraft Interrogation and Display System

Multiprocessing Ground Support Equipment for Digital Flight Systems

Richard D. Glover Ames Research Center, Dryden Flight Research Facility, Edwards, California

1987

National Aeronautics and Space Administration

Ames Research Center

Dryden Flight Research Facility

Edwards, California 93523-5000

# CONTENTS

| Pag                                                      |

|----------------------------------------------------------|

| LIST OF TABLES                                           |

| LIST OF FIGURES                                          |

| LIST OF SCREEN DISPLAYS                                  |

| SUMMARY                                                  |

| INTRODUCTION                                             |

| NOMENCLATURE                                             |

| DESIGN OBJECTIVES                                        |

| SUMMARY OF REQUIREMENTS                                  |

| SYSTEM HARDWARE OVERVIEW                                 |

| FUNCTIONAL DESCRIPTION                                   |

| SOFTWARE OVERVIEW                                        |

| MAINTENANCE PROCESSOR SOFTWARE                           |

| PERIPHERAL PROCESSOR SOFTWARE                            |

| REAL-TIME PROCESSOR SOFTWARE                             |

| CENTRAL PROCESSOR XAIDS JOB SOFTWARE                     |

| XAIDS-USER INTERFACES OVERVIEW                           |

| XAIDS CONFIGURATION FOR X-29A PROJECT SUPPORT            |

| OPERATION OF THE X-29A XAIDS                             |

| GUIDE FOR THE PROSPECTIVE XAIDS OWNER                    |

| FUTURE XAIDS DEVELOPMENTS                                |

| CONCLUDING REMARKS                                       |

| APPENDIX A - PROTOTYPE REMOTE DATA ACQUISITION SUBSYSTEM |

| APPENDIX B - XAIDS SYSTEM INTERRUPT UTILIZATION          |

| APPENDIX C - RTPRO RAW DATA PROCESSING ALGORITHMS        |

| APPENDIX D - RTPRO USER SUPPORT SUBROUTINES              |

| APPENDIX E - CENPRO USER SUPPORT SUBROUTINES             |

| REFERENCES                                               |

| TABLES                                                   |

| FIGURES                                                  |

| DISPLAYS                                                 |

# PRECEDING PAGE BLANK NOT FILMED

## LIST OF TABLES

- Table 1. XAIDS baseline board complement

- Table 2. XAIDS bus memory mapping

- Table 3. XAIDS bus I/O mapping

- Table 4. RTPRO channel declaration structure

- Table 5. RTPRO data acquisition block structure

- Table 6. RTPRO raw data type declaration structure

- Table 7. RTPRO function generator block structure

- Table 8. CENPRO command declaration structure

- Table 9. CENPRO scratch diskette directory

- Table 10. CENPRO display format declaration structure

- Table 11. Symbol table entry block structure

- Table 12. CENPRO data display item block structure

- Table 13. CENPRO make page display template

- Table 14. CENPRO free form display template

- Table 15. CENPRO RDAS function generator template

- Table 16. ASCII editor entry block structure

- Table 17. X-29A interface channel board complement

- Table 18. XAIDS to RDAS message structure

- Table 19. RDAS to XAIDS reply structure

- Table 20. XAIDS-RDAS packet formats

- Table 21. XAIDS bus interrupt allocation

- Table 22. XAIDS CENPRO interrupt assignments

- Table 23. XAIDS RTPRO interrupt assignments

- Table 24. XAIDS PERPRO interrupt assignments

- Table 25. XAIDS maintenance processor interrupt assignments

PRECEDING PAGE BLANK NOT FILLED

# LIST OF FIGURES

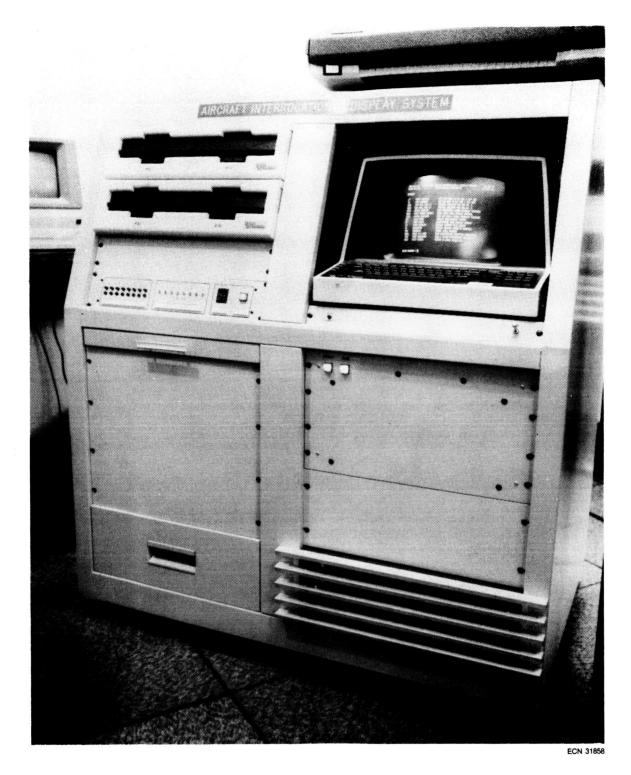

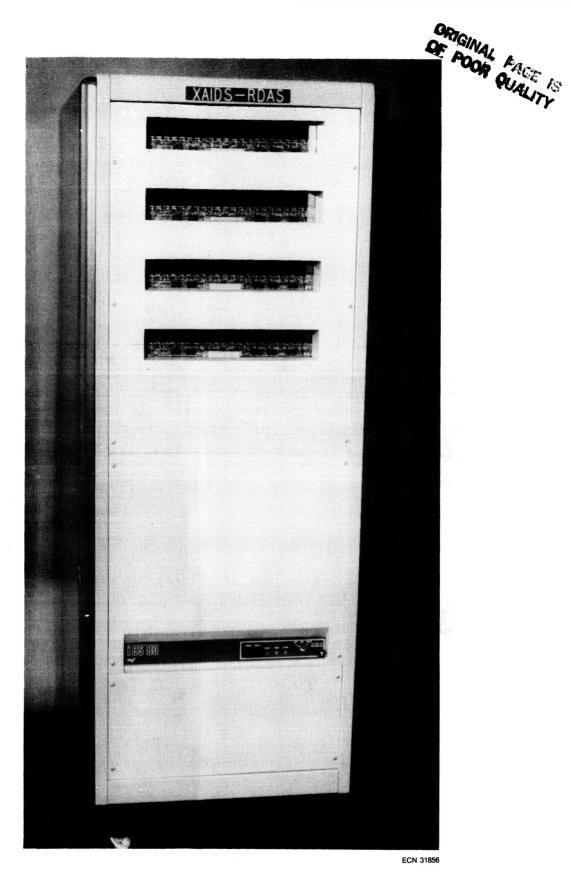

- Figure 1. Extended aircraft interrogation and display system.

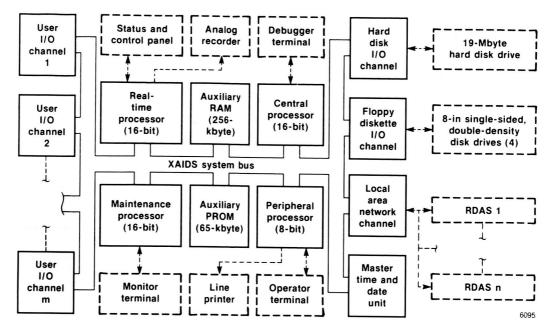

- Figure 2. XAIDS system overview.

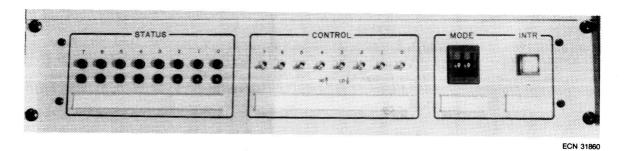

- Figure 3. XAIDS status and control panel.

- Figure 4. XAIDS input-output panel.

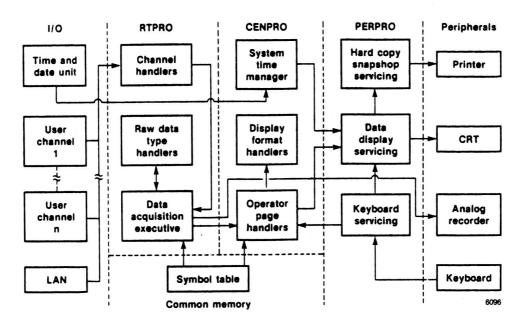

- Figure 5. XAIDS functional interfaces.

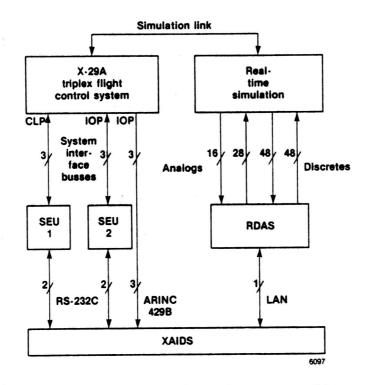

- Figure 6. XAIDS interfaces to X-29A project systems.

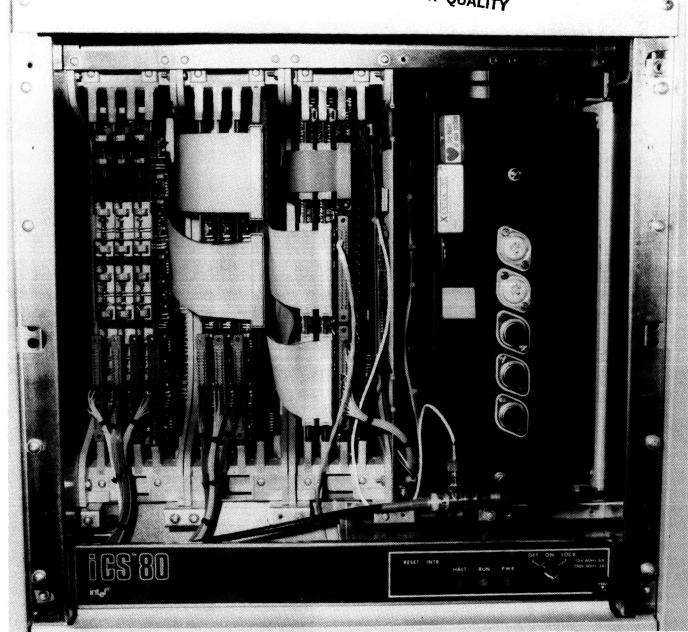

- Figure 7. XAIDS cardcage.

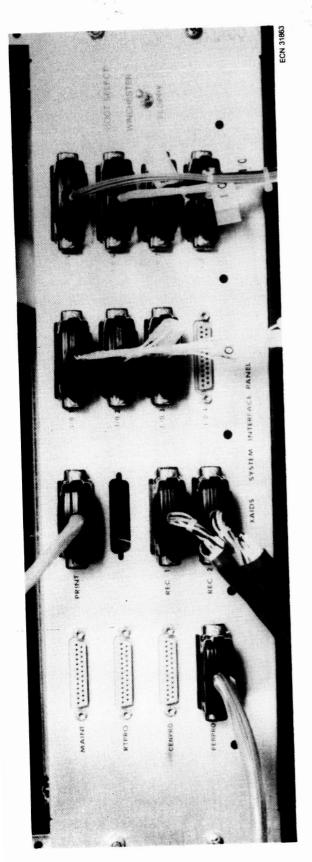

- Figure 8. XAIDS system interface panel.

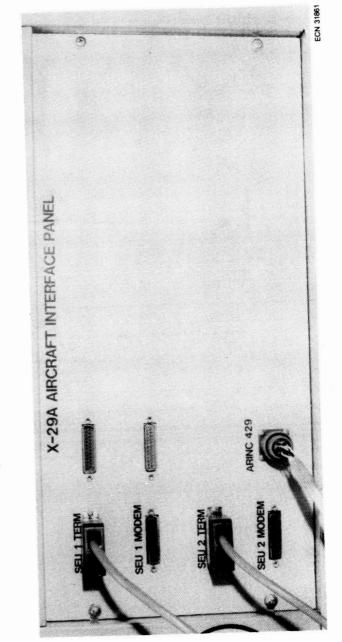

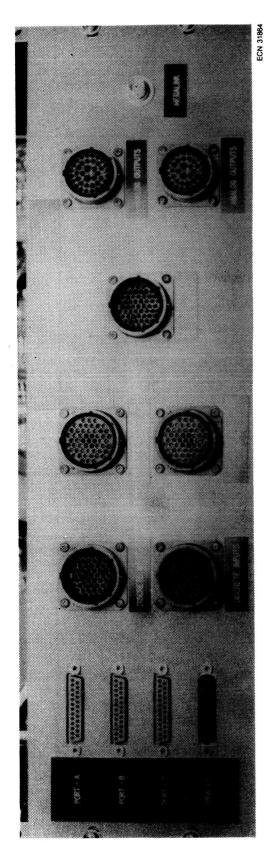

- Figure 9. XAIDS X-29A aircraft interface panel.

- Figure 10. Remote data acquisition subsystem.

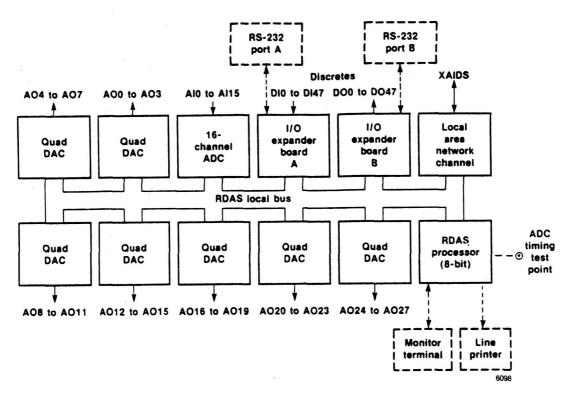

- Figure 11. RDAS overview, X-29A configuration.

- Figure 12. RDAS cardcage.

- Figure 13. RDAS user input-output panel.

- Figure 14. XAIDS-RDAS data exchange.

PRECEDING PAGE BLANK NOT FILMED

# LIST OF SCREEN DISPLAYS

- Display 1. Main command menu.

- Display 2. TEST command menu.

- Display 3. RU command display.

- Display 4. QT command display.

- Display 5. PTCH command menu.

- Display 6. PTCH command edit display.

- Display 7. GAIN command display.

- Display 8. GAIN command help page.

- Display 9. Example MP-driven display.

- Display 10. MP command help page.

- Display 11. Example FF-driven display.

- Display 12. Example FF setup page.

- Display 13. FF command help page.

- Display 14. Example FF command list to CRT.

- Display 15. DK command menu.

- Display 16. Example DK view display.

- Display 17. SYM command menu.

- Display 18. Example SYM edit page.

- Display 19. BAUD command display.

- Display 20. CAL command display.

# PRECEDING PAGE BLANK NOT FILMED

A pipelined, multiprocessor, general-purpose ground support equipment for digital flight systems has been developed and placed in service at the NASA Ames Research Center's Dryden Flight Research Facility. The design is an outgrowth of the earlier aircraft interrogation and display system (AIDS) used in support of several research projects to provide engineering-units display of internal control system parameters during development and qualification testing activities. The new system, incorporating multiple 16-bit processors, is called extended AIDS (XAIDS) and is now supporting the X-29A forward-swept-wing aircraft project. This report describes the design and mechanization of XAIDS and shows the steps whereby a typical user may take advantage of its high throughput and flexible features.

#### INTRODUCTION

Several years ago, the NASA Ames Research Center's Dryden Flight Research Facility (Ames-Dryden) undertook the development of a microprocessor-based, user-programmable, general-purpose ground support equipment (GSE) called the aircraft interrogation and display system (AIDS) (ref. 1). This development was spurred by the need for a research tool to support digital flight systems integration, software verification and validation, pre- and postflight testing, and system maintenance. Prior to that time, special-purpose GSE was procured for each project, resulting in a multiplicity of different types of equipment having various capabilities.

The original AIDS design was an 8-bit unit used to support F-8 digital fly-by-wire (F-8 DFBW) flight software verification and validation (V/V). This was followed by a second unit built to support highly maneuverable aircraft technology (HiMAT) flight control computer testing and systems integration. Success with these early units led to the construction of more units for application to other projects (ref. 2). Although users universally praised the utility of the AIDS, many suggestions for improving system capabilities were offered, leading ultimately to the development of an extended AIDS (XAIDS). The overall design objectives for the new system forced this development effort to take an entirely new approach, which produced a system mechanization believed to be the first of its kind. In addition, an auxiliary system called the remote data acquisition subsystem (RDAS) was designed to permit the user to extend the capability of a basic XAIDS as the application may require.

The XAIDS and RDAS are both designed to be high-bandwidth real-time systems and can support both open- and closed-loop applications. As an engineering-units data display system, the user taps into the target system at the desired data flow point, and the XAIDS passively acquires data and drives operator-specified displays. Another open-loop application could be as an excitation generator to support response testing of the target system. Closed-loop applications include real-time simulation support with interfaces to either an iron bird or an actual aircraft. Such simulations could, for example, generate faulty dynamic sensor signals to allow testing of redundancy management in multichannel systems. Another area of possible closed-loop application is the interactive control of other GSE, permitting centralization of control to a single workstation.

This report will discuss first the generic XAIDS system hardware and software, pointing out features intended to simplify user interfaces. Then the X-29A forward-swept-wing aircraft testing application will be discussed from the standpoint of the user's dual responsibility for engineering compatible add-on hardware and developing necessary software extensions. Examples of typical operator displays will be shown, and an overview of basic procedures will be presented. A description of the prototype RDAS will be presented in appendix A.

# NOMENCLATURE

ADC analog-to-digital converter

AIDS aircraft interrogation and display system

ARINC Aeronautical Radio Incorporated

BIOS basic input-output system

CENPRO central processor

CLP control law processor

CPU central processing unit

CRT cathode ray tube display

DAC digital-to-analog converter

DK diskette

EEPROM electrically erasable programmable read-only memory

FF free form

GSE ground support equipment

HDLC high-level data link control

IEEE Institute of Electrical and Electronic Engineers

INTR interrupt pushbutton

I/O input-output

IOP input-output processor

ISO International Standards Organization (U.N.)

LAN local area network

LED light-emitting diode

MAINT maintenance processor

MDS microcomputer development system

MP make page

NDP numeric data processor

NMI nonmaskable interrupt

PERPRO peripheral processor

PROM programmable read-only memory

PTCH patch manager

RAM random access memory

RDAS remote data acquisition subsystem

RETMA Radio-Electronics-Television Manufacturers Association

RTPRO real-time processor

SCP status and control panel

SDLC synchronous data link control

SEU system evaluation unit

TDU time and date unit

UDI universal development interface

USART universal synchronous-asynchronous receiver-transmitter

V/V verification and validation

XAIDS extended aircraft interrogation and display system

## DESIGN OBJECTIVES

The fundamental objective of the AIDS-XAIDS family of general-purpose GSE was to provide an aircraft control system research tool that could support a variety of projects with minimum reconfiguration of hardware and software. The approach taken was to provide a baseline host system to which could be added application-dependent hardware and software to meet specific needs. The success of this approach hinged on the baseline hardware providing a minimum of constraints on hardware additions and the baseline software providing a user-friendly environment within which software extensions could operate. These goals were not well met in the AIDS mechanization, and the second-generation XAIDS effort was aimed at broad improvements in both hardware and software flexibility.

In general, the design objectives for the XAIDS closely paralleled those for the AIDS. These included mobility, flexible input-output (I/O), a common core of generic support software, user-oriented displays, commercial components used wherever possible, and integral maintenance support. Several years of operational experience with AIDS showed that numerous major improvements were desirable, leading to the formulation of the following XAIDS design objectives:

# User hardware extensions

- -More cardcage slots available for user boards

- -Multiple bus master capability

- -Both 8- and 16-bit data bus operations allowed

- -Larger memory and I/O mapping space

- -More user interrupt lines available

- -I/O extension via local area network

# User software extensions

- -Simplified interfaces to baseline software

- -Structured extensions to ease customizing

- -Larger support libraries

- -Resident software development capability

- -High-order languages available

# Baseline environment

- -Improved operating system

- -Higher system throughput

- -Symbolic parameter referencing

- -Mass data storage and retrieval

- -Faster printer with upper- and lowercase

- -Dedicated analog recorder digital-to-analog converters (DACs)

- -Operator control of screen refresh rates

- -Status and control panel for process management

- -Automatic date and time tagging

# Maintenance and troubleshooting

- -Full-time operating system debugger

- -Full-time maintenance monitor

# SUMMARY OF REQUIREMENTS

It was decided at the outset of the XAIDS effort that the listed design objectives could best be met by a distributed system having multiple processors permitting pipelining of concurrent operations. The choice of system bus was somewhat arbitrary since several bus architectures would have served, but the Institute of Electrical and Electronic Engineers (IEEE) Standard 796 Bus Specification was chosen since it offered the widest choice of compatible hardware and software components on the open market. An analysis of the throughput of such a system showed that 16-bit processors would be adequate, assuming that hardware floating-point processing were included. The choice of the 8086 microprocessor with the companion 8087 numeric data processor (NDP) gave the desired throughput. The remaining objectives were easily met within this basic environment.

One important carryover from AIDS was its central processor board, for which a considerable amount of operator I/O software had been developed. This 8-bit board, with the AIDS operator I/O software placed in programmable read-only memory (PROM), was to become the intelligent I/O channel for XAIDS operator peripherals. The final detailed requirements are summarized as follows:

```

IEEE-796 system bus

-20-bit memory mapping (1 megabyte)

-16-bit I/O mapping

-16-bit-wide data path

-Parallel priority resolution

-Eight bus interrupts

-21-slot cardcage; 3/4-in spacing

-System reset pushbutton

-Pushbutton for interrupt INTO/

-Switching power supply (45 A at 5 V)

Multiple processors

-Central processor (8086 plus 8087 NDP)

-Real-time processor (8086 plus 8087 NDP)

-Peripheral processor (8085); carryover from AIDS

-Maintenance processor (8086); no NDP required

Peripheral I/O devices

-19-megabyte hard disk drive

-Four double-density floppy drives (8 in)

-19,200-baud operator terminal; 24 lines by 80 columns

-Line printer; upper- and lowercase; paper width up to 15 in

-16 DACs dedicated to analog recorder outputs

-Status and control panel (SCP)

-Eight light-emitting diode (LED) indicators

-Eight debounced high-low switches

-00 to FF hexadecimal thumbwheels

-Manual interrupt pushbutton

Local area network (LAN) controller

-International Standards Organization (ISO) X.25 high-level data link

control (HDLC) and synchronous data link control (SDLC) protocols

-1-megabit/sec data rate

-Phase-locked loop clock recovery

-Modem capable of driving 5000 ft of bus cable

Operating system

-Complete 8086-based multitasking system

-Custom device drivers for printer and operator terminal

-Utilities for boot loading satellite processors

-IEEE-796 bus slave loader

-LAN remote slave loader

-Full-time debugger

-Must support software development tools

```

Time and date unit (TDU)

- -Julian calendar

- -Self-contained rechargeable battery

- -Initializes operating system at power-up

- -Peripheral processor (PERPRO) interface for data time tagging

- -Utility program for resetting time and date

Resident software development support

- -Text editor

- -Languages: Assembly, FORTRAN, Pascal, PL/M

- -Utilities for linking, locating, and library functions

# SYSTEM HARDWARE OVERVIEW

Figure 1 shows the general appearance of the two-bay XAIDS console. It is mounted on wheels for mobility and requires 120-V single-phase power from a standard wall outlet. Power consumption is approximately 1200 W, and numerous blowers within the console provide ample cooling even in non-air-conditioned hangar and ramp areas.

Figure 2 shows an overview of the XAIDS bus architecture; each solid-outline box represents a board plugged into the 21-slot large cardcage carrying the system bus. Four processors form the baseline complement: the central processor (CENPRO), the real-time processor (RTPRO), the peripheral processor (PERPRO), and the maintenance processor (MAINT). Mass storage is provided by a 19-megabyte hard disk drive plus four floppy diskette drives each providing 0.5 megabyte on single-sided double-density diskettes. A local area network (LAN) controller provides a 1-MHz serial addressable interface using synchronous data link control (SDLC) protocol. This LAN is currently configured to interface with the prototype RDAS described in appendix A. The prototype RDAS bears address 01; additional RDAS units may be added as user requirements dictate. A time and date unit (TDU) board provides clock and calendar readouts to the operating system and contains batteries to sustain time-keeping even when the XAIDS is powered down. The line printer and operator terminal are permanent peripherals and provide the basic operator interfaces.

An additional permanent feature of the baseline XAIDS is the status and control panel (SCP), shown in figure 3. This unit is interfaced to the RTPRO and provides a general-purpose operator interface. Eight light-emitting diode (LED) indicators are provided for visual readout; each LED has a monitoring jack suitable for oscilloscope monitoring of its drive signal. Eight switches with debounced contacts are provided for generating high-low input discretes, and two hexadecimal thumbwheels provide another 8-bit input register. The interrupt (INTR) pushbutton is debounced and generates one RTPRO interrupt each time it is actuated. Since the thumbwheels are not debounced, it is usually desirable to use the INTR pushbutton to generate a software snapshot of the setting of the thumbwheels.

The analog recorder outputs from the XAIDS are driven by 12-bit digital-to-analog converter (DAC) units on RTPRO. There are 16 channels of -5 to +5 V accessed through two connectors on the XAIDS I/O panel, shown in figure 4. This panel, located at the lower right rear of the console, provides the mounting for the LAN interface connector.

Table 1 shows the board complement for the baseline XAIDS. The CENPRO serves as the host for the RMX86 operating system, which resides partly in PROM and partly in random access memory (RAM). The two auxiliary memory boards (the auxiliary RAM board and the auxiliary PROM board) serve to augment, respectively, the RAM and PROM found on CENPRO proper. The nine empty slots are reserved for user-selected I/O channel boards that provide the hardware interface to the user's target system. The RTPRO and the LAN channel board both require two slots because of the aboveboard height of the piggyback modules they carry. Appendix B details the assignment of interrupts throughout the system, including those on the bus and on RTPRO reserved for the user.

#### FUNCTIONAL DESCRIPTION

At system power-on, the XAIDS begins an automatic bootstrap load operation that ends with the operating system (described later) in control of CENPRO. The operating system is configured for a single resident user (assigned number 1) who is given access to the operating system through the human interface by means of the operator terminal. This allows the XAIDS operator to access all the resources of the operating system, including editors, language processors, and software development utilities, by entering commands on the terminal keyboard. It also allows the operator to load and execute custom utilities and other jobs (called I/O jobs) that have been created (by NASA) to make the hardware perform desired user functions. One of these custom I/O jobs is the XAIDS executive, which has been previously configured to service a particular XAIDS application (although a non-user-specific "default" version also exists for test purposes). It is loaded by entering the command XAIDS, at which time it takes control of the hardware and remains in control until the operator forces an exit back to the RMX86 operating system.

During the time the XAIDS I/O job is running, the system takes on the character of the pipelined multiprocessor architecture shown in figure 5. The arrows show the direction of information flow during a typical data acquisition and display cycle. Data flow in general from left to right in the figure, with the vertical dashed lines demarcating the five stages of the pipeline. The symbol table shown at the bottom of the figure is the one element of the system that is not directly part of the pipeline but is rather a data base for XAIDS supervisory software.

The I/O channel boards shown at the left of the figure constitute the first stage of the pipeline. The TDU and LAN are considered baseline system channels. The system, when configured for a specific user, will normally have one or more user I/O channel boards as well. The essential function of this I/O complement is to interface external equipment to the IEEE-796 bus, with the one exception of the TDU, which is self-contained. The I/O channels may fall into one of three categories: nonintelligent slaves (such as the TDU), intelligent channels executing onboard firmware (such as the LAN), and intelligent channels executing software that must first be loaded into onboard RAM. A bootstrap loader utility has been created that can load any channel having in firmware the required startup routine.

The next stage is RTPRO, which handles any and all time-critical functions associated with the user application. It is loaded using the bootstrap loader utility mentioned previously and is responsible for I/O channel management, raw data preprocessing, and analog recorder servicing, in addition to any user-supplied real-time

routines. The channel handlers provide a standard interface to the data acquisition executive and may be executed either polled or interrupt-driven. Notice that the TDU does not have a channel handler, because it is polled from CENPRO. The data acquisition executive is responsible for all data flow within RTPRO and services two separate structures, one for the analog recorder interface (high speed) and the other for the operator display (on demand). It is supported by a set of raw data type handlers that perform parameter type conversion to NDP-compatible formats. Parameter mapping and type conversion specifications are fetched from the symbol table as required.

The third pipeline stage is CENPRO, which under the XAIDS I/O job is given the main task of interpreting and carrying out operator commands. This requires it to exercise control over both RTPRO and PERPRO while carrying out baseline tasks as well as servicing whatever user-defined commands are present. For data acquisition and display, the operator will normally load a previously created display page from floppy diskette. The display page handler will then perform page setup: fetch information as required from the symbol table, create a display control structure, set up the RTPRO data acquisition executive, and initialize PERPRO to drive the display. It then serves as the intermediary between RTPRO and PERPRO, fetching data as required and formatting each parameter in turn using the display format handler routines. In addition, CENPRO has the ongoing task of periodically polling the TDU and sending updated time and date information to PERPRO.

The PERPRO, the fourth stage in the XAIDS pipeline, uses firmware to manage the digital peripherals of the fifth stage, namely, the operator keyboard, cathode ray tube (CRT) display, and the line printer. The PERPRO provides line-edited operator input strings from the keyboard in several formats, checking for error locally before sending the string on to CENPRO for interpreting. The PERPRO also drives the CRT in several output modes, including the cursor-vectored high-speed refresh mode normally used for data displays. It responds to operator keyboard command sequences to select the desired screen refresh period from 0.1 to 1.5 sec. It also responds to a special keyboard command to snapshot the screen buffer and send it to the line printer buffer for editing and dumping to printer. Both the screen displays and the printer dumps are tagged with the current date and time of day to the nearest second.

# SOFTWARE OVERVIEW

The XAIDS software suite may be broken into three major categories. The largest body of software is the commercial operating system, which was purchased from the Intel Corporation and configured for the XAIDS architecture. The second category is the XAIDS baseline software complement (generic, user independent), which includes a mix of firmware (PROM-resident) and RAM-resident modules for the four system processors. The third category contains the user-dependent software modules, including two RAM-resident packages, one for the CENPRO and one for the RTPRO, plus whatever firmware or software is required to support the user I/O boards. All processors in the system (including user I/O boards) have PROMs containing firmware that begins executing when power is applied. The CENPRO and RTPRO (and usually the user I/O processors as well) are then automatically loaded with software from the hard disk drive.

Table 2 shows the mapping of the various XAIDS system elements within the memory space accessible through the IEEE-796 bus using 20-bit addressing. Three-fourths of the available 1 megabyte of memory domain are occupied by the CENPRO RAM, the auxiliary RAM board, and the RTPRO RAM in three contiguous 256K blocks. The remaining space is allocated as shown to the LAN controller, PERPRO RAM, user I/O, and auxiliary PROM. The uppermost 64K block is not used. Table 3 shows the mapping of system elements within the I/O address space, which is a separate 64K domain paralleling the memory-mapped domain. Notice that the TDU decodes only the lower 8 bits of the I/O address and thus is aliased into 256 separate 8-byte blocks within the domain. Such a mix of address decoding is acceptable only because none of the 16-bit I/O-mapped devices impinge on these multiple blocks.

The operating system software currently used in the XAIDS is the Intel iRMX86 release 5, to which has been added custom device drivers for the TDU, line printer, and operator terminal. The operating system is given exclusive access to the entire CENPRO RAM as well as the entire auxiliary RAM board. A portion of the total operating system is contained in PROMs on CENPRO proper, a portion is resident on the auxiliary PROM board, and the remainder is loaded from the hard disk drive into CENPRO and auxiliary RAM during the bootstrap load operation. The Intel-supplied bootstrap loader firmware was slightly modified to permit switch selection of either the normal hard disk boot mode or a backup bootstrap mode using one of the four floppy diskette drives.

The total operating system is a full-up configuration incorporating all the Intel-provided release 5 options, including the universal development interface (UDI). The UDI serves as the host for the software development tools available to the operator through the human interface command interpreter. Another permanent feature of the operating system is a full-time RMX86 debugger, which may be accessed while the system is executing without disturbing current job execution. To use the debugger, a separate terminal set for 9600 baud must be mated to the CENPRO connector on the system interface panel inside the left rear of the XAIDS cabinet. The debugger, activated with the single keystroke command <cntl D>, permits examination of the entire spectrum of operating system objects. This tool is invaluable for assessing system allocation of resources (especially memory) and is the only means whereby such system problems as task deadlock can be diagnosed. The debugger is deactivated by entering Q <return>.

When the operating system begins to execute following completion of the bootstrap load process, the human interface submits the log-on file (pathname :prog:r?logon), causing the operating system to perform the steps specified. This text file is created using the system text editor and can perform any system functions desired by the user. Currently this file is configured to first load the RDAS through the LAN using a system utility program called RBOOT. The final step is the loading of the XAIDS executive program (called XAIDS), which in turn handles the loading of user boards and RTPRO. This logon file thus completes the automatic bootstrap process, which begins when the XAIDS is powered up, and takes the user directly to the XAIDS executive command list interpreter.

The operator is given the freedom to return to the RMX86 human interface whenever desired by entering the XAIDS command EXIT. While running under the human interface, several XAIDS utilities are available to the operator: the RDAS loader (RBOOT), the slave loader (BOOT), and the TDU setup program (TCU). Program RBOOT

permits the operator to reload the RDAS as required. If the RDAS has previously been loaded, the RBOOT commands RDAS to dump its load and the new program is then loaded. The utility BOOT allows the operator to "manually" load a slave processor, rather than have the XAIDS executive do it. If the slave has already been loaded, BOOT aborts the load process with an appropriate error message. The INTO pushbutton can be used to send an interrupt, forcing all slaves to purge previously loaded programs so that BOOT can be used to reload one or more of them. The utility TCU permits the operator to reset the time and date registers of the TDU as required to correct for drift or to permit daylight saving time or standard time adjustments. The operator may reload the XAIDS executive at any time by entering the human interface command XAIDS.

#### MAINTENANCE PROCESSOR SOFTWARE

The maintenance processor (MAINT) is a 16-bit single-board computer configured as a bus master that is designed to access the entire IEEE-796 bus including both the memory-mapped and the I/O-mapped domains. The current MAINT program is resident in onboard PROMs and provides most of the features usually found in a monitor program, including memory read-write and I/O read-write. A separate terminal, which is connected to the system interface panel inside the XAIDS rack (accessible through the left rear door), is required to use MAINT. This terminal may employ any baud rate in the range 110 to 19,200. When the XAIDS is powered up, the MAINT firmware enters a lockon loop, which senses one or two capital letter U keystrokes to determine the baud rate. The program then displays a command menu including an H (help) command, whereupon the operator may perform any desired system troubleshooting operations. Until the program is called upon to examine or alter system-mapped hardware or software, no bus operations are involved, and there is thus no loading of the system. A purely passive function performed by MAINT starting at power-up is the monitoring of the eight bus interrupts; when sensed, each causes a counter to be incremented. These eight counters may be displayed on the maintenance terminal whenever desired.

# PERIPHERAL PROCESSOR SOFTWARE

The peripheral processor (PERPRO) is an 8-bit single-board computer configured as a bus slave that services the operator CRT and keyboard, the line printer, and the bus timeout light on the panel below the operator terminal. The PERPRO software is resident in onboard PROM and executes in three separate modes: reset, RMX86 I/O, and XAIDS. Communication with PERPRO is accomplished through PERPRO RAM control structures that are accessible to any bus master through the system bus (memory-mapped domain). When the system is powered up, PERPRO firmware begins executing immediately, performing an initialization sequence, entering reset mode, and displaying a sign-on message on the CRT. Whenever the human interface is running in CENPRO, the PERPRO switches to RMX86 mode, in which the CRT, keyboard, and line printer become I/O devices belonging to the operating system. If the XAIDS executive is loaded, the PERPRO mode switches to XAIDS, during which the firmware responds to numerous specialized commands for keyboard input sequences, screen display functions, and line printer operations (including screen snapshot) that are

not available in RMX86 mode. These special functions are tailored for high-speed support of the XAIDS page displays at refresh rates up to 10 Hz.

#### REAL-TIME PROCESSOR SOFTWARE

The real-time processor (RTPRO) is a 16-bit single-board computer configured as a bus master that directly services the analog recorder DAC outputs, the SCP, and an RS-232 serial port. The RTPRO software consists of two elements: a startup package resident in onboard PROM and a RAM-resident load module that is downloaded either by the BOOT utility or by the XAIDS executive. When the system is powered up, the firmware begins executing immediately and waits until a RAM-resident module download has been completed. At that time, the firmware passes control to the load module, which will remain in control unless the INTO pushbutton forces a return to firmware, which permits a reload.

The RTPRO firmware, while waiting for download, performs an SCP test routine permitting the operator to perform confidence tests on the switches, thumbwheels, and INTR pushbutton. If the control switches are all LO, the LEDs are flashed on in slow succession; any control switches placed in the HI position turn on the corresponding LED. When the INTR pushbutton is pressed, the mode thumbwheels setting is logically ORed with the switches and the combination appears on the LEDs.

The RTPRO load module consists of a baseline set of routines linked to the user's real-time routines to form a single entity loaded into the lower portion of RTPRO RAM. The baseline routines provide the following services: LAN servicing, channel management, DAC and CRT data acquisition, and programmable function generation. Supervision of RTPRO by CENPRO is accomplished through control structures in a portion of RTPRO RAM that is reserved as a common data area. The interfaces to the user's routines provide a variety of options that can accomodate a broad spectrum of user requirements including interrupt linkages, timed polling, and background looping.

The LAN servicing provides pipeline management for all data flowing to and from the RDAS. At present, only a single secondary station (01) is tied to the bus, although up to 255 addressable stations may be serviced. As discussed in appendix A, the maximum servicing rate is approximately 96 Hz, although degradation can be expected with high RTPRO loading. During each cycle, all 48 discretes are passed (both ways), 16 analog-to-digital converter (ADC) values are fetched, and all 28 DACs are updated. The data are passed to and from buffers in RTPRO RAM; if a routine requires access to the data stream for either input or output, this is accomplished synchronously using handshake semaphores. In addition to analogs and discretes, serial character streams to and from the RDAS peripherals can be passed using packets attached to the LAN messages. These packets are handled as low-priority traffic to maximize the bandwidth of the analogs and discretes.

Channel management involves the declaration and subsequent supervision of the data acquisition channels, which may number up to 32. Each is identified by a two-character mnemonic and has associated with it a control structure as shown in table 4. The handler for each channel consists of a set of six subroutines whose addresses are provided when the channel is declared. The baseline RTPRO software declares four channels: PP for access to PERPRO RAM, RP for access to RTPRO RAM,

RA for access to RDAS analog inputs, and RD for access to RDAS discrete inputs. All channels, including any the user requires, are declared during RTPRO initialization following download. The baseline software provides routines for the timing, synchronization, and status monitoring of each channel.

The DAC and CRT data acquisition is managed using two large control structures that contain all the information necessary to fetch the data items called for and perform raw data preprocessing. Up to 16 recorder output DAC parameters may be handled, and up to 255 CRT display parameters may be handled. The DAC control structure is scanned at a maximum rate of 100 Hz, although rate degradation is normal depending on RTPRO loading. The CRT control structure is scanned at the screen refresh rate selected by the operator (0.67 Hz to 10.0 Hz). The control structures contain a block of the type shown in table 5 for each parameter. These blocks provide registers for data buffering, constants used in preprocessing, and pointers to the necessary supporting subroutines. As soon as the DAC control structure scan is complete, the DAC values are copied from the structure to the DAC buffer, and the 16 DAC outputs are immediately updated. For the CRT control structure, CENPRO is notified when scan is complete, and CENPRO then fetches from the structure whatever data elements are required to support its screen display formatting.

For both DAC and CRT data acquisition, the subroutines called to perform the data snapshot (copying data from the channel handler) and subsequent processing are embodied in software modules called raw data type handlers. Each data type is identified by a four-character mnemonic and has an associated declaration structure as shown in table 6. The two setup routines are used in the configuration of the CRT and DAC control structures. These routines are responsible for generating the constants embedded in each control block and also for supplying the pointers for the snapshot and processing routines. Up to 64 total raw data types may be declared at initialization time; currently the baseline software declares the 7 types shown in footnote a of table 6. The algorithms employed in the processing routines for these 7 data types are shown in appendix C.

The programmable function generator contained within the baseline RTPRO software permits up to 100 time-varying functions to be generated. The outputs are used to selectively drive RDAS analog and discrete outputs to provide forcing functions to a system under test. The generator is initialized by CENPRO and is clocked by eight separate software timers triggered by the operator using the SCP. Up to 32 function types may be declared at initialization time; currently 10 functions are declared by the baseline software. These are sinusoidal, step, ramp, doublet, pulse, rectangular periodic, triangular periodic, random discrete, shaped white noise, and exponential. The generator is controlled by a large data structure containing for each function a block such as that shown in table 7. When each function is declared, a pointer is supplied for a setup routine that is responsible for initializing the block constants and pointers. The structure is scanned at a maximum rate of 100 Hz, with slower rates to be expected for larger numbers of functions as RTPRO loading increases. However, the timers maintain a uniform time scale even though servicing rates may slow.

# CENTRAL PROCESSOR XAIDS JOB SOFTWARE

The XAIDS executive load module consists of a baseline set of routines linked to the user's extension modules to form a single load-time locatable RMX86 I/O job.

This module is loaded by the logon file during system power-up initialization; it may be later reloaded manually using the operator human interface command XAIDS. At its core is a looping command interpreter that accepts command mnemonics of one to four characters in length and then branches to the corresponding servicing routine, called a command handler. The menu is the combination of the XAIDS baseline command set plus whatever user-defined commands have been declared. The XAIDS executive provides an interface for the overall software suite to the RMX86 operating system for such operations as file reading and writing. In addition to RMX86 I/O, the executive baseline manages the display scratch diskette, several data display formats, a symbol table, two display page handlers, a function generator, and several test modules.

All XAIDS commands with the exception of EXIT are declared by tables consisting of concatenated sets of command declaration blocks such as shown in table 8. A concatenated set of such blocks may be of any length and is delimited by a final block containing blanks in the mnemonic field. Associated with each declared command mnemonic are two ASCII text strings that are used in the menu presentation process. The first is a 20-character explanation of the mnemonic itself while the second is a 45-character description of its function. Also contained in each block is the entry address of the command handler, the address of the scratch file save template (if any), and the length of said template in bytes.

A template is defined as any data structure that is created by a command handler and that can be preserved on diskette and retrieved for later reuse. All templates contain the same initial block of 54 ASCII bytes, the first 4 bytes containing the mnemonic for the associated command handler and the next 50 bytes containing the identifying name for the template. Diskette drive :F3: is reserved for the scratch diskette, which may contain up to 100 numbered files each containing one template. An additional file on the diskette is the so-called scratch diskette directory (not to be confused with the diskette's operating system directory), structured as shown in table 9. The scratch diskette manager has routines for viewing the directory, loading a file, dumping of file groups to printer, deleting a file, copying a file to a backup scratch diskette, and initializing a new scratch diskette. When a fresh diskette is initialized to become an XAIDS scratch diskette, its newly created (empty) directory is given a name, and the date and time of creation is permanently recorded. This directory contains 100 entries for the status information corresponding to diskette files given pathnames 1 to 100. Each entry contains the emptyoccupied status flag, the command mnemonic of the handler associated with the template, the date and time of the save operation, and the title for the template.

Two major PUBLIC routines within the scratch diskette manager handle the saving of templates and the subsequent reloading of templates. The routine that saves a template is invoked from within a command handler and either overwrites a specified file number (1 to 100) or writes to the first available empty file if 0 is the file number. For a typical save operation, the current scratch diskette directory is loaded, the elected file is written, the directory is updated, and the directory is then rewritten. The loading of a template (always specified by file number) invokes the routine that reads the directory from the scratch diskette, determines which handler is involved, retrieves the template, copies it to the handler's buffer, and invokes the handler's servicing routine.

Since the main uses of XAIDS in one way or another involve the display of data, a wide choice of screen display formats has been made available. The executive

manages a set of baseline and user-defined display formatting routines that are declared during the initialization of the executive immediately after load. The formats are declared by blocks such as that shown in table 10. Each format is identified by a single letter that has associated with it the address of the corresponding servicing routine. The eight format types declared by the baseline software are shown. With the exception of M, the letters assigned are identical to those used in FORTRAN format statements. The M (for "message") format causes the display of one of two alternative ASCII strings, each from 1 to 10 characters in length. This format is widely used for displaying the status of a single discrete or a set of discretes within a given parameter.

A central feature of the XAIDS is the use of symbolic parameter referencing through a large structure called the symbol table. This table occupies 64 kbytes in the uppermost portion of RTPRO RAM at bus memory domain address range 0B0000H to 0BFFFFH. The table is alphabetized and can hold a maximum of 510 parameter entries described by blocks such as that shown in table 11. This information is the data base used by both RTPRO and CENPRO in the management of data flow from the channel handlers to the ultimate destination, whether RTPRO DACs or CRT display. The symbol table editor is a routine that manages the symbol table; it can load a new table if required, insert, modify, delete, or clone individual entries in the currently loaded table, attach an identifying name to the table, and store the resulting table on diskette (usually using the default pathname :F3:SYMBOL.TAB). It also controls the printer listing of the table in one of two formats and generates scans of the table on the CRT.

Screen display of data is managed within CENPRO using a table of item blocks such as that shown in table 12. Each parameter to be displayed on the screen requires such a block; each has an index number identifying which element of the RTPRO CRT data acquisition structure is used as the data source. Also specified in each block is the display format, the address of the corresponding formatting routine, the position on the screen of the left edge of the data field, and a copy of the zero-one messages from the symbol table entry for the parameter. The zero-one messages are used only by the M format; they are copied from the symbol table to the structure to reduce bus traffic levels.

Two data display page handlers are provided by the baseline software. The simplest of these is a tabular form called a make page having the template structure shown in table 13. The make page handler displays a maximum of 20 data items, 1 per line, each specified by data source channel code, parameter name, and display format. The format for a line item is usually the default format read from the symbol table but may be a different format in effect for this line item only. The handler accepts whatever title is desired for the page template and can save the template on scratch diskette for later retrieval. Besides being used for data display, this page is used to set up the recorder analog outputs. A subroutine controls the mapping of the first 16 entries of any make page to the RTPRO DACs on a one-to-one basis whenever the page is "latched" to the recorder outputs. Even though the display is exited, the latched configuration will remain in effect until either unlatched or relatched.

The other baseline display page handler, called the free form, has the template structure shown in table 14. The handler for this style page permits unlimited freedom to create a display of whatever form desired occupying screen lines 3 to 23. The template contains an image of the static information or "background" to be

displayed plus data entry blocks for up to 255 entries. Notice that the data item entry structure is slightly different from that used for the make page template since each free form data item must be explicitly positioned. Normally the template would contain a mix of background plus data but may contain only background (thus generating a static display) or may contain only data items (without background). Data items are specified by channel code plus parameter name; the format for each data item is configurable, the title for the page can be whatever desired, and the template can be saved on scratch diskette. One unique feature of this handler is the means to list the data item blocks from the template on either CRT or line printer.

Control of the programmable RDAS function generator within the RTPRO baseline software (discussed previously) is exercised by a command handler having the template structure shown in table 15. Each template defines a "program" specifying up to 100 different functions capable of driving either an RDAS DAC or an RDAS discrete output "channel." Functions may individually drive a channel, may be summed to a channel, or may be time-division multiplexed to a channel. Each function entry specifies the desired output channel, the function name, the timer specification, and the three elapsed times at which the function is to be enabled, triggered, and disabled. The function name correlates to an entry in a function definition table, a tabular data structure loaded from diskette, which specifies the function type (for example, sine) and the arguments characterizing the function. The timer specification for each function determines which of eight timers (controlled by the SCP) is to be used as its time base. This handler can edit the program template, give it a title, save the program template on diskette, define new functions in the function definition table, and cause the current program template to initialize the RTPRO function generator control structure. Once the RTPRO generator is initialized to run mode, it is independent of CENPRO, and the handler may be exited.

The function definition table is an example of a category of data structures called ASCII editor tables. As the name implies, these tables contain only ASCII (that is, text) information and may be employed by any command handler requiring an auxiliary data base in addition to its template. These tables, like symbol tables, exist as operating system files (not numbered scratch files) and temporarily overlay the memory block normally occupied by the symbol table. To distinguish the different table types, all are tagged with the "owner" mnemonic. Therefore all symbol tables are tagged SYM, and a function definition table will always be tagged RDFN. For each type of table, there must be a default pathname permitting the automatic reload of the correct table type as required. The generic ASCII editor routine may be called by any command handler that "owns" an ASCII editor table to permit loading, viewing, listing, modifying, naming, and storing of its table.

The structure of an ASCII editor table entry is shown in table 16. The assignment of fields is determined by the handler owning a particular table. In the case of RDFN's function definition table, the entry name field contains the name of the function, information field 1 contains the function type mnemonic, and information fields 2 to 9 are assigned to various function arguments. Any application that requires a field to contain a numeric constant must encode it in ASCII string form when the entry is created and later decode it when the constant is fetched. This general-purpose structure is suitable for any auxiliary ASCII data base application of up to 510 total entries, provided each entry can be encoded into a name and description field of 32 characters plus 9 information fields of 10 characters each.

The baseline CENPRO software currently contains four test routines. An RDAS test routine generates two-way traffic to the RDAS unit through the LAN, including analog I/O, discretes I/O, and peripherals I/O. There is a routine used primarily in software V/V that permits the generation of numeric constants in various formats anywhere within the memory-mapped domain. Another routine writes to the analog recorder outputs using various periodic waveforms as well as individually controlled calibration test voltage levels. Finally, there is a general-purpose system monitor routine that is similar to the MAINT firmware described earlier except that it cannot tally the IEEE-796 bus interrupts.

### XAIDS-USER INTERFACES OVERVIEW

The central philosophy adopted in the design of the XAIDS was to provide a flexible environment that would permit a prospective user to easily configure the system in ways that could not be anticipated. To make this possible, the interfaces of the baseline hardware and software to the user-supplied extensions have been structured so as to be limited, clearly defined, and easily understood. This approach has been so successful that the design of any XAIDS application is now a straightforward engineering task.

The interfaces that a prospective XAIDS user must deal with can be partitioned into the following categories: cabinet-mounted hardware, cardcage components, cabling, and software. As might be expected, the software area involves the most extensive interfaces and as such usually demands the largest part of the engineering effort. These four areas will be discussed here in generic terms with emphasis on the options open to a user.

The XAIDS cabinet hardware employs standard RETMA (Radio-Electronics-Television Manufacturers Association) compatible mounting rails and accepts standard 19-in-wide rack-mounted subsystems. Within the cabinet, three spaces have been reserved for the user: a 3.5-in-high panel space above the status and control panel in the upper left front bay, a 7.0-in-high panel space above the blower unit in the lower right front bay, and a 8.75-in-high panel space at the bottom of the left rear bay. The 3.5-in space above the SCP will accept a unit not exceeding 12 in. in depth; the 7-in space above the blower unit will accept a unit not exceeding 8 in. in depth. These two spaces may be utilized for user equipment or panels; spare power outlets are provided supplying up to 360 W total. Equipment that dissipates appreciable power should contain integral ventilation blowers. The rear panel space is reserved for user I/O connectors, which provide a mating interface for the cabling connected to the user's target system or systems.

The XAIDS cardcage is a 21-slot (0.75-in spacing) IEEE-796 compatible unit having integral parallel priority resolution. Auxiliary (P2) connectors are not installed, and if possible, the user should avoid selecting boards that require them. Cardcage backplane power for +5, +12, and -12 V is provided, and the user is permitted to draw up to 16 A from the +5-V feed. Nine slots are reserved for the user board complement, six of which are wired for parallel bus priority resolution and may thus contain bus masters. All boards must decode 20 address bits, and memory-mapped domain bus requirements must not total more than 96 kbytes. The I/O-mapped domain access may be 8 or more address bits, and a minimum of 198 I/O addresses are available. Three backplane interrupts are reserved for the user,

one of which is currently configured to be generated by RTPRO, while the other two are sensed by RTPRO. Within the stated guidelines, the user may select or build whatever board complement is required to provide target system interfaces.

The user must provide cabling within the XAIDS cabinet to connect the user's I/O connector panel to rack-mounted equipment (if any) as well as to cardcage boards. While there does not need to be an interface of such cabling to the cabinet, there does exist a convenient interconnect point that the user may employ if desired. The cardcage interface connector panel is mounted inside the cabinet behind the cardcage and has 8 empty mounting holes for 25-pin connectors. This is a convenient spot to transition from ribbon cable (coming from the cardcage) to the pigtails going to the user I/O connector panel.

User-supplied software may fall into one of four categories: RMX86 utilities, I/O board programming, RTPRO resident extensions, and XAIDS executive extensions. The user has the option of creating utility programs, which are loaded and executed through the RMX86 human interface by simply entering the name of the file containing the load-time locatable code. Such utilities would necessarily be stand-alone RMX86 I/O jobs totally independent of the XAIDS executive (which in itself is a stand-alone I/O job). An example of such a utility would be a file processor that analyzes data previously written while running under the XAIDS executive. Creating such utilities requires knowledge of RMX86 system calls and file management techniques. The advantage of a stand-alone utility is that it may be quite large and has unrestricted access to system resources. An alternative option is to make the utility a routine that runs under XAIDS and is accessed with a menu command. This has the advantage of convenience by being accessible without exiting XAIDS.

With regard to user I/O board programs, the type of board selected in each case determines what programming options exist. If an I/O board does not have a large dual-port RAM, its program must be PROM resident and cannot be bootstrapped. If the board has a large dual-port RAM and employs an 8086 or 8088 central processing unit chip, the user can bootstrap its program using the XAIDS utility BOOT. If this option is selected, the necessary cooperative firmware module checks the byte flag at onboard address 4, which if set causes an interrupt 0 to occur. The BOOT utility first loads the program into the board's RAM, places the starting address in the interrupt 0 vector location (addresses 0 to 3), and sets the flag. A user I/O board that does not employ either the 8086 or the 8088 can still be bootstrapped if the user is willing to write a custom loader utility that transfers code from a non-RMX86 diskette to the I/O board. In this case, the load module would need to be on 8-in diskette and would necessarily be generated on a user-supplied development system. In general, the advantage of bootstrapping an I/O board is that its program may be changed more easily. The advantage of PROM-resident I/O programs is that the lengthy bootstrapping process at system power-up is eliminated.

All baseline software used in the XAIDS is created using Intel iAPX 86/88 Family Utilities. The user-supplied software that links to the RTPRO and XAIDS executive baseline software must be compatible. The XAIDS system has resident software development support for PL/M, FORTRAN, Pascal, and assembly language, thus giving the user a choice of source language. The compiler for the high-order language "C" is also available but is not currently installed. All baseline software is written in PLM86 and compiled using LARGE model. When a user elects to use one of the other languages, the compilation model must be compatible with PLM86 LARGE, and the source code must be rigidly disciplined in subroutine parameter passing. The use of PLM86

LARGE is encouraged since it guarantees problem-free integration with the baseline code.

After linking with the user's extensions, the RTPRO baseline software expects to find the following routines declared PUBLIC: USER\$INIT, USER\$TIMER\$0, and USER\$BACKGROUND. The first is called only once during the RTPRO initialization sequence, the second is called every 2 msec, and the third is called at a variable rate that depends on RTPRO loading. All three of these routines have access to the full set of RTPRO support routines shown in appendix D. Some of these are subroutines, and others are typed procedures (functions) that return a value. All are written in PLM86; non-PLM86 calls to these routines are permitted, provided that proper parameter passing is observed. The user has access to a large block of RAM for common data area and is expected to design protocol for handshaking with user CENPRO routines where required.

The USER\$INIT routine in RTPRO provides the user an opportunity to perform initialization steps related to load module identification, raw data type handlers, and channel handlers. The user must select a four-character ASCII identifier and write it into the PUBLIC variable RTPRO\$LOAD\$MODULE\$ID. This allows the user's CENPRO software to later verify that the proper RTPRO load module has been booted. For each raw data type that falls outside the baseline set, the user must supply a raw data handler and declare it from USER\$INIT. For each separate data input path (usually originating from an I/O board), the user must supply a channel handler, declare it, and decide what mode to employ in servicing it. The user has the option of declaring a channel from USER\$INIT or delaying until later and declaring it from USER\$BACKGROUND. Once declared, the servicing modes available are interrupt driven, timed polling, and background polling. If interrupt driven, the linkage must be set up and the interrupt level enabled.

The USER\$TIMER\$0 routine in RTPRO provides a means of performing timed polling of channel handlers or of performing other operations at user-selected intervals of 2-msec granularity. The USER\$TIMER\$0 routine is called with interrupts disabled from the timer 0 interrupt routine and is restricted to servicing that does not require the NDP. This routine should be as short as possible so as not to miss the next timer 0 interrupt and thus cause timing distortions.

The USER\$BACKGROUND routine in RTPRO is called from the looping main RTPRO program at intervals that vary widely with RTPRO loading. It provides a means for the user to service low-priority tasks that are triggered by handshaking flags from the user CENPRO software. This could even include the declaration of user channel handlers, the vectoring of interrupts, and the enabling or disabling of interrupts. It would likely control channel handler status and guarantee that proper synchronization with baseline channel handlers was maintained.

After linking with the user's extensions, the XAIDS executive baseline software expects to find the following declared PUBLIC: an ASCII string called USER\$NAME, two pointers called USER\$CMD\$LIST\$PTR and USER\$TEST\$LIST\$PTR, and five subroutines called USER\$INIT, USER\$CRT\$REQUEST\$ACTIVATE, USER\$CRT\$REQUEST\$RESET, USER\$DAC\$REQUEST\$ACTIVATE, and USER\$DAC\$REQUEST\$RESET. The USER\$NAME string must be 16 bytes long, the 16th byte must be null, and the remaining bytes should contain the identifying name that will be placed in the upper left corner of all displays. The pointers provide the user a means to specify the location of the two tables of

commands to be placed at the top of the main menu and the test menu, respectively. The USER\$INIT routine is called once when the XAIDS executive is initialized following load. The remaining four routines provide the user with the means to perform special processing if required at the beginning and end of display operation and at the latching and unlatching of recorder outputs. All user routines have access to the full set of CENPRO XAIDS operator interface support routines shown in appendix E. The names for these routines all begin with xq to distinguish them from RMX86 routines, which begin with rq.

The USER\$INIT routine in XAIDS allows the user to perform steps related to bootstrap loading of RTPRO and the I/O channel boards, performing RTPRO handshaking setup, declaring special display formats, initializing command handlers, and loading the pointers specifying the location of the two command tables. When USER\$INIT is called, it must first determine whether RTPRO is loaded with the proper load module. If not, the user purges the incorrect one (if required) and calls a bootstrap loader routine that is an embedded version of the utility BOOT. Like BOOT, OFFSET\$LOADER requires two arguments: a pointer to the filename for the RTPRO load module and the offset in 16-byte segments of the RTPRO RAM (which is 8000H). If any I/O boards need booting, OFFSET\$LOADER must be called for each. After successful I/O board boot, the RTPRO must be informed that the related channel handler or handlers may now be declared. If any special I/O board initialization following boot is required, that must be done here as well. If the user has any special display formats, they must be declared by calling a routine called DECLARE\$FORMAT\$TYPE with two arguments: the ASCII letter code and the address of the formatting routine associated with it. All user command handlers must be initialized, and their command declaration blocks in the appropriate table must be set up. The final step is to load the table pointers with the correct addresses.

### XAIDS CONFIGURATION FOR X-29A PROJECT SUPPORT

The X-29A forward-swept-wing aircraft employs a triplex digital flight control system using dual computers in each channel. At an early date, NASA stated a requirement for an XAIDS unit that would be used by X-29A project personnel both in the simulation laboratory and in the hangar. It was intended to support control system testing during software V/V, simulation exercises, systems integration, and pre- and postflight testing. The desired level of support required three different kinds of interfaces: monitoring three telemetry streams simultaneously, controlling two pieces of GSE, and providing I/O tie-in to the Ames-Dryden simulation laboratory. This section will deal with the configuration of the X-29A project's XAIDS to meet these requirements.

Figure 6 shows an overview of the XAIDS interfaces that had to be engineered for the X-29A project. Each channel of the aircraft's triplex flight control system consists of two processors called the control law processor (CLP) and the I/O processor (IOP). The three telemetry streams are Aeronautical Radio Incorporated (ARINC) 429B format running at 100 kbits/sec, with each IOP sending 64 32-bit "words" every 25 msec. The GSE are called system evaluation units (SEUs), with two being required, one to access the CLPs and the other to access the IOPs. The interface to the SEUs is through full duplex RS-232C serial trunks, which communicate with the resident firmware internal to each SEU. An SEU can perform various CLP-IOP

system interface bus operations, such as selectively halting or running a processor, reading or modifying RAM, reprogramming electrically erasable programmable read-only memory (EEPROM) chips, recomputing checksums, and examining registers. The simulation laboratory interface required both analogs and discretes to be bidirectionally transmitted through the RDAS for closed-loop simulated fault testing.

Table 17 shows the I/O board complement required to support these interfaces. Each I/O board handles one telemetry stream through a piggyback ARINC 429B transceiver module that is designed to mount on one of its so-called I/O expansion bus connectors. Two of the three boards also have a second piggyback module that provides one RS-232C interface to supplement the one on the main board. The RDAS interface through the LAN is part of the baseline XAIDS configuration and as such did not require any user-supplied components. Figure 7 shows the final configuration of the XAIDS cardcage with the I/O board complement installed.

The cabling for the ARINC busses and RS-232C ports uses flat ribbon cables from the I/O boards as far as the system interface panel behind the cardcage. Figure 8 shows the location of the X-29A connectors mounted in the right half of the system interface panel with the mated pigtails connecting to the X-29A aircraft interface panel at the rear of the console. Figure 9 shows the layout chosen for the aircraft interface panel; the three ARINC busses share a single connector at the bottom.

The PL/M program written for the I/O boards was designed to permit the boards to operate as slaves to RTPRO rather than as bus masters. Each board has 32 kbytes of dual-port RAM, all of which is mapped to the IEEE-796 bus memory domain creating three contiguous blocks. Each board has the same small startup routine in PROM, and the same program (IOP.X29A) is loaded by the bootstrap loader into the three RAMs. This program contains servicing routines that respond to local interrupts from the ARINC transceiver and RS-232C modules and handle the resulting data flow solely under the direction of the RTPRO. Each board signals status to RTPRO through a combination of semaphores and state variables, and thus no bus interrupts are required.

The RTPRO software extensions required for the X-29A system include six channel handlers, six raw data type handlers, and one rather large background task called X29A\$SIM, which locally computes anticipated control law gains. The status and control panel is not used, and no interrupts are serviced. The software was written using FORTRAN for the X29A\$SIM package and PL/M for everything else. A large block of RTPRO RAM is devoted to hard-mapping the FORTRAN COMMON blocks for X29A\$SIM so that CENPRO can display the common variables. The USER\$INIT routine declares three channels (H1, H2, and H3), declares six raw data types (HSP, HDP, HFLT, HHEX, HINT, and HBOO), and loads the identifier X29A into RTPRO\$LOAD\$MODULE\$NAME. The three channels access buffers within RTPRO RAM that contain control system data fetched through the SEUs. The six raw data type handlers provide conversion of the processor data types, single precision, double precision, floating point, hexadecimal, integer, and boolean, to NDP-compatible types. The algorithms employed in these data handlers are summarized in appendix C. The USER\$BACKGROUND routine checks on I/O board status and waits until bootstrap load is complete before declaring the corresponding ARINC channel handler (A1, A2, or A3). It also invokes the execution of X29A\$SIM when so directed by CENPRO and manages the status keeping for any ARINC channels that happen to be idle. The USER\$TIMER\$0 routine polls the three I/O boards (every 2 msec) to see if a fresh ARINC data buffer load is ready. As the active channels show ready, an elapsed timer is checked so that only data frames

coincident within an 8-msec window are accepted. If proper synchronization is sensed, it calls the routine named SYNCH, which in turn triggers the copying of whatever data are required from the I/O board buffers to the data acquisition control structures.

The CENPRO software extensions required for the X-29A application include the USER\$INIT routine, seven main menu command handlers, two test menu command handlers, and a USER\$CRT\$REQUEST\$ACTIVATE routine. No custom data display formats are declared. The USER\$INIT routine loads the I/O boards with the file IOP.X29A, sets the default baud rate (2400) on the four SEU trunks, and loads the RTPRO with the file RTPRO.X29A. It then initializes the nine command handlers and sets up the command list pointers. The seven main menu commands are QT, RU, SEU1, SEU2, PTCH, PMSW, and GAIN. The two test menu commands are ARNC and BAUD.

# OPERATION OF THE X-29A XAIDS

The XAIDS unit constructed for the X-29A project went into service in January 1984 and by October 1986 had accumulated over 3600 hr of operation in the Ames-Dryden real-time simulation laboratory. During this period the unit was used for diverse support including software V/V, closed-loop simulation testing, and pilot training. This section gives an overview of XAIDS operator procedures and presents sample printer hard copies of displays made during actual operations.

The XAIDS firmware and software load modules were configured to totally eliminate any need for operator interaction during bootstrap and initialization following power-up. The operator need only turn on the RDAS power switch, then turn on the XAIDS power switch, and wait approximately 1 min until the XAIDS main menu appears on the CRT screen. During this waiting period, several messages appear on the screen that give the operator the status of the ongoing bootstrap and initialization stages. The first message to appear is the RESET mode sign-on generated by PERPRO to signal its readiness to accept communications from CENPRO. Meanwhile the RMX86 operating system is being loaded, and approximately 30 sec later the RMX86 basic I/O system (BIOS) switches PERPRO to RMX86 mode, thus telling the operator that the operating system is running. Following this, the operating system submits the logon file for execution. The next message to appear is generated by the utility RBOOT as it performs the RDAS bootstrap; if RDAS is not connected or not powered up, RBOOT aborts with an appropriate message. The final stage of the initialization process is when the logon file invokes the command XAIDS, which begins the loading of the XAIDS executive.

The XAIDS executive loaded into CENPRO by the human interface is classified as an RMX86 "I/O job" and consists of the executive baseline linked to the X-29A extensions. When the load cycle is complete, the executive takes control of the system, switches PERPRO to XAIDS mode, and activates the operator's keyboard. From this point on the operator has the option of aborting the XAIDS executive initialization and returning to RMX86 mode by pressing the <esc> key. The executive next calls the X-29A USER\$INIT routine, which controls the boot of the I/O boards and RTPRO. The following messages appear on the screen (in bottom to top scroll fashion) during the execution of USER\$INIT:

SLAVE PROCESSOR LOADER ROUTINE PATHNAME : :sd:user/1/1op.x29a

SEGMENT = C800

LHEADER : X29A\_IOP\_MAIN\_P86

MODEND TYPE 3 T MAIN MODULE WITH START ADDRESS = 0040 : 0006

TOTALS: IGNORED = 108 PEDATA = 82 PIDATA = 0

SETTING UP DEFAULT SEU #1 BAUD RATES

TERMINAL BAUD RATE = 2400 MODEM BAUD RATE = 2400

SLAVE PROCESSOR LOADER ROUTINE PATHNAME : :sd:user/1/1op.x29a

SEGMENT = DOOO

LHEADER : X29A IOP MAIN P86

MODEND TYPE 3 : MAIN MODULE WITH START ADDRESS = 0040 : 0006

TOTALS: IGNORED = 108 PEDATA = 82 PIDATA = 0

SETTING UP DEFAULT SEU #2 BAUD RATES

TERMINAL BAUD RATE = 2400 MODEM BAUD RATE = 2400

SLAVE PROCESSOR LOADER ROUTINE PATHNAME : :sd:user/1/iop.x29a

SEGMENT = D800

LHEADER: X29A IOP MAIN P86

MODEND TYPE 3 : MAIN MODULE WITH START ADDRESS = 0040 : 0006

TOTALS : IGNORED = 108 PEDATA = 82 PIDATA = 0

SLAVE PROCESSOR LOADER ROUTINE PATHNAME : :sd:user/1/rtpro.x29a

SEGMENT = 8000

LHEADER : RTPRO MAIN P86

MODEND TYPE 3 : MAIN MODULE WITH START ADDRESS = 0040 : 0006 TOTALS : IGNORED = 155 PEDATA = 494 PIDATA = 1098

This sequence loads and initializes the four slave processors in the following order: IOP A, IOP B, IOP C, and finally RTPRO. The executive then loads the symbol table from the scratch diskette in drive :F3: and finally enters the command interpreter.

Beginning at the time the XAIDS executive first enters the command interpreter, the operator may at any time request PERPRO to perform a snapshot of the screen display and provide a hard copy on the line printer. These hard copies are true single-frame snapshots and are requested using the keyboard entry <cntl P>. Another keyboard command recognized by PERPRO is <cntl U>, which signals a request to change the screen refresh update period (initially defaulted to 0.5 sec). The next keystroke is then interpreted as the desired period in deciseconds and must be one of the set 1,2,3,4,5,6,7,8,9,A,B,C,D,E,F covering the range from 0.1 to 1.5 sec. These commands are recognized by PERPRO only while in XAIDS mode; in RMX86 mode all keystrokes are passed to the RMX86 BIOS without prior PERPRO interpretation.

The command interpreter main menu display shown in display 1 (screen displays follow the figures at the end of this report) is the first formatted page display presented by the executive and is the last one seen when returning to RMX86 using the command EXIT. If the command TEST is entered, the subsidiary menu shown in display 2 is displayed. On the main menu, the first seven commands are X-29A extensions; on the test menu, the first two commands are X-29A extensions. These two command menus provide first-level access to the complete spectrum of XAIDS executive functions.

The first step normally required of the operator is to command the three control system computers to RUN state using command RU. Display 3 shows the display generated by this package as it verifies the links to the SEUs, selects all three channels, displays the checksums, and finally sends the SEU command RU to place the three channels in RUN mode. The sequence is performed twice since separate SEUs control the CLPs and IOPs, and both sets must be placed in RUN mode. A companion XAIDS command is QT, which performs the shutdown sequence shown in display 4. Notice the difference in the order of the operations performed since the computers must first be halted using the SEU command QT before the checksums can be fetched. If either package cannot communicate with either SEU, the software hangs while waiting for SEU response, and the operator must enter <esc> to terminate. The <esc> key is universally recognized by all XAIDS command handlers as an abort request; pressing the <esc> key enough times will return the operator from even the deepest level of a command handler to the main menu display.

The main menu commands SEU1 and SEU2 invoke handlers that allow the operator access to the respective SEU using the XAIDS terminal in emulator mode. In this mode, keystrokes are echoed to the CRT and sent to the SEU one at a time, and the response character stream received back from the SEU is written to the CRT. XAIDS responds to <esc> by terminating the emulation and returning to the main menu. While an SEU terminal emulator is being used, the <cntl P> command is functional, and hard copies may be made at any time.