Innovation for Our Energy Future

# GalnAs 4th Junction for Next-Generation Lattice-Mismatched Multijunction Solar Cells

D.J. Friedman, J.F. Geisz, A.G. Norman, M. Wanlass, and S.R. Kurtz

National Renewable Energy Laboratory

NREL/PR-520-39909

Presented at the 2006 IEEE 4th World Conference on Photovoltaic Energy Conversion (WCPEC-4) held May 7-12, 2006 in Waikoloa, Hawaii.

#### The Fine Print

#### **Disclaimer and Government License**

This work has been authored by Midwest Research Institute (MRI) under Contract No. DE-AC36-99GO10337 with the U.S. Department of Energy (the "DOE"). The United States Government (the "Government") retains and the publisher, by accepting the work for publication, acknowledges that the Government retains a non-exclusive, paid-up, irrevocable, worldwide license to publish or reproduce the published form of this work, or allow others to do so, for Government purposes.

Neither MRI, the DOE, the Government, nor any other agency thereof, nor any of their employees, makes any warranty, express or implied, or assumes any liability or responsibility for the accuracy, completeness, or usefulness of any information, apparatus, product, or process disclosed, or represents that its use would not infringe any privately owned rights. Reference herein to any specific commercial product, process, or service by trade name, trademark, manufacturer, or otherwise does not constitute or imply its endorsement, recommendation, or favoring by the Government or any agency thereof. The views and opinions of the authors and/or presenters expressed herein do not necessarily state or reflect those of MRI, the DOE, the Government, or any agency thereof.

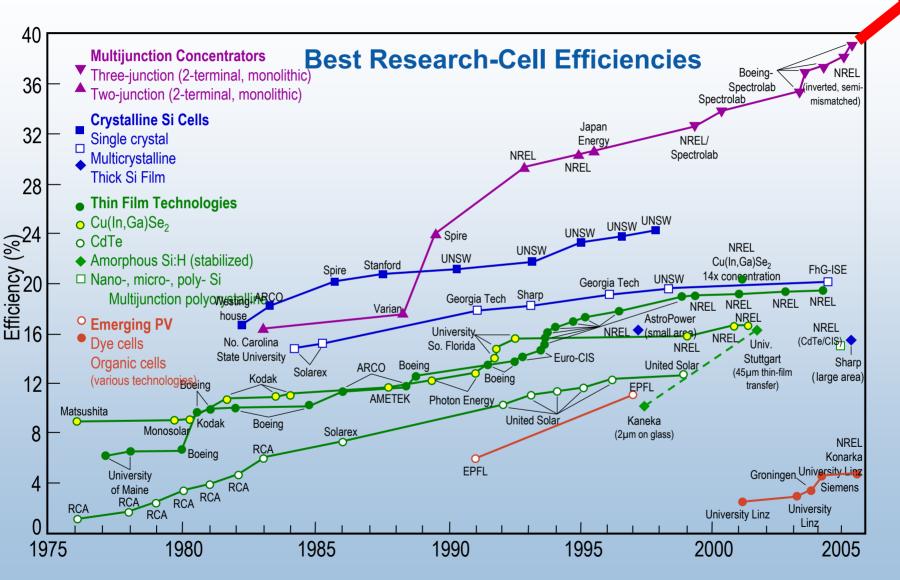

# **Evolution of Multijunction Devices**

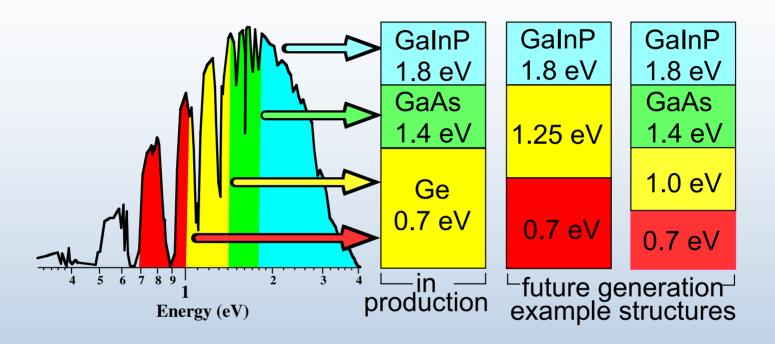

- Need to make better use of spectrum, esp. in 0.7–1.4 eV range

- How to do this...?

#### **Outline**

- Approaches to next-generation high efficiencies: survey of the field

- The inverted mismatched 3-junction cell

- Adding a 4th junction

- Fabrication and testing of 4th junction

- How low a bandgap do we really need?

- Outlook

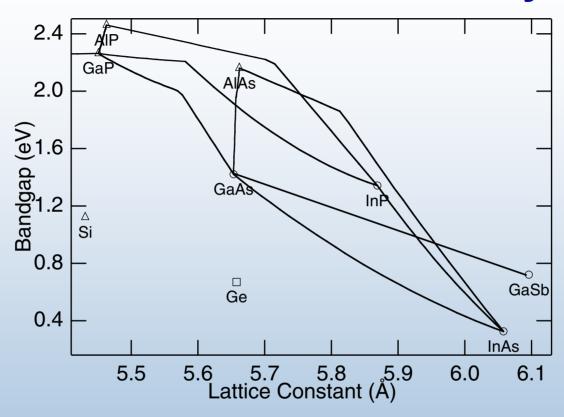

# **Our Palette: the III-V Alloys**

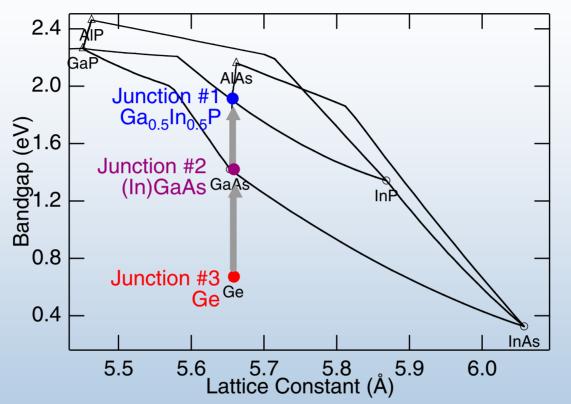

# Lattice-Matched to Ge (and GaAs)

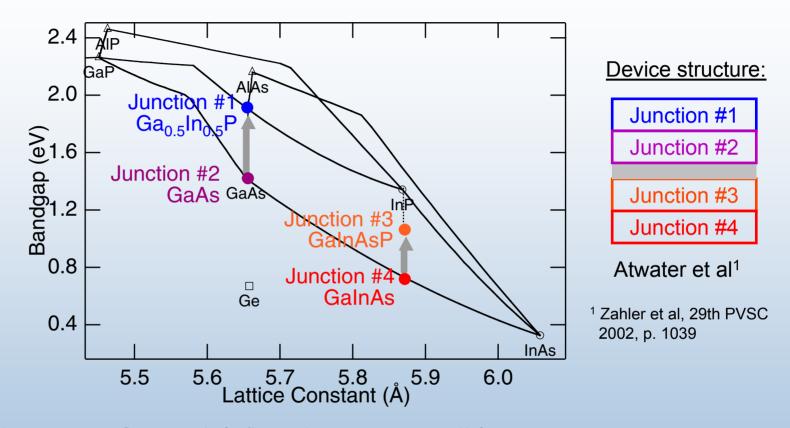

#### Device structure:

Junction #1

Junction #2

Junction #3

39%@236x by Spectrolab<sup>1</sup>

<sup>1</sup> King et al, 20th Eur.Solar Energy Conf. 2005 p.118

- The "standard" 3-junction device structure

- Lattice-matched: easy to grow good material... but

- Restricts available bandgap range

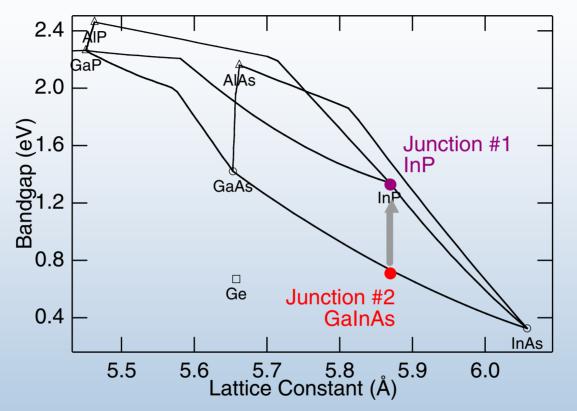

#### Lattice-Matched to InP

#### Device structure:

Junction #1

Junction #2

31.8% @ 50x (three-terminal) by NREL<sup>1</sup>

<sup>1</sup> Wanlass et al, 21st PVSC, 1990, p.38

Another example - lattice matching to InP

# Expanding our Range of Bandgap Options

- New materials lattice-matched to GaAs: e.g. GaInNAs

- Need good PV materials

- Junctions grown separately, then stacked

- Mechanical stacking

- Wafer bonding

- Lattice-mismatched epitaxy

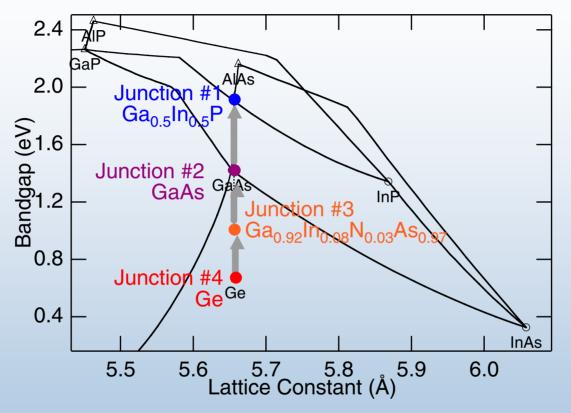

#### **New Semiconductor: GalnNAs**

#### Device structure:

Junction #1

Junction #2

Junction #3

Junction #4

- <sup>1</sup> Ptak et al, 31st PVSC 2005, p. 603

- <sup>2</sup> Jackrel et al, this meeting

- <sup>3</sup> Meusel et al, 19th Eur.PVSEC 2004 p.3587

- <sup>4</sup> King et al, 19th Eur.PVSEC 2004 p.3581

- GaInNAs: lattice-matched, desired bandgap...

- But: short diffusion lengths >> poor device performance

- MBE may help growth<sup>1,2</sup>

- 5- or 6-junction structures may work around problems<sup>3,4</sup>

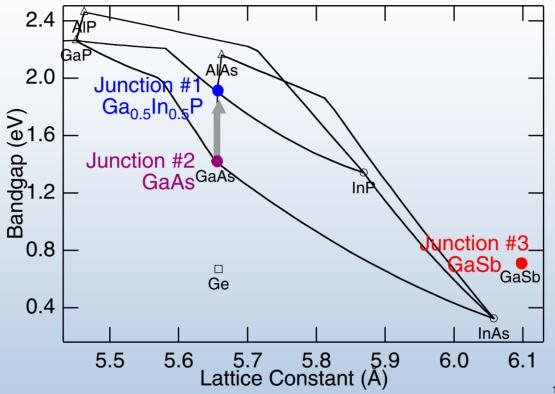

# **Mechanically Stacked Junctions**

#### Device structure:

Fraas,<sup>1,2</sup> Fraunhofer ISE (33.5%@308x)<sup>3</sup>

- Extremely wide range of materials/bandgaps accessible:

high efficiencies; e.g. 32.6% for GaAs/GaSb back in 1990¹

- Not a single chip; multiple growths required

<sup>&</sup>lt;sup>1</sup> Fraas et al, 21st PVSC 1990, p. 190

<sup>&</sup>lt;sup>2</sup> Fraas et al, 31st PVSC 2005, p. 751

<sup>&</sup>lt;sup>3</sup> Bett et al, 17th Eur.Solar Energy Conf. 2001 p.84

#### **Wafer-bonded Stacked Junctions**

- Wide range of materials/bandgaps accessible

- single chip / III-V integration with Si

- Multiple growths required; requires transparent conductive bond

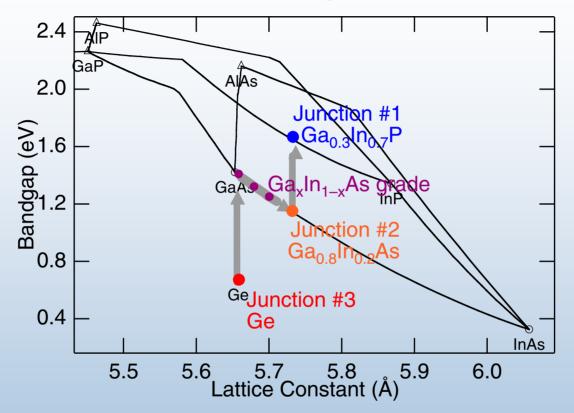

# Lattice-mismatched ("metamorphic") 3J

#### Device structure:

Junction #1

Junction #2

grade

Junction #3

Spectrolab<sup>1</sup>, Fraunhofer ISE<sup>2</sup> EMCore<sup>3</sup>

- <sup>1</sup> Law et al, 31st PVSC, 2005, p.575

- <sup>2</sup> Dimroth et al, Prog. Photovolt. **9**, 2005, p.165

- <sup>3</sup> Stan et al, 31st PVSC, 2005, p. 770

- Promising approach, competitive with lattice-matched

- Challenge is to maintain materials quality of junctions grown after grade

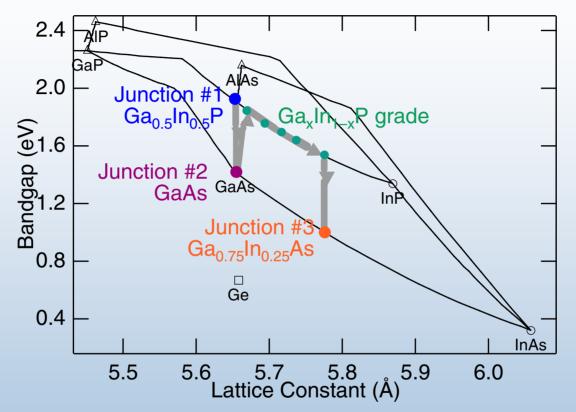

### **Inverted Lattice-Mismatched Structure**

#### Device structure:

Junction #1

Junction #2

grade

Junction #3

Wanlass et al<sup>1,2</sup>

- Wanlass et al, 31st PVSC 2005, p. 530

- <sup>2</sup> Wanlass et al,this meeting

- <sup>3</sup> Schultz et al, 21st PVSC 1990, p. 148

- Only the bottom junction is grown mismatched

- Similar philosophy to Varian GalnP/GaAs/substrate/GalnAs design<sup>3</sup>

- Potential for very high efficiencies (38% achieved w.o. optimization)

- Some complexities but also opportunities in the processing...

### **Processing of Inverted Structure**

1: Growth 2: Bonding 3: Substrate Removal foreign substrate foreign substrate epi growth lattice-mismatched lattice-mismatched lattice-mismatched low-Eg junction(s) low-Eg junction(s) low-Eg junction(s) lattice-matched lattice-matched lattice-matched high-Eg junctions high-Eg junctions high-Eg junctions Substrate Substrate (GaAs or Ge) (GaAs or Ge) illumination FINISHED DEVICE lattice-matched layers grown first lots of freedom in choice of foreign substrate: lightweight, flexible, etc.

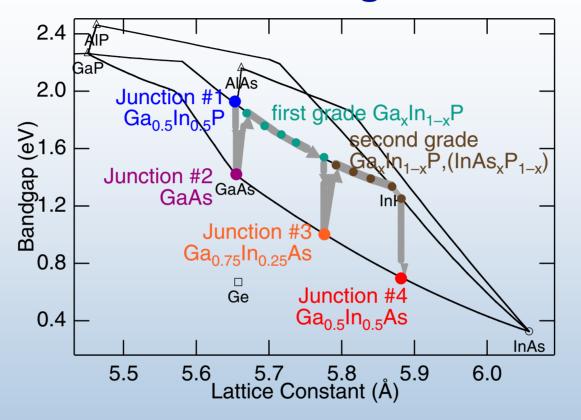

### **Inverted LMM: Adding a 4th Junction**

#### Device structure:

Junction #1

Junction #2

first grade

Junction #3

second grade

Junction #4

- Extend advantages of inverted 3-junction structure to higher efficiencies

- But: how far can we grade? How far do we need to grade?

#### 4th Junction: Test Structure

Inverted 4 Junction Design:

GalnAs Junction (0.7 eV)

GalnP Grade

GalnAs Junction (1 eV)

GaInP Grade

GaAs Junction (1.4 eV)

GaInP Junction (1.8 eV)

GaAs or Ge Substrate (removed after growth)

4th Junction Test Structure:

not to scale GalnAs Junction

(0.74-0.88 eV)

GalnP Grade

GalnAs Isotype Layer

Simulated Junction (1 eV)

GalnP Grade

**GaAs Substrate**

- Accounts for effect of latticemismatched growth

- Bypasses complexities of growth and especially of measurement of the other three junctions

- Tried bandgaps from 0.88–0.74 eV

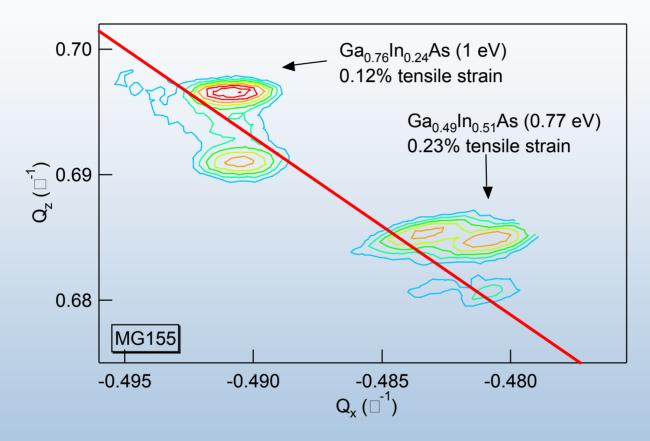

# X-ray Characterization of Strained Layers

XRD analysis critical to getting the compositions correct

#### **TEM Characterization: 4th Junction**

0.77 eV 4th junction -220DF  $Ga_xIn_{1-x}As$  (0.77 eV) InP Ga<sub>x</sub>In<sub>1-x</sub>P grade 2 µm MG298

4th Junction Test Structure:

GalnAs Junction (0.74-0.88 eV)

GaInP Grade (including InP buffer)

GalnAs Isotype Layer Simulated Junction (1 eV)

GaInP Grade

GaAs Substrate

not to scale

Dislocations largely confined to grade

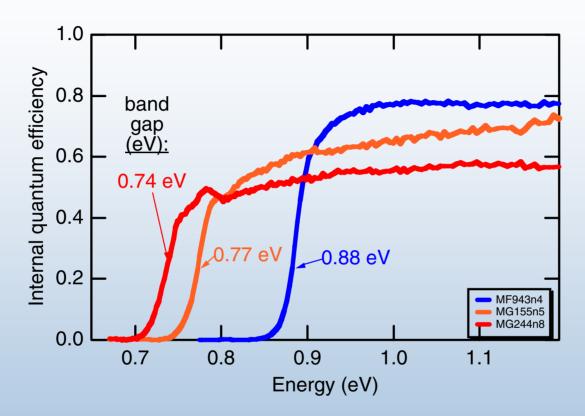

### **Quantum Efficiency**

- QE degrades with increasing mismatch (decreasing Eg) (note -- still room for improvement in these devices)

- QE of 0.88 eV device approaches performance required (note -- QE achieved without significant depletion region)

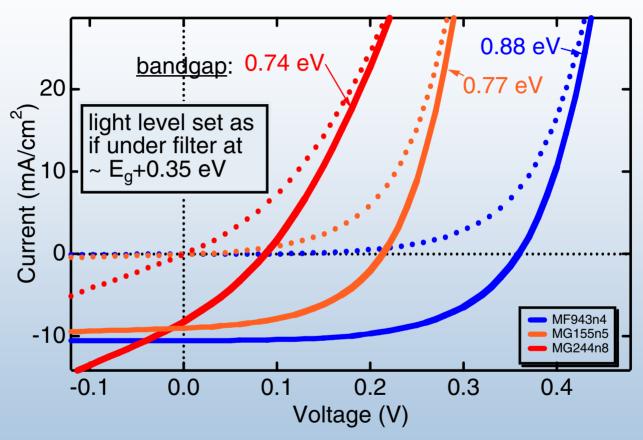

### **Current-Voltage Characteristics**

Eg=0.74eV junction leaky, others good

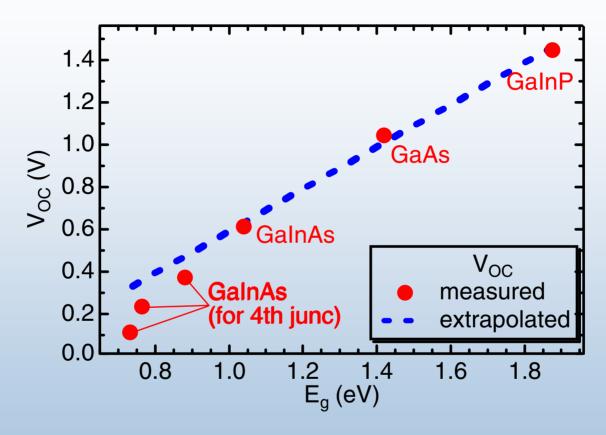

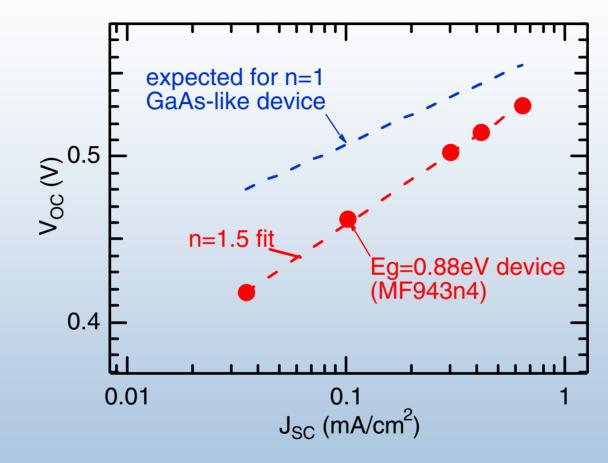

# Dependence of V<sub>oc</sub> on Band Gap

- Lowest-Eg junction degraded

- Higher-Eg junctions better (and should get closer to GaAs-like with concentration)

### Improvement of Voc with Concentration

Voc does get closer to GaAs-like with concentration, as expected

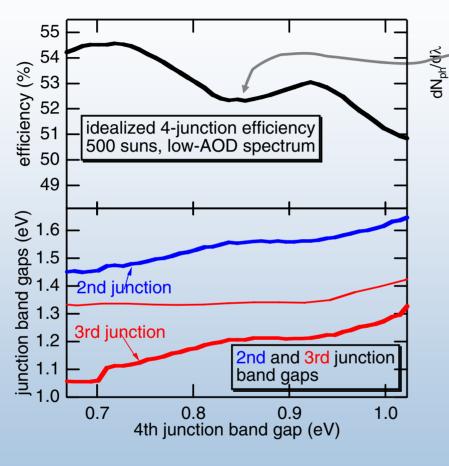

# 4th-Junction Eg - is 0.7 eV Necessary?

Good devices increasingly challenging as band gap decreases (i.e.mismatch increases)

Can we get away with a higher 4th junction band gap?

### **Allowing Band Gap to Vary**

- Can raise 4th junction Eg from 0.7 to 0.9 eV and only lose 1.6% eff.

- Still 4% above GaInP/GaAs/1-eV 3j

- Real-world efficiency for the 0.9-eV option likely to be ~45%

# Device with 4th Junction Eg=0.9 eV

#### Why consider this over the 0.7-eV option:

- High-quality 0.9-eV junction easier to make

- Efficiencies:

- Only lose 1.6% efficiency compared to 0.7-eV option

- Still 4% above the 1.85/1.41/1.0eV 3-junction efficiency

- Grade layers can be thinner:

- Less time to grow

- Less source material used

- Less strain/wafer bowing

#### Concerns:

- 1.6 eV junction needed: can it be as good as GaAs?

- Tunnel junctions need to be demonstrated

#### **Outlook**

- A cornucopia of promising approaches to next-generation high efficiencies

- may be places for more than one, in different cost-performance niches

- Inverted multijunction approach

- Extending to 4 junctions likely to boost efficiencies by several %, to ~45%

- 4-junction structure likely to use an 0.9-eV bottom junction

# A Golden Age for Multijunctions!