| An Alternative Methodology: Valuing Quality Change for Microprocessors in the PPI                             |

|---------------------------------------------------------------------------------------------------------------|

|                                                                                                               |

| Mike Holdway Bureau of Labor Statistics                                                                       |

| Division of Industrial Prices and Price Indexes Revised 1-01                                                  |

|                                                                                                               |

|                                                                                                               |

|                                                                                                               |

|                                                                                                               |

|                                                                                                               |

|                                                                                                               |

|                                                                                                               |

|                                                                                                               |

|                                                                                                               |

|                                                                                                               |

|                                                                                                               |

|                                                                                                               |

| The proposed quality adjustment methodology for microprocessors is currently under internal review. The views |

| expressed represent those of the author and not those of BLS or any of its staff.                             |

|                                                                                                               |

|                                                                                                               |

# An Alternative Methodology: Valuing Quality Change for Microprocessors in the PPI

Mike Holdway

## **Identifying the Target**

Identifying and valuing quality change for the rapidly evolving microprocessor (mpu) requires several preparatory steps. Obviously we must obtain an understanding of the basic functional features that mpus are designed to provide and the manufacturing processes used. But we must first insure that our net is cast over the entire mpu market which is more broadly inclusive than the casual observer might suspect.

If you ask most people to define or describe a mpu they are likely to employ restrictive computer centric terms such as CPU, computer chip or even computer "brain". Many computer manufacturers imply an even more restrictive definition when they use the phrase "Intel Inside" as an integrated and highly visible part of their marketing strategies. The popular association of mpus and Intel Corporation is not surprising because Intel enjoys a dominant position as a producer. Various trade publications, such as *Microprocessor Report* and *Electronic News*, estimate Intel's 1999 share of the computer mpu (cmpu) market at around 80 percent in terms of units shipped and 90 percent in terms of revenue. Visibility and marketing aside, cmpus are only a subset of the total mpu market.

Another type of mpu designed for non-computer applications is called the embedded<sup>2</sup> processor (empu). Empus are found in cellular and digital phones, motor vehicles, air transportation, communication networks, electronic organizers, pagers, printers, game consoles (i.e. Sega and Nintendo) and thousands of other consumer and industrial products. Empus account for approximately 98 percent of worldwide processor shipments<sup>3</sup>, but less than 20 percent of revenue because of much lower average selling prices relative to cmpus. Perhaps because of their lack of identification with a highly visible company, empus not only have little recognition in the general public but have been ignored by much of the economic literature that has attempted to provide quantitative or technical insight to the general mpu market. In terms of economic measures such as price indexes, GDP and productivity, it is important that neither mpu subset is used as a proxy for the overall market due to significant differences in technology and price trend. Because embedded designs are often application or customer specific, they tend to have longer life cycles relative to cmpus which reduce product substitutions and the corresponding need to value quality change. In contrast, cmpus have exceptionally short life cycles which require the PPI to make almost

<sup>&</sup>lt;sup>1</sup> Intel Corporation subsidizes the cost of computer (PC) manufacturers advertisements if they include this slogan and Intel's logo in their marketing materials. Intel has final approval of proposed OEM advertising for which they fund several hundred million dollars annually (approximately 3% of revenues). The subsidies began in 1991 and by 1994 "almost the entire PC industry had joined in". See *Intel Inside*, Jackson, T, Penguin Putnam, 1997, pg. 315.

<sup>&</sup>lt;sup>2</sup> Trade journals such as *Electronic Buyers News* (www.ebn.com) often describe empus as any non-computer processor. This description is essentially correct though there are a few mpus that are sold into both embedded and computer markets.

<sup>&</sup>lt;sup>3</sup> Approximately 140 million cmpus shipped last year vs almost 5 billion empus. "Guest Viewpoint: Embedded Systems and the Microprocessor", Microprocessor Report, 4-24-2000, http://www.mdronline.com/mpr/h/2000/0424/141702.html

continual estimations of quality change. Thus, the description of a targeted quality adjustment and product substitution strategy will be limited to cmpus.

## A Brief Retrospect of PPI CMPU Coverage

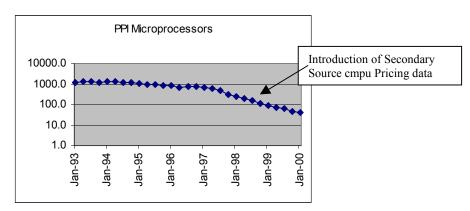

Prior to 1997 the PPI's Microprocessor index (code 36741A201) was moved primarily by empus and small niche players in the cmpu market. The disparity between the PPI sample and mpu universe was due in part to significant non-response from a major segment of the cmpu market. As previously mentioned, the technology and price trends of empus and cmpus are dissimilar. To the extent that the PPI sample was not representative of the market, significant bias may have been introduced. The bias became evident over time as the PPI's Microprocessor index was correctly (in hind-sight) criticized by the Bureau of Economic Analysis<sup>4</sup> (BEA), the Federal Reserve, and economic consultants from the private sector. After careful review the PPI introduced secondary source<sup>5</sup> pricing data for cmpus on January 1997. The introduction of secondary source prices can be viewed as a limited supplemental sample designed to represent 85 percent of the cmpu market that was not available for direct repricing in the PPI. Chart 1 shows, in log form, the change in PPI's Microprocessor index starting from the last sample (1993) through January 2000 in order to present a kind of before and after.

#### Chart 1.

The significance of augmenting the PPI with secondary data to enhance its coverage of cmpu pricing trends is apparent.

As mentioned in the opening section, the first step in our inquiry was to identify the target. This step is largely complete, but at this point we are no closer to a technical definition of cmpus than when we started. A basic understanding of cmpu architecture is required if the PPI is to effectively address the issue of calculating

<sup>&</sup>lt;sup>4</sup> Bruce Grimm, a research economist with the BEA, sent a paper to the PPI for comment in 1996 titled "Quality Adjusted Price Indexes for Metal Oxide Semiconductor Microprocessor Integrated Circuits". He uses secondary source data to construct a summary chained Fisher index for cmpus from 1985 to 1994. The Fisher cmpu index had an AGR of -35.3 percent for the 84-96 time frame (95-96 were extrapolated). The AGR for the PPI Microprocessor index in the same period was -2.9 percent. The difference in index formula (Fisher vs Laspeyres) can not explain the significant difference in AGRs. Ignoring index formulas and the empu segment (omitted from the BEA index), the most obvious difference is that BEA was able to purchase cmpu pricing data that was missing in the PPI.

<sup>&</sup>lt;sup>5</sup> Pricing data for the major X86 cmpus are obtained from *Microprocessor Report* and *Electronic News* in 1,000 lot order sizes. Both publications are used as a cross-check for accuracy.

valuations for rapid technological change. For now, we can think of cmpus as semiconductor devices that are designed to process or execute instructions. They require power, memory and communication channels (inputoutput) to operate.

#### Then and Now

Intel invented the first mpu, the 4004, in 1971 which they initially marketed as a microprogrammable computer on a chip to computer hobbyists for around \$200. Within two years, competitive pressure and faster processors forced the price of the 4004 below \$100. Compared to modern cmpus, the 4004 was a crude device with 4 bit internal data paths, 2,300 transistors and an operating speed of 108Khz<sup>6</sup>. Intel introduced its latest generation cmpu, the Pentium III, in 1999. This mainstream device includes 64 bit internal data paths, 28 million transistors, and a current maximum speed of 1,000Mhz. The Pentium III has additional architectural features that are far beyond the capabilities of 1971 technology. These features include but are not limited to L1/L2 caches, register renaming, out of order execution, multiple instruction units, pipelining, and single instruction-multiple execution.

The massive technological and performance differences between current generation cmpus and Intel's original device occurred as a progression of advances over time. Our initial view of this progression is best served with a simplified approach that limits technological comparisons to changes in the number of cmpu transistors used to manipulate data.

The internal structure of the cmpu is composed of multiple functional units that are made up of logic gates (if 1 do this; if 0 do that) which are in turn built with transistors. Transistors function as electronic switches in the sense they either allow the passage of electrons through a circuit, thereby signaling an ON condition, or block the flow of electrons signaling an OFF condition. This switching capability is key to a cmpu's ability to function because it is a binary device that can only accumulate and string together a series of 1s and 0s to represent words and numbers which in turn can be used as data or instructions. The ability of a cmpu to perform useful work by executing instructions efficiently has a great deal to do with the design and layout, also referred to as the architecture of the device. In other words, if both manufacturer A and B produce competing cmpu products with a similar transistor count<sup>7</sup>, manufacturer A's device may outperform manufacturer B's due to a more efficient architecture. For this reason, and others, transistor counts should not be viewed as an absolute technology metric, but are useful as a general indicator of relative improvements in design as well as production processes. Table 1 shows the amazing increase (+12,172%) in the number of transistors that Intel has been able to design into their major cmpu products since 1971.

<sup>&</sup>lt;sup>6</sup> Microprocessor Timeline 1971-1976; http://www.islandnet.com/~kpolsson/comphist/comp1971.htm

<sup>&</sup>lt;sup>7</sup> And also use similar production technologies that yield comparable feature size.

Table 1\*

|                   | Year of      |                  |          |

|-------------------|--------------|------------------|----------|

| MPU Product       | Introduction | # of Transistors | % Change |

| Intel 4004        | 1971         | 2,300            |          |

| Intel 8008        | 1972         | 3,500            | 52%      |

| Intel 8080        | 1974         | 4,000            | 13%      |

| Intel 8086        | 1978         | 29,000           | 625%     |

| Intel 80286       | 1982         | 134,000          | 362%     |

| Intel 80386       | 1985         | 275,000          | 105%     |

| Intel 80486       | 1989         | 1,200,000        | 336%     |

| Intel Pentium     | 1993         | 3,100,000        | 158%     |

| Intel Pentium Pro | 1995         | 5,500,000        | 77%      |

| Intel Pentium II  | 1997         | 7,500,000        | 36%      |

| Intel Pentium III | 1999         | 28,000,000       | 273%     |

<sup>\*</sup>From www.intel.com/intel/museum/25anniv/hof/tpecs.html.

The rapid growth in transistors that are packed within a tiny slice of silicon is one of many possible measures of technological advances that have occurred over time. It is the magnitude of technical change that is of interest because if unaccounted for in a price index, the index becomes unavoidably biased.

The PPI did not publish a Microprocessor index in 1971, but we can hypothesize an extreme example and ask how the PPI would go about constructing a index (T=2000; T-1=1971) while adjusting price change for the massive technological differences between the 4004 and a current generation cmpu. The Pentium III has a transistor count more than 12,000 times that of the 4004 and a Mhz rating that is more than 10,000 times faster. In terms of transistor density, the 4004 had 2,300 transistor in a 12mm<sup>2</sup> chip or 191 transistors per mm<sup>2</sup> of silicon. The Pentium III packs 28 million transistors into a 106mm<sup>2</sup> chip which is equivalent to 264,151 transistors per mm<sup>2</sup> of silicon. These are a few of the characteristics (out of hundreds) that partially define cmpu technical advances. Conventional PPI quality valuation methodology would use a comparison of production cost differences between the 4004 and Pentium III. This procedure (if relevant data could be obtained from manufacturers) implicitly assumes that a significant quality increase is accompanied by higher resource/input cost. To correctly apply changes in resource cost to value changes in cmpu quality requires that the PPI answer the question; What is the input cost difference between a obsolete cmpu and its replacement using the production function of the obsolete (Laspeyres) product? The relevant production function is reversed in a Paasche. However, one of the consequences of Moore's Law<sup>8</sup>, is that cmpus not only get faster and better over time, but also cheaper. This is a powerful insight that is made possible by improvements in chip fabrication technologies that allow more transistors to be packed on smaller less costly chips. It is this latter point, lower unit cost that is related to technological improvements, that make a direct comparison of resource costs problematic. New input technologies that

<sup>&</sup>lt;sup>8</sup> Gordon Moore, cofounder of Intel Corp., postulated in 1965 that that the logic density of silicon transistors doubled every year; he later changed this to 18 months, and the figure still applies today. Moore's Law can be graphed as an exponential curve; although it starts slowly, the pace of growth accelerates as time passes. Advances in cmpu input technologies have enabled producers to transform roomfuls of vacuum tubes into chips the size of a fingernail.

significantly change cmpu input requirements reflect a shift in the production function, not a movement along the function available in the reference period. Despite the difficult measurement problem caused by non-comparable production functions, it is important to keep the resource cost issue in perspective. Rapid technological change that simultaneously reduce unit input cost while substantially increasing output quality does NOT invalidate the resource cost approach in a output price index. While the PPI continues to emphasize the resource cost criteria for valuing quality change, cmpus and other high-tech products often require information that is not available in a real-time environment.

Triplett (1983) presents a more lucid description of the resource cost measurement problem using the example of rapid advances in computers that also involve a shift in the production function. He supports the correctness of the resource cost approach, but states that the *requirements function* is unknown. *That is, there may be data on the cost of the old machine under the old technology and the cost of the new machine under the new technology, but no data at all on the cost of both under comparable technologies.* In fact, the PPI usually has no timely information on cmpu input costs for either the old or new technology. Triplett proposes taking the analysis of quality change into characteristics space (hedonics) as one way of addressing the practical limitations of the resource cost criteria. However, the PPI's experience with hedonics<sup>9</sup> has shown that this approach may not provide a viable alternative for some high tech goods. Hedonics, as applied to cmpus, will be discussed in a later section of this paper.

## **CMPU Quality Improvement and Reduced Unit Input Cost**

A quick review of fundamental cmpu production processes will help explain how cmpu unit production cost can fall as technical features improve. The following description is oversimplified, so I highly recommend the book "Microchip Fabrication", 3<sup>rd</sup> Edition, by Peter Van Zant for a more complete description.

The production process begins with the basic material, refined silicon, which is implanted with precise amounts of impurities<sup>10</sup>. The introduction of impurities, also called doping, give the silicon desirable properties such an excess or deficiency of electrons. It is the flow of electrons that are controlled by transistors that enable the ON/OFF states recognized and manipulated by the cmpu. Silicon wafers enter a complex production process enabled by some of the most advanced equipment in the world, such as ion implanters and photolithography projectors that are so precise that the wavelength of ordinary light is relatively crude. Photolithography equipment uses an intense light source to project multiple images of integrated circuits onto the silicon wafer. The image patterns are captured by a special film called a resist that has been applied to the wafer. The pattern is transferred from the resist to the wafer by an acid etching process that physically imprints the precise outline of the circuit design into the wafer surface. Current technology enables production quantities (tens of millions) of cmpus with circuit features of 0.18 micron or 1/600<sup>th</sup> the thickness of a human hair. These features can only be viewed through a powerful microscope and their ability to function correctly are due as much to physicists and materials scientists as

<sup>&</sup>lt;sup>9</sup> The PPI has developed and applies quality valuations from hedonic models for several types of computers, printers, and storage devices. See Holdway (1999b).

to engineers and technicians. It is the rapid advances in production technology that enable discrete feature sizes that are beginning to approach the atomic level. In the 1980s many industry observers felt that the laws of physics would not allow semiconductor technology to break the 1.0 micron barrier. Since then the industry has introduced 0.80, 0.50, 0.35, 0.25 and 0.18 micron devices and is currently shifting to 0.13 micron designs. Each shift to a new micron generation allows more features, such as transistors, to be packed into a smaller section of a silicon wafer. As features are packed more tightly together the distance that electrons must travel is reduced, which improves performance.

The production process can also be viewed through analogy. Stencils are widely used to transfer a painted pattern or design onto a surface. In a similar fashion, the electronic circuit pattern is printed on a quartz/chrome mask that functions like a stencil but allows light rather than paint to transfer the circuit design onto the silicon wafer.

As the industry pursues lower cost and better performance, circuit designs have advanced to the point that the wave-height (amplitude) of most common light sources are too large to pass cleanly through the mask. This limitation was supposed to have been one of the laws of physics that would keep producers from breaking the 1.0 micron barrier. With billions of dollars at stake, manufacturers of semiconductor production equipment introduced photolithography designs that utilize a 248 nanometer krypton-fluoride (KrF) excimer light source. Krf's amplitude is short enough to project circuit designs through masks that are designed for 0.18 micron feature sizes. Equipment is currently being installed in domestic semiconductor fabs that use 193 nm argon fluoride (ArF)<sup>11</sup> that will enable a further shrink to 0.13 micron. When demand for circuit designs drop below 0.13 micron, prototypes of 157 nm molecular fluoride are already in the development stage that will eventually enable the production of cmpus several times faster than current designs, while simultaneously reducing unit cost.

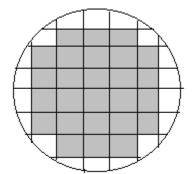

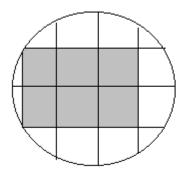

Rather than get bogged down in the unique complexities of semiconductor production processes, I have attempted a couple of crude drawings (figures 1 and 2) that illustrate the general effects of industry shifts to more advanced micron technologies.

<sup>&</sup>lt;sup>10</sup> Primarily phosphorous or boron.

<sup>&</sup>lt;sup>11</sup> ASML, SVG Shoot-out for 157nm IP, Electronic News, 7-12-99, pg. 76.

Figure 1 (0.25 micron design)

Figure 2 (0.35 micron design)

Figures 1 and 2 represent 0.25 and 0.35 micron technology respectively. Wafer diameter is 8" in both processes, but it is clear that the 0.25 micron technology yields more usable cmpu dies (chips) than the 0.35 micron technology. Usable dies<sup>12</sup> are outlined in gray. Notice that the rectangular dies that are on the outer perimeter of the wafer are not fully formed and represent waste. The number of usable die shown in Figures 1 and 2 are for illustrative purposes and do not represent the actual yield improvement made possible by a shift from 0.35 to 0.25 micron technology.

Further details will be provided shortly, but for now let's assume that a producer is manufacturing 100Mhz cmpus using a 0.35 micron technology which yields 6 usable chips as shown in Figure 2. We also assume that each 8" wafer in figure 2 costs the producer \$1,000 including an amortization factor that accounts for plant facilities and all capital equipment used in the production process. Under this scenario each 100Mhz cmpu costs \$166.66 (\$1,000/6). Now suppose that the producer can modify or introduce new production equipment which enables a shift to a 0.25 micron technology as shown in Figure 1. The new technology yields 26 usable cmpus but the cost of each 8" silicon wafer increases from \$1,000 to \$1,500 because of the investment in new capital equipment required to implement the 0.25 micron process. Each cmpu produced at 0.25 microns cost the producer \$57.69 (\$1,500/26), a substantial reduction in unit cost despite the increased cost per wafer. In addition, the 0.25 micron cmpus operate at 133Mhz due to the shorter distance that electrons must travel in the smaller device. The producer has not only lowered unit cost, but now has a faster (better) product to offer buyers. A few liberties were taken with this example to help illustrate one of the fundamental enablers of Moore's Law.

<sup>&</sup>lt;sup>12</sup> I am ignoring defects such as those caused by dust or other impurities that can destroy the tiny circuit connections within the chip.

MicroDesign Resources presents a more elegant and precise description of the impact of shrinking feature size on production cost in their semiannual review of Intel's manufacturing process which is called *Intel Microprocessor Forecast, Product Roadmap, Volumes, Costs, & Prices* (IMF). This resource will be cited frequently because it not only focuses on the most important cmpu producer in the world, but also because the authors (Linley Gwennap and Mel Thompson<sup>13</sup>) have worked for many years in the semiconductor industry as microprocessor designers and product managers. Each edition of IMF devotes a chapter to an analysis of Intel's production costs that help to relate the concepts described above to one of the most important economic forces in the semiconductor industry. For example, table 2 describes the evolution of the Pentium based on data provided by the 3<sup>rd</sup> Edition (1998) of IMF, tables 5-3 and 5-4 pgs 55 and 57.

Table 2

|              | Wafer   | Gross Die | Net Die   | Die         | Package | Total       |

|--------------|---------|-----------|-----------|-------------|---------|-------------|

| MPU/Micron   | Cost    | per Wafer | Per Wafer | Cost        | Cost*   | Chip Cost   |

| Pentium/0.80 | \$1,900 | 80        | 24        | \$80        | \$31    | \$111       |

| Pentium/0.50 | \$2,400 | 175       | 89        | <b>\$27</b> | \$25    | <b>\$52</b> |

| Pentium/0.35 | \$3,000 | 298       | 194       | \$15        | \$25    | \$40        |

\*Includes assembly and test [The production process through Die Cost is normally handled at one of Intel's domestic Fabs (in 1997), but packaging and test is handled at offshore Intel owned facilities primarily located in Malaysia and the Philippines. Offshore packaging and test is not an Intel specific practice but is used by many semiconductor producers to reduce cost.]

Gwennap and Thompson estimate wafer costs<sup>14</sup> by assuming full utilization (a sound assumption for Intel) and depreciate the cost of the fab and production equipment using the 4-year straight line method. The first iteration of the Pentium was introduced in 1993 using a 0.80 micron technology yielding 24 usable die per 8" wafer. Intel shifted Pentium production to 0.50 micron in 1994 which more than tripled the number of good die per wafer to 89 and then to 0.35 micron in 1995/96 which more than doubled good die to 194.

Note that the ratio of net (good) die to gross die per wafer increases at each process shrink. At 0.80 micron, only 30 percent (24/80) of the gross chips were usable, but at 0.35 micron the percent of usable chips jumped to 65 percent (194/298). There are several technical reasons why process shrinks improve the net to gross ratio but one of the most often discussed is defect density. Manufacturers spend millions of dollars to construct clean rooms to help minimize defects in their expensive wafers. These defects are often caused by tiny particles (even dust) that contaminate circuit pathways or features. A dust particle that may seem otherwise insignificant takes on the destructive proportions of a large boulder in the tiny sub-micron world of cmpus and other semiconductor

\_

<sup>&</sup>lt;sup>13</sup> Both authors are regular speakers at the annual Microprocessor Forum attended by most of the mpu producers including Intel, AMD, Texas Instruments, Cyrix, Hitachi, NEC and MIPS.

<sup>&</sup>lt;sup>14</sup> Clean or unprocessed wafers (8") that exclude amortization of fab and production equipment, cost less than \$200. It is the investment in the fab and production equipment that now routinely exceed \$1 billion that drive wafer costs to the levels shown in Table 2. Note that the estimated wafer costs do not include the upfront cost of designing a new microprocessor or developing a new IC process. *IMF* estimates these upfront costs at \$200 million or more, but because of *Intel's huge volumes* they would add *only a few dollars to the unit cost*.

products. Suppose a manufacturer is able to control the number of fatal occurrences of contamination so that they average no more than 10 per wafer. If the manufacturer can shift production to a new generation technology that enables the number of gross die to increase from 100 to 200, then the defect ratio will on average drop from 1 in 10 to 1 in 20. The higher gross number of die made possible by shifting to a more advanced technology, is further enhanced by lower defect densities. In other words, the ratio of net (marketable) Pentiums to gross Pentiums increase as microns decrease.

Drawing from the far right column in table 2, the shift from 0.80 to 0.50 micron reduced unit cost from \$111 to \$52 or 53 percent. Unit costs were reduced again with the shift to 0.35 micron, dropping from \$52 to \$40 or 23 percent. These unit cost reductions were accompanied by equally impressive quality improvements in cmpu performance. The 0.80 micron process yielded 60 and 66Mhz Pentiums, which were accelerated to 75, 90 and 100Mhz with the shift to 0.50 micron. Introduction of 0.35 micron technology enabled a jump to 120 and ultimately to 200Mhz<sup>15</sup>. The rapid transitions from 0.80 to 0.50 to 0.35 micron production technologies occurred over a brief 3 year period (1993-1995) and the pace continues to quicken.

Sematech, an industry research organization has recently changed it's highly regarded roadmap that presents a timetable for the introduction of new process technologies used for planning purposes by semiconductor equipment OEMs. The revised timetable was characterized in Semiconductor Business News, 6-9-99, with the observation that; *In the late 1990s, the pace of process shrinks has accelerated from three-year cycles to two years or less...* <sup>16</sup>. Electronic Buyers News (www.ebonline.com) reported on Intel's comments concerning their next process shrink with the statement, *Intel expects to achieve another 30% reduction in costs from the increased yields in the die shrink by moving to the 0.13- micron generation.*

## **CMPU Quality Change: Three Paths**

At this point, the reader may understandably, but incorrectly, conclude that unit costs for cmpus are inevitably reduced over time. As long as we refer to the same cmpu generation and investments in more advanced production equipment continue to provide positive returns, speeds will increase and unit costs should decline. However, unit costs are likely to initially increase when new generation cmpus are introduced, and then

\_

<sup>&</sup>lt;sup>15</sup> Multiple speed ratings produced within a single micron process are a technical issue based partly on the amount of heat generated by the cmpu at a specified speed. Thermal tolerances are established by engineers to ensure product reliability. Tolerances must take into account several factors including voltage, resistance, and projected speed ratings because, in a given process, an increase in any of the three will increase heat. The photolithography process, while extremely accurate by most measures, does not transfer circuit designs to silicon with zero variance. To the extent that a slight imperfection/irregularity is created in a circuit path, additional resistance to the flow of electrons may be introduced. This additional resistance creates more heat at a given operating speed. Therefore in the 0.80 micron process, tiny imperfections may cause one cmpu to reach its thermal limit at 60Mhz, while an otherwise identical cmpu is able to remain within tolerance at 66Mhz.

<sup>&</sup>lt;sup>16</sup> Robert Lineback, Semiconductor Business News, as reported by Electronic Buyers News Onlinewww.ebnonline.com/story/OEG19990609S0007.

resume a downward trend. Additional cost may also be incurred when an existing generation is modified as was the case when the Pentium was redesigned in 1996 to include new instructions that improved integer performance. The redesigned Pentium was called the Pentium MMX and because of its larger L1 cache (L1 will be described later), was physically larger and more costly than the Pentium. Intel attempted to compensate for the size differential by shifting from a 0.35 to a 0.28 micron process which was only partially successful.

The MMX represented more of a design tweak, while the Pentium II (introduced in 1997) is an example of a new generation product. The Pentium II was initially produced in the same 0.28 micron process used for the MMX, but the Pentium II had so many additional features that it required 7.5 million transistors compared to the 5.5 million in the MMX. Without the benefit of a more advanced input technology, the Pentium II was physically larger than the Pentium/MMX which resulted in less good die per wafer and higher unit production cost. Table 3 extends the data provided in table 2 to include the MMX and Pentium II.

Table 3

|                  | Wafer   | Gross Die | Net Die   | Die  | Package | Total     |

|------------------|---------|-----------|-----------|------|---------|-----------|

| MPU/Micron       | Cost    | per Wafer | per Wafer | Cost | Cost*   | Chip Cost |

| Pentium/0.80     | \$1,900 | 80        | 24        | \$80 | \$31    | \$111     |

| Pentium/0.50     | \$2,400 | 175       | 89        | \$27 | \$25    | \$52      |

| Pentium/0.35     | \$3,000 | 298       | 194       | \$15 | \$25    | \$40      |

| Pentium MMX/0.28 | \$2,800 | 206       | 125       | \$22 | \$21    | \$43      |

| Pentium II/0.28* | \$2,800 | 123       | 58        | \$49 | \$31    | \$80      |

<sup>\*</sup>The Pentium II was introduced with a new package called slot 1 which included a 512K L2 Cache. This additional feature (not available with the Pentium/MMX) has been excluded to keep the cost estimates reasonably comparable. Pentiums were also designed to work with L2 caches, but they were normally provided as a separate device (and cost) by the motherboard manufacturer.

Note that Gwennap and Thompson estimate total amortized wafer cost for the 0.28 micron MMX and Pentium II dropped relative to the predecessor 0.35 micron wafer cost. The reduced wafer cost estimate is due to Intel's decision to refit existing 0.35 micron production facilities to make them 0.28 micron capable. By modifying existing facilities and equipment that were already partially amortized Intel was able to reduce wafer cost relative to the construction of a new production facility. Making broad generalizations for an industry as complex as semiconductors is probably ill-advised and can easily lead to embarrassing contradictions. Nevertheless, wafer costs should increase as multigenerational production shifts occur, but may actually decrease when existing facilities are modified to implement a single generation shift.

Returning to the example of the MMX and Pentium II, while the shift from 0.35 to 0.28 micron reduced wafer cost, unit cost is actually higher for MMX and Pentium II because of their relative bulk. The reduced yield that is directly caused by the physically larger cmpus is pinpointed by Gwennap and Thompson in table 4 through destructive analysis (opening the package that seals and protects the cmpu).

Table 4

| MPU/Production Process   | Die Size           |

|--------------------------|--------------------|

| Pentium @ 0.80 micron    | 294mm <sup>2</sup> |

| Pentium @ 0.50 micron    | 148mm <sup>2</sup> |

| Pentium @ 0.35 micron    | 91mm <sup>2</sup>  |

| Pentium MMX @0.28 micron | 128mm <sup>2</sup> |

| Pentium II @ 0.28 micron | 203mm <sup>2</sup> |

The data presented in table 4 can be viewed as a kind of forensic trail that enables us to better understand how input quantities and costs are affected by the three primary types of cmpu quality change. These changes are identified as Types 1, 2 and 3.

**Type 1:** The first three Pentium entries in table 4 are examples of type 1 quality changes. As the input technology advances from 0.80 to 0.50 and finally to 0.35 micron, the physical size of the chip is progressively reduced which directly lowers cost and improves quality. Type 1 changes refer to input quantity (technology) changes that generally result in lower unit cost and better quality, in this case speed. Type 1 changes DO NOT include changes to an MPU's architecture or design<sup>17</sup>.

Type 2: The fourth entry is the Pentium MMX which represents a type 2 quality change. The Pentium's architecture was altered with MMX in two important ways. First, 57 new instructions were added that were specific to multimedia integer performance. The second change doubled the L1 cache size. This latter change was the primary reason that the number of transistors jumped 36 percent relative to the Pentium (3.3 vs 5.5 million). A type 2 quality change includes architectural modifications that do not involve a redesign of core logic functions. In other words, type 2 changes DO NOT include modifications that define a new generation cmpu. Marginal changes to input quantities under the type 2 scenario do not have a fixed impact on unit cost. Unit costs, depending on the nature of the design change and the production process used, can decline, increase or, though unlikely, remain constant.

**Type 3:** The Pentium II entry is an example of a type 3 quality change. Architectural differences between the Pentium II and the Pentium/MMX are so significant that they represent a new class of cmpu. Some of the most important distinguishing characteristics of the Pentium II architecture are described below.

Dynamic Execution Technology: Enables out of order and speculative execution. Dynamic execution

is designed to minimize linear constraints that are inevitable in software programs. This new

technology enables up to four instructions per clock cycle compared to the Pentium's two instructions

per cycle.

<sup>&</sup>lt;sup>17</sup> The Pentium underwent some minor peripheral changes, the most notable a reduction in voltage from its initial 5 volts to 3.3 volts. The voltage reduction was made possible by smaller feature sizes and should be considered a quality improvement due to improved energy efficiency and lower heat dissipation. This type of quality improvement is similar to the improvement in speed that is, in effect, a byproduct of the input quantity change that reduced the cmpus physical dimensions. Several other improvements were made that had the effect of removing certain latencies in the Pentium's circuit design. These improvements were of a highly technical nature and beyond the scope of this paper. (See Intel Technology Journal 3Q97 for details).

- Superpipelining: The Pentium II's pipeline (think of pipelines as an instruction queue) extends to 12 stages compared to the Pentium's relatively small 5 stage pipeline. The practical consequence of deeper pipelines is the ability to achieve higher clock speeds using the same manufacturing process. Intel claims that the Pentium II's pipeline enables up to a 50 percent Mhz increase relative to the Pentium, even if the same micron production process is used for both cmpus.

- Dual Independent Bus Architecture: Essentially provides a dedicated bus to the L2 cache. This enables a much greater cache throughput. For example the Pentium/MMX was limited to a 66Mhz shared L2/system bus, while the Pentium II's dedicated L2 bus could be clocked at half the MPU speed (i.e. a 300Mhz Pentium II's L2 cache runs at 150Mhz).

These architectural improvements are only a part of a more comprehensive list described by Intel in their *Pentium II Processor Performance Brief*, January 1998 (order # 243336-004). A type 3 quality change always includes fundamental changes in core logic design. The new mix of input quantities usually result in higher unit cost relative to the previous generation cmpu. Note that the higher unit cost of type 3 change tends to be quickly offset with more advanced input technologies as a series of type 1 changes progressively shrink the physical dimensions of the new generation cmpu. For example, Intel introduced the Pentium II at 0.28 microns in May 1997, but then shifted to a 0.25 micron production process eight months later. The new process decreased unit cost 18 30 percent from \$80 to \$56. Another benefit of this type 1 quality change was that the Pentium II's maximum speed increased from 300Mhz to 450Mhz.

The three types of quality change described are the most common examples that are likely to be encountered in a price index covering cmpus. However, before proceeding to the next section, additional context is needed for type 2 changes. Due to industry hype and America's love affair with things that are new and improved it is easy to fall into the trap of assuming that cmpus only improve over time. This assumption, if blindly adhered to, can distort perceptions about how technology is wielded by producers to protect or expand market share. For example, speed or Mhz ratings continue to rapidly increase and if used as a quality benchmark would imply an unbroken upward quality trend. One could ask the question, if other metrics besides the superficial speed ratings were used, would the quality trend maintain this unbroken upward path?

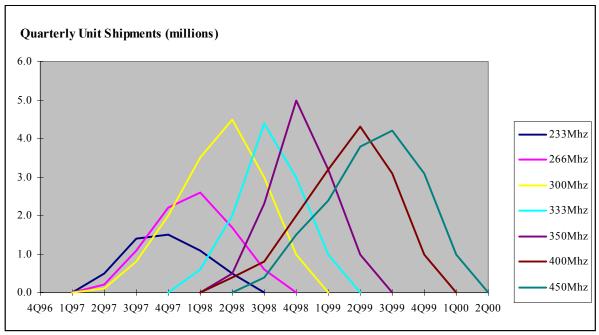

To illustrate, we need only review Intel's Pentium II product lineup. The Pentium II was introduced at 233 and 266Mhz in May 1997 at \$636 and \$775 respectively<sup>19</sup>. By May 1998, the prices for these cmpus had fallen to \$198 and \$246, but Intel's Pentium II offerings had expanded to include additional speed ratings shown in table 5.

#### Table 5

<sup>&</sup>lt;sup>18</sup> The 0.25 micron process increased the yield or net die per wafer from 58 to 120. Net die increased more than 100 percent, but total amortized wafer cost for the new process increased only 21 percent (from \$2,800 to \$3,400). It is no wonder that Intel plowed back over \$4 billion in capital expenditures in 1997 and \$5 billion in 1998 to convert to the 0.25 micron process. *IMF*,

tbl. 5-4, pg. 57. <sup>19</sup> *IMF*, tbl. A-3, pg. 114.

| 0.28 Micron |

|-------------|-------------|-------------|-------------|-------------|

| PII-233     | PII-266     | CPII-266    | PII-300     | PII-333     |

| \$198       | \$246       | \$155       | \$375       | \$492       |

*Prices are based on 1,000 lot quantities effective 5-98.*

The most interesting entry in table 5 is the CPII-266Mhz that Intel introduced on 5-98 at \$155. All cmpus shown were produced in the same 0.28 micron process and therefore have approximately the same die cost. The CPII is actually a new version of the Pentium II that has been stripped of all L2 cache to reduce package cost (a type 2 quality change). Intel called this modified Pentium II the "Celeron" and introduced it to maintain market share in the low-margin but high volume segment<sup>20</sup> of the PC market. To the unwary buyer, the Celeron ran at a respectable 266Mhz. However, with no L2 cache, the Celeron was widely reported in various industry journals such as PC Magazine to have lower performance than the PREVIOUS generation 233 Mhz Pentium MMX. By Intel's own admission, the elimination of the L2 cache in the 266Mhz Celeron reduced performance by 30 percent<sup>21</sup> relative to the 266Mhz Pentium II with an L2 cache.

A more complex example of a quality decline can be observed with Intel's 486 cmpu family. One of the big improvements in the 486 relative to its predecessor product, the 386, was the addition of a floating point unit (FPU). FPUs enable much faster calculations of formulas that involve fractional numbers which are commonplace in engineering, drawing, statistical and multimedia applications. Prior to the 486, if a consumer needed floating point performance they had to buy a separate specialized chip in addition to the cmpu. Intel produced two versions of the 486, the DX and the SX. The DX was introduced in 1989 at more than \$900 which limited sales to the relatively low volume high performance segment of the PC market. In order to penetrate the high volume low end of the PC market Intel needed to reduce prices while simultaneously displacing its previous generation 386<sup>22</sup>. So, in 1991 Intel introduced the 486 SX. The 486 DX and SX were identical, except that Intel disabled<sup>23</sup> the FPU in the SX to rationalize a lower price. The SX enabled Intel to offer a product to the low end market without cannibalizing high margin DX sales. Since the SX was really a DX with the FPU disabled at the factory, accounting for quality change based on a change in input quantities is problematic. *IMF* estimates that \$1.5 billion of SX chips were sold between 1Q93 and 2Q95. Unfortunately their revenue data does not capture pre-1993 sales so much of the total SX revenue is missing. Even though revenues are incomplete, it is clear that despite reduced capability the SX was a successful product.

One last example to show that cmpu quality declines are no fluke can be found in Intel's first 32 bit cmpu, the 386.

<sup>&</sup>lt;sup>20</sup> It is also pertinent that Intel's competition (i.e. AMD and Cyrix) were gaining market share in this segment.

<sup>&</sup>lt;sup>21</sup> Based on Intel's composite performance benchmark which they call I-Comp. The 266Mhz Pentium II was rated by Intel at 3.03 I-Comps, but Intel could only coax 2.13 I-Comps from the 266Mhz Celeron.

<sup>&</sup>lt;sup>22</sup> One of the reasons Intel wanted to steer the PC market away from the 386 to the 486 was because AMD offered a competing 386. In fact AMD offered a less expensive and faster 386 (40Mhz vs 33Mhz).

<sup>&</sup>lt;sup>23</sup> The emasculation of the 486 was well documented in technical journals such as the *PC Processors Guide* @ http://www.x86.org/articles/computalk/help.htm which stated that, *Unbeknownst to the consumer, the 80486 SX was an 80486 DX with a non-functional math unit (though later versions of the chip actually removed the math unit).*

The 386, like the 486, were offered in a DX and SX version. The DX was introduced in 1985, followed by the SX in 1988. As in the previous example, Intel felt the need to move the 386 from the relatively low volume high performance segment of the market to the high volume low end of the market without sacrificing the DX's high profit margins<sup>24</sup>. Intel wanted to protect high margin DX sales by introducing a 386 with lower performance characteristics which they called the SX. Unlike the 486, the 386 had no FPU to disable. Instead, Intel decided to go back to the old 16 bit system bus used in the predecessor 286. Of course mating the 32 bit 386 with a 16 bit system bus seems a bit odd, but was successful in the marketplace. Essentially Intel was offering a cmpu that could internally process data 32 bits at a time, but could only communicate with other system components, such as DRAM, 16 bits at a time. Intel's I-Comp performance benchmark<sup>25</sup> showed that their re-introduction of old 16 bit technology for the SX reduced performance 26 percent relative to the DX.

These examples have been presented for two reasons. The first is to show that cmpu performance has not followed an unbroken upward path over time despite the general accuracy and popular acceptance of Moore's Law. The second is to point out that if the PPI adopts new procedures for valuing cmpu quality improvements without also capturing quality declines, then price measurement will have an unavoidable downward bias of unknown magnitude. This caveat is also relevant when applied to alternative cmpu indexes based on average price data that are produced outside of BLS from time to time.

It would be disingenuous to imply that the PPI has been able to properly value and account for technological change in its cmpu price measurements. The standard PPI methodologies for valuing quality change is rather limited when faced with quality improvements that are accompanied by reduced input costs due to shifts in the production function.

The remainder of this paper will describe possible solutions to the problem of valuing cmpu technological change. One of the criteria for an acceptable alternative is that it must enable the PPI to calculate reasonable and consistent estimates for the value of technical change so that the residual price relative yields a measure of pure price change.

#### **Standard PPI Quality Adjustment Procedures**

Choosing among standard PPI methodologies to adjust cmpu price relatives for violations of the targeted Fixed-Input Output Price Index (FIOPI) model is a conceptually difficult obstacle. To cut to the quick, I will use simple price relative calculations to clearly show the consequences of choosing among standard PPI procedures to value quality change. The PPI's Laspeyres formula is ignored because it is needlessly cumbersome for this purpose and more useful for comparing index formula aggregation effects which are beyond the scope of this paper. The

<sup>-</sup>

<sup>&</sup>lt;sup>24</sup> The 386DX cost Intel \$141 and was sold for \$900 according to *Inside Intel*, pg. 282.

<sup>&</sup>lt;sup>25</sup> The University of Berkeley maintains a web site @www.infopad.eecs.berkeley.edu/CIC/suimmary that provides a history of Intel performance benchmarks that are no longer directly available from Intel. According to this site, Intel rated the 25Mhz 386 DX at 49 I-Comps and the 25Mhz SX at 39 I-Comps. Note that I-Comps are recalibrated over time so that they are often not comparable from one cmpu generation to the next.

examples are limited to the most common type 1 quality changes because if an acceptable solution<sup>26</sup> for type 1 is adopted, then it should also be applicable to type 2 and 3 changes.

The pricing data shown in table 6 overlap different input technologies and will be used to contrast the differences among standard PPI quality adjustment procedures on price relative calculations at the item level.

\*Table 6

|        | (0) (1             | (())()             | 0014          | 12014         |

|--------|--------------------|--------------------|---------------|---------------|

|        | 60Mhz              | 66Mhz              | 90Mhz         | 120Mhz        |

|        | (0.80 micron)      | (0.80 micron)      | (0.50 micron) | (0.35 micron) |

| 2Q93   | \$878              | \$965              | N/A           | N/A           |

| 2Q94   | \$675              | \$750              | \$849         | N/A           |

| May 95 | \$245              | \$260              | \$377         | \$935         |

| Nov 95 | \$230 discontinued | \$230 discontinued | \$247         | \$357         |

<sup>\*</sup>Prices are based on 1,000 unit order size. From *IMF*, 3<sup>rd</sup> Ed., Tbl. A2, pg. 113.

We can further simplify with the assumption that the domestic cmpu universe was limited to 60 and 66Mhz Pentiums in 1993. The PPI samples this universe and disaggregates to the 66Mhz version. Tracking price change for this cmpu to its end-of-life on Nov 95 is straightforward. Based on the prices in table 6, example A shows that the PPI's Microprocessor index would have dropped 76 percent over this 2 ½ year period.

Example A:

$$P66/P66 = [1 - 230/965] = -76\%$$

However, since both 60 and 66Mhz are discontinued in Nov. 1995, what replacement cmpu should be selected to maintain index continuity? The closest match is 90Mhz produced with the more advanced 0.50 micron input technology. One of the problems presented by the proposed substitute is that it represents a shift in the production possibilities curve. In other words, the assumption of fixed input quantities, including technology, that is basic to the PPI's target FIOPI model has been violated. The correct adjustment for this violation is one of the most difficult challenges faced by PPI analysts. Standard PPI methodology offers several possible techniques that will theoretically address this situation depending on the amount of information that is available<sup>27</sup>.

#### **Direct Compare**

For example, if the discontinued 66Mhz and its 90Mhz replacement are deemed to be very similar and no cost information is available, perhaps a direct comparison is appropriate. Using direct comparison, the \$17 premium for the replacement results in a 7.3 percent increase in example B.

Example B:

$$P90/P66 = [1-247/230] = +7.3\%$$

On the other hand, the replacement has a speed rating that is 36 percent faster than its predecessor. This is hardly an insignificant difference and is completely ignored in a direct comparison. If cmpu output were defined in terms of Mhz, then the PPI's use of direct comparison will grossly understate output.

<sup>&</sup>lt;sup>26</sup> Any proposed methodology designed to value cmpu quality change must take into account a resource constrained operational environment that may affect the choice of the "best" solution.

<sup>&</sup>lt;sup>27</sup> Gousen, Monk, and Gerduk provide an overview of standard QA procedures in *Producer Price Measurement, Concepts and*

#### **Direct Link**

Standard PPI methodology also includes a direct link procedure to compare prices of a discontinued product and its replacement. With direct link, an implicit assumption is made that the entire price difference between the obsolete product and its replacement is due to quality change. In other words if we view quality change strictly in terms of Mhz, then direct link treats the \$17 price premium for the replacement as a valuation for the increased quantity of Mhz. The direct link adjusted price relative is shown in example C.

Direct link is often used when the PPI analyst does not have the information required to estimate an explicit quality valuation and the difference between the old and new products are significant enough that a direct comparison appears to be inappropriate. The direct link, if used frequently for products like cmpus that undergo significant and rapid change, will almost certainly introduce bias of unknown magnitude and direction into the PPI. The problem is an old one, but takes on added importance as "high-tech" products continue to grow relative to GDP.

## **Explicit Quality Adjustment**

The preferred methodology in the PPI's quality adjustment arsenal is an explicit valuation of technical change. Using the previous example of the 66Mhz to 90Mhz transition, the PPI analyst would ask the reporter to provide an estimate for the change in marginal cost that is directly tied to the 24Mhz difference between old and new products. In a output index, significant improvements in quality are assumed to require additional inputs and it is the cost of additional inputs that are used to value related quality improvements. If the opposite occurs and quality declines significantly, say from 90Mhz to 66Mhz, then it is assumed that input quantities have been reduced and the cost reduction associated with new input requirements are used to value quality decline. In both cases a violation of the FIOPI model has occurred.

The methodology of using changes in marginal input cost to value quality change, in theory, returns the PPI to the original base period production possibilities curve. Some may say that we have "fixed" the violation of the FIOPI model when quality adjustment procedures are applied correctly. To illustrate, let's pretend that we have not yet reached a transition point in which the industrial revolution is giving way to the information technology revolution. The traditional industrial sector is generally more amenable to the PPI's explicit quality adjustment assumptions. More specifically, in the short term, measurements of increased quality are positively correlated with more costly inputs (higher marginal cost). Under this scenario, if the PPI needs to replace 66Mhz with a 90Mhz and we discover that the 90Mhz product has an additional marginal cost of \$50 then the PPI analyst is on solid footing. Applying standard explicit quality adjustment procedures, the price relative is simply recalculated in example D to account for the increased marginal cost that is tied to the 24Mhz improvement.

Example D: \$P90-VQA/\$P66= [1-(\$247-\$50)/\$230]=1-\$197/\$230= -14.3%

In example D the effect of the \$50 dollar valuation for quality improvement is to transform a 7 percent increase in the directly compared nominal relative (example B) into a 14 percent decline in the explicit quality adjusted price relative. As long as the change in marginal cost exceeds the difference in nominal prices, then a pure price decline has occurred. If the increase in marginal cost is less than the increase in nominal prices then a pure price increase has occurred and if the change in marginal cost is equal to the difference in nominal prices then no change will be recorded (equivalent in effect to a direct link).

In the context of a deflator, because the PPI's explicit quality procedure for the new product "adjusts" the price relative from a nominal increase to a decline, the "real" measure of cmpu output increases. On the other hand, direct comparison makes no adjustment for technological change and simply measures the nominal price increase which decreases the real measure of cmpu output. In this case we know that the valuation of technology change embedded in the 90Mhz cmpu exceeds its price premium relative to 66 Mhz and therefore represents more output. Thus, the explicit quality adjustment procedure provides a closer approximation for measures of real cmpu output.

But if we try to use the explicit quality adjustment procedure to "fix" violations of the FIOPI model when quality improvements are accompanied by declining resource costs then we run into trouble. Using the rationale in the previous example, if technological improvements result in lower unit input costs, then the amount of this reduction should be added to rather than subtracted from the numerator of the price comparison. Or, if a technological decline results in higher input costs, then the amount of the increase should be subtracted from the price comparison. Both instances, using circular logic, should return the PPI to the original production possibilities curve.

The real effect would be as follows: The 66Mhz cmpu has reached end-of-life and is replaced by 90Mhz to maintain index continuity. The reporter informs the PPI analyst that the 90Mhz cost \$50 less than the 66Mhz version. If we blindly follow the standard explicit quality adjustment formula then the adjusted price relative comparison will take the form in example E resulting in a 29 percent price increase.

Remember that the nominal price increase associated with new cmpu is only 7 percent. We can make the example more extreme if the reporter decides to pass on half of the cost savings to the consumer by offering the 90Mhz for \$222 instead of \$247. The adjusted price relative is restated to show this in example. F.

In example F the nominal price change is a negative 3.5 percent (1-\$222/\$230 = -3.5), but the PPI "quality-adjustment" transforms the nominal decline into an 18 percent increase for the faster, cheaper replacement.

Explicit quality adjustment will continue to be used extensively in the PPI, but one can question if this procedure "fixes" violations of the FIOPI model for the rapidly growing information technology sector. As high technology

industries continue to grow in importance, many of the tools and concepts used by PPI analysts may need to be refined if we are to properly account for rapid quality change. I do not mean to imply that all information technology related industries constantly improve quality while simultaneously reducing unit cost. However, in addition to semiconductors, other high profile industries such as computers and telecommunications continue to offer greater functionality and performance while lowering unit production costs relative to predecessor products.

A case can be made that semiconductors take on the role of mother and computer and telecommunication products the role of children. The Semiconductor Industry Association's (SIA) 1999 directory estimates that computers contain more than half the semiconductors sold worldwide. Advances in semiconductors that can be characterized as "better and cheaper" are quickly adopted by computer and telecommunication equipment manufacturers to produce better products with lower input costs. No one questions that technical capabilities of computers have advanced tremendously over the last decade while prices have plunged<sup>28</sup>. To the extent that advanced procedures such as hedonic models are used to value quality change in computers, but not semiconductors, measures of output and productivity at the industry level are distorted. One of the consequences of this distortion is that real computer net output has been overstated due to an understatement of their most important input, semiconductors.

## **Alternative Quality Adjustment Methodologies**

The challenge of accounting for new input technologies that reduce unit cost while improving quality was originally addressed by the PPI in the late 1980s when hedonic regression techniques were applied to an experimental computer index<sup>29</sup>. After careful review of the performance and production worthiness of the experimental indexes, the PPI officially began publication of Computer industry price indexes on December 1990. These were the first indexes to be integrated into the PPI structure that employed hedonic models to value quality change. In the field of government produced economic data, the PPI was not entering uncharted territory. The BEA introduced hedonic models<sup>30</sup> into the NIPAs to produce constant quality price indexes for computers in 1985. BEA's chief economist at the time, Jack Triplett, presents a clear description of the conceptual framework for applying hedonic techniques in *The Economic Interpretation of Hedonic Models*, Survey of Current Business, Jan. 1986.

The introduction of hedonic models into the NIPAs did not go unchallenged. Jorgenson and Stiroh (1994) present an interesting description of the controversy in *Computers and Growth*. They describe a "heated exchange" between BEA and Edward Dennison, *one of the founders of NIPA methodology in the 1950s and head of national*

\_

<sup>&</sup>lt;sup>28</sup> PC Magazine (8-88) reviewed a Compaq Deskpro 386S PC equipped with a 16Mhz 386, 1MB of DRAM, 40MB hard drive and DOS 3.1 that sold for the astronomical (by today's standards) **\$5,199**. Compaq currently (1999) offers desktop PCs with a Pentium III 500Mhz, 64MB of SDRAM, DVD drive, 17" Monitor, 3D Video capability, sound card w/speakers, MS Office and one year on-site warranty for around \$2,000.

<sup>&</sup>lt;sup>29</sup> Sinclair, Catron, *An Experimental Price Index for the Computer Industry*, Monthly Labor Review, Bureau of Labor Statistics, Oct. 1990, pgs. 16-24.

<sup>&</sup>lt;sup>30</sup> BEA's model was based on a IBM study, *Quality-Adjusted Price Indexes for Computer Processors and Selected Peripheral Equipment*, that was presented in the Jan. 1986 issue of Survey of Current Business, pgs. 41-50.

accounts at BEA from 1979 to 1982. Dennison attacked the use of hedonics and argued vigorously against the introduction of constant quality indices into NIPA. Triplett provided some of the key counterpoints to Dennison's position, particularly that correctly specified<sup>31</sup> models not only measured changes in consumer utility but also changes in marginal cost. Triplett went on to say that ...implicit prices measure value on both sides of the market, as do any prices.

If Dennison had prevailed, then one can assume (in a worst case scenario) that the BEA would have continued to estimate computer industry output by measuring changes in nominal revenues. Measuring changes in computer output by changes in nominal revenue implicitly assumes a price index of 1 for the three decades of tremendous advances in computer technology prior to 1985. This of course is a difficult position to defend, but since the PPI did not introduce its own computer price index until 1990, the BEA had little choice but to develop an alternative.

## **Applying Hedonic Techniques in the PPI**

The PPI's implementation of hedonics differs from the BEA in that price indexes are not directly calculated from a hedonic model based on pooled data and time dummy variables. Instead the PPI builds cross-sectional models to calculate values or implicit prices of computer characteristics. These values are then used to adjust prices reported to the PPI by producers when the characteristics of their sampled products change. Hedonic models and their supporting databases are updated on a regular basis (quarterly for desktop computers), to account for the rapid introduction of new characteristics.

Unfortunately correctly specified hedonic models for dynamic products can be elusive as technology induced disequilibriums may cause independent variables to have different interpretations for different observations. Comprehensive industry knowledge is one of the most important prerequisites in developing correctly specified models for technologically complex products. Otherwise, how do you judge the suitability of a supporting database (they are often expensive)? Even with a detailed understanding of technological features and how they interact, the availability of an appropriate supporting database is a major problem. This last point is not particularly newsworthy to anyone that has developed a hedonic model for high-tech products, but I mention the issue because it has a special relevance for cmpus.

I have no doubt that BEA's hedonic model for cmpus (see footnote 4) was supported by the required detailed product knowledge. But I do question the use of models based on long-term pooled databases within the PPI to adjust directly reported producer prices for current period quality change. The specifics of the problem are best presented through a brief review of commonly available cmpu characteristics. Rather than analyze each of the characteristics in BEA's model, the review is limited to the Mhz and transistor characteristics. Mhz and transistors are two of the most common and accurately identified features likely to be available in a supporting database.

<sup>&</sup>lt;sup>31</sup> A correctly specified hedonic model is a reference to the selection of independent variables (product characteristics) that represent both outputs and inputs. Outputs absorb resources and inputs provide user value.

#### **Interpreting the Mhz Characteristic**

Mhz is often accepted as a measure of relative performance and was used as such in the BEA model. Mhz is also referred to as clock frequency which in turn is controlled by a small crystal that pulses at a steady frequency (or clock ticks). For each clock tick some action(s) can take place inside the cmpu, so as the frequency increases, more clock ticks are available per second to process data. For example, a 500Mhz cmpu has 500 million clock ticks available per second. In the world of cmpus, speed is the coin of the realm. A cmpu that can execute more instructions in a set period of time is able to run software more efficiently and therefore command a price premium relative to slower cmpus. However, MHz can be a misleading metric if more than one cmpu type, or generation is included in the same model. A quick look at Mhz ratings using Intel's 386-33Mhz as a baseline should help illustrate the problem.

Table 7

| MPU Generations | Mhz | % change in Mhz |

|-----------------|-----|-----------------|

| 386             | 33  |                 |

| 486             | 66  | 100             |

| Pentium         | 133 | 300             |

| Pentium II      | 450 | 1,263           |

While it is clear that Mhz has increased rapidly from the 386 to the Pentium II, it still is a poor measure for the real increase in the speed of instruction execution as we progress through succeeding generations. The following is somewhat technical but necessary to understand the weakness of Mhz as a consistent measure of relative performance.

The 386 did not have a pipeline (a method of queuing instructions) which forced delays in the flow of instructions to its execution unit. In other words the 386 was sub-scalar and limited to about 0.8 executions per Mhz or clock tick. The 486 introduced a small pipeline which theoretically enabled one execution per cycle, the first scalar Intel cmpu. The Pentium introduced dual pipelines and execution units as well as branch prediction which enabled a maximum of two instruction executions per cycle, the first superscalar Intel cmpu. And finally, the Pentium II added<sup>32</sup> superpipelining, out of order and speculative execution which enabled a maximum of four instructions per cycle.

Using executions per cycle information, Table 7 data is adjusted in Table 8 to reflect the impact of these architectural changes<sup>33</sup>.

Table 8

<sup>32</sup> The Pentium Pro was actually the first cmpu (1995) to introduce out of order and speculative execution, but is not included here due to technological tradeoffs in its design that would add unnecessary complexity to the examples.

<sup>&</sup>lt;sup>33</sup> The architectural improvements described are key to understanding and quantifying their effect on Mhz. Unfortunately, most databases, even expensive ones, do not provide the level of technical detail required to properly specify a cmpu model. I may be proven wrong on this at some point. However, if this happy event should occur, there is the still the matter of limited observations that present another hurdle that would be difficult to overcome in a properly specified model.

| 386        | 33  |       | 26    | -21   |

|------------|-----|-------|-------|-------|

| 486        | 66  | 100   | 66    | 153   |

| Pentium    | 133 | 300   | 266   | 923   |

| Pentium II | 450 | 1,263 | 1,800 | 6,823 |

<sup>\*</sup>Executions per cycle multiplied by the rated Mhz, for example the Pentium II's adjusted Mhz is (450 \* 4 executions per Mhz=1,800)

The data in table 8 clearly shows that if unadjusted Mhz is used in a model that includes more than one cmpu generation, then it is an unstable explanatory variable. The degree of instability (if history is any guide) will increase at an accelerated rate as the time span covered by a pooled database increases. The problem with specifying Mhz in a hedonic model is that it is really a proxy variable for other characteristics that are generally not included in supporting databases. For example, changes in Mhz for early generation cmpus such as the 8086, 286 and 386 (all referenced in the BEA model), are primarily a function of declining feature size enabled by new input technologies. This is a bit oversimplified, but the performance slope should be reasonably stable and linear as long as Mhz proxies similar, but unobserved characteristics. On the other hand, the 486, Pentium and Pentium II introduced new unobserved characteristics such as pipelines, register renaming, out of order execution and many other performance enhancing technologies. For these latter generations, Mhz takes on a new role as a proxy variable, because in addition to smaller feature size, Mhz is now a function of new technologies which change its performance slope dramatically. Proxy variables are particularly hazardous in pooled models that are used to investigate price/characteristic relationships for products that undergo rapid technological change. Even products that exhibit a slower rate of change require vigilance when proxy variables are employed. Triplett describes the use of weight as a proxy variable in early hedonic studies on automobiles. Weight was used as a proxy for the "true" characteristics that may have been unavailable or difficult to individually measure. Triplett describes the problem as follows... Use of a proxy variable, however, introduces the possibility of error whenever the relation between the proxy and the true variables change, and one can never be entirely sure whether such shifts have occurred.34

<sup>&</sup>lt;sup>34</sup> Economic Interpretation of Hedonic Models, pg. 38, Current Survey of Business, January 1986.

#### **Interpreting the Transistors Characteristic**

Transistors are another popular variable used to quantify technological change and were included in the BEA model. This variable is also unstable over extended periods as a measure of relative quality change. If transistor counts are precisely defined, it is true that as the number of transistors increase and as their physical dimensions decrease, performance is enhanced. However, total transistor counts quoted by Intel and others do not always distinguish between transistors dedicated to logic and those dedicated to on-board memory (L1 cache). The distinction between transistors used for logic and those used for cache is important as will be shown.

Early generation cmpus (prior to the 486) used transistors primarily to form logic arrays that enabled them to process instructions and perform useful work. These early devices processed data/instructions (D/I) more slowly than system memory could deliver D/I. In other words, DRAM speed was sufficient to keep early cmpus "fed" with enough D/I that most performance bottlenecks were internal<sup>35</sup> to the cmpu. Starting with the 486 generation, cmpus could process D/I at a rate that substantially exceeded the speed of DRAM. The 486 and ensuing generations have a voracious appetite for data and DRAM was simply too slow to keep the new cmpus "fed". This performance bottleneck, absent a technological solution, would cause cmpus to stall as they had to wait on D/I before completing work in progress. Producers of cmpus were concerned because their new generation products were running into a performance brick wall caused by other system components. As long as DRAM set the performance ceiling, why would anyone pay a premium for a new relatively expensive 486 if they could get the same performance from a 386?

Producers devised a clever way to get around this performance barrier by adding small chunks of very fast memory directly into the integrated circuit design of their chips. This type of memory is generally known as L1 cache and requires vast amounts of transistors to implement. L1 cache operates at the same speed as the cmpu, but it can only hold a tiny amount (8 Kilobytes for the 486) of D/I relative to system memory. Cmpu producers placed stringent limits on the size of L1 cache for two reasons. The first was to minimize the unit cost of their new products. The second reason is not as transparent, but far more interesting. Savvy consumers could ask the logical question, if L1 cache has such a low capacity for holding D/I, how can it possibly make that much difference in removing the performance bottleneck presented by system memory? The answer is that L1 does not remove the entire bottleneck, but through the use of algorithms can eliminate 80-85 percent<sup>36</sup> of cmpu stalls that previously occurred as the result of accesses to system memory. The ability of producers to do more with less is based on the knowledge that most software requests for D/I are predictable. A software program may require several megabytes of DRAM to store all of its components and functionality, but most D/I requests are contiguous. In other words, if a function is provided by first executing instruction A, followed by B and then C, L1 cache need only grab B and

<sup>&</sup>lt;sup>35</sup> I am ignoring other types of system interactions such as cmpus and disk drives.

<sup>&</sup>lt;sup>36</sup> The percent estimate is based on synthesized tests performed by Intel to determine the percent of cache hits compared to cache misses for instructions that need to be loaded into the cmpu pipeline. The percent can vary according to the algorithm

C, while A is executing. When the cmpu is finished with instruction A, B and C are conveniently waiting in fast L1 cache for immediate access. However, if execution patterns are not correctly predicted by algorithms, then L1 cache provides little if any benefit. Let's say instruction A is followed by S and then by G. Since S and G are not contiguous with A, the algorithm used by the cmpu, may incorrectly load instructions B and C. This is called a cache miss and requires the cmpu to look for the S and G instructions in relatively slow system memory causing a delay.

The main point is that the algorithms used in L1 cache are so efficient at predicting software behavior that cache hits are far more likely than cache misses which eliminates most of the performance bottleneck caused by system memory accesses. With the introduction of L1 cache, producers dodged a technology bullet that could have greatly reduced the desirability and sales of new generation cmpus.

The reason for this level of detail is to establish the rationale for the adoption of L1 cache and it's inclusion in all subsequent generations<sup>37</sup> that followed the 386. So, what are the implications of this somewhat arcane description of evolving cmpu architecture? Logic transistors and memory transistors could hardly be more different. First, it is important to understand that logic transistors are smart and memory transistors are dumb. Logic is the core or active part of the cmpu that executes software instructions. Memory is passive and acts as a buffer between cmpu logic and slower system components. Prior to the 486, all transistor counts represented logic, simply because L1 caches had not been introduced. If transistors are used in a pooled model that spans a significant time period due to limited observations, then interpretation of the transistor characteristic takes on a different meaning for the 386 relative to the  $486^{38}$ .