System Level Optical Interconnect

#### Optical Fiber Computer Interconnect: The Simultaneous Multiprocessor Exchange (SOME)-Bus

Rhonda Kay Gaede

The University of Alabama in Huntsville Department of Electrical and Computer Engineering Huntsville, AL 35899

UAH

Optical Interconnects for High Performance Computing Workshop Oak Ridge, Tennessee

System Level Optical Interconnect

November 8 & 9, 1999

Electrical and Computer Engineering

• Computer Engineering

#### **Computer Networks**

- Carries information between processors

- Influences computer system performance

- Many Variations

- Shared Bus

- Point-to-Point

#### Shared Bus

- Single set of wire(s) used for data exchange, e.g. Ethernet segment

- Advantages

- Low wiring costs

- Direct connection between processors

- Disadvantages

- Limited communication bandwidth

- Arbitration overhead

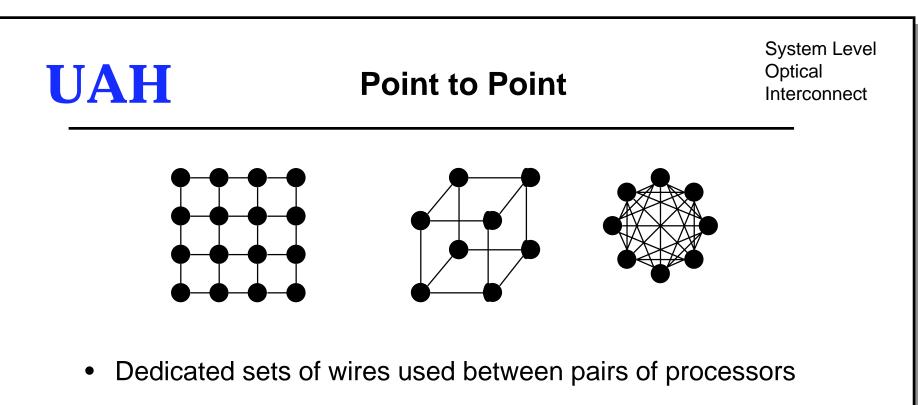

- Advantages

- Greater aggregate bandwidth

- Limited number of taps on channel

- Disadvantages

- More wiring

- Processors not directly connected

#### **Electronics Technology**

- Advantages

- Dense digital VLSI circuitry

- Inexpensive fabrication

- Disadvantages

- Low fan-out of signals

- Low bandwidth per channel

- Point-to-point communication channels

#### **Optics Technology**

- Advantages

- High fan-out of signals

- High bandwidth per channel

- Multi-cast communication channels

- Disadvantages

- Single point insertion

- Weak computing facilities

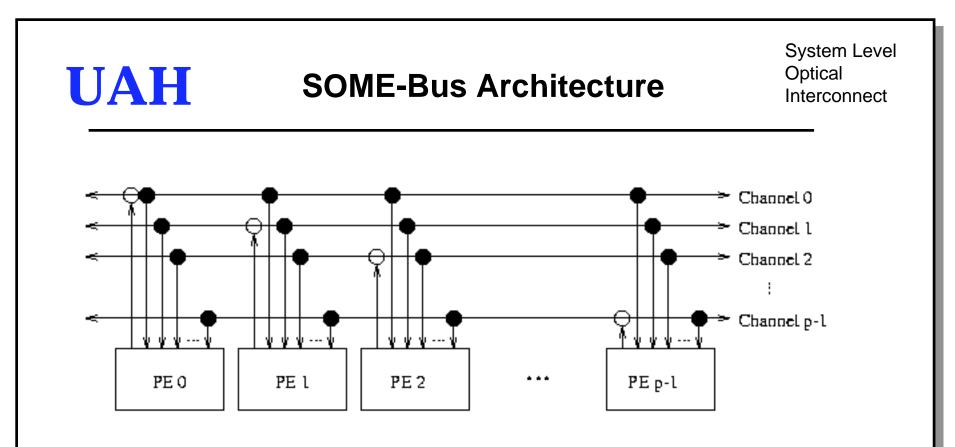

- Exploits strengths of electronics and optics technologies

- One dedicated unidirectional channel per processor

- Each processor observes all channels

- Performance not limited by communication medium (fiber)

| UAH                                 | Network Characteristics |                        |                        | System Level<br>Optical<br>Interconnect |

|-------------------------------------|-------------------------|------------------------|------------------------|-----------------------------------------|

| N processors                        | Diameter                | Channels               | Trans-<br>mitters      | Re-<br>ceivers                          |

| SOME Bus                            | 1                       | Ν                      | Ν                      | (N) <sup>2</sup>                        |

| Shared Bus                          | 1                       | 1                      | Ν                      | N                                       |

| Mesh                                | (N) <sup>0.5</sup>      | 4N                     | 4N                     | 4N                                      |

| Hypercube                           | Log <sub>2</sub> (N)    | N Log <sub>2</sub> (N) | N Log <sub>2</sub> (N) | N Log <sub>2</sub> (N)                  |

| Fully connected                     | 1                       | N(N-1)                 | N(N-1)                 | N(N-1)                                  |

|                                     |                         |                        |                        |                                         |

| Electrical and Computer Engineering |                         |                        |                        |                                         |

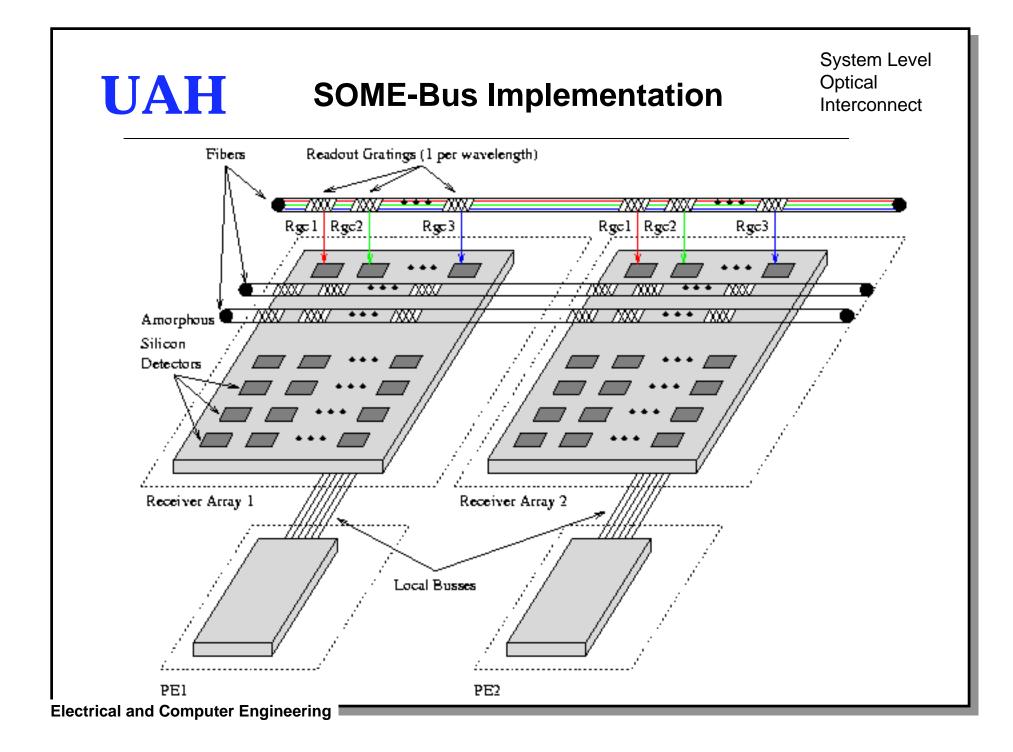

#### **Optics Implementation**

- Ribbon of multiple optical fibers

- Input coupler

- One per fiber

- Multiple wavelengths of light

- Multiple processor channels on single fiber

- Output coupler

- Multiple output couplers per fiber

- Bragg grating in fiber

- Wavelength specific

- Very small output per grating (~1%)

- Aligned with optical detectors

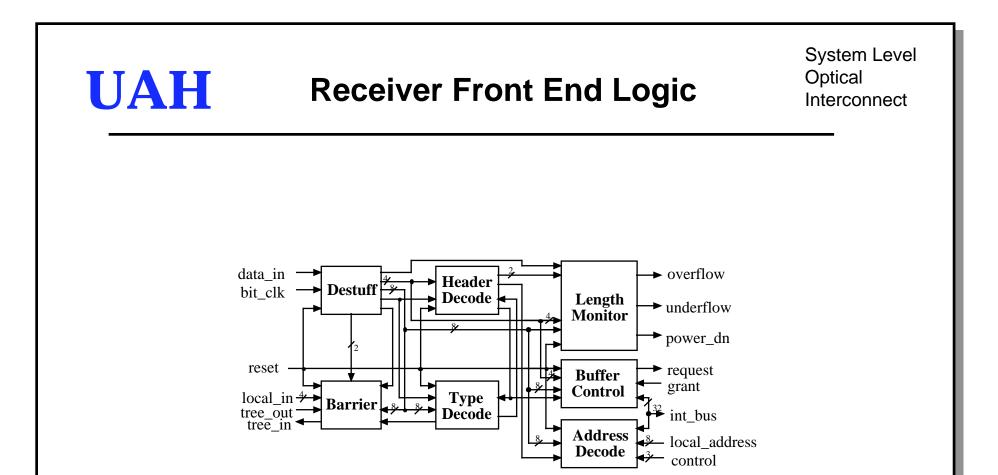

#### **Electronics Interface**

- Integrated Circuit (IC)

- Array of receivers

- Interface to Processor bus

- 128 1024 byte buffers and associated logic fit in a die size of 1.6 cm x .8 cm

- Receiver Functions

- Convert optical detector's analog signal into digital signal

- Filters out uninteresting bus traffic

- Buffer data until processor bus available

#### **Programming Support**

- Communication models

- Shared memory

- Message passing

- Simplified model for programming

- Direct connections between processors

- No interference on channel from other processors

- High-speed broadcast

- Fast barrier synchronization mechanism

### **UAH** Factors Affecting Performance

- Bandwidth is an important concern, but not the only one

- Latency is critical in many computer operations such as

- Cache coherency messages

- Shared memory data exchanges

- Handshaking and synchronization signals

- Network flow control/resource allocation

#### **Future Work**

- Form gratings in fibers and characterize footprint and selectivity

- Examine issues of inter-mixed analog and digital circuitry

- Build silicon v-groove devices to hold fibers for alignment with photodetectors

- Characterize performance for realistic program loads using simulations.

- Investigate whether diffractive optic elements are required, build if necessary

- Build and characterize 32 channel prototype

#### Conclusions

- Bandwidth scales with the number of processors

- Network diameter = 1

- Supports shared memory, message passing and synchronization

- As technology matures, the system bandwidth will increase