### Impact of Technology Scaling on Low Noise Front End Circuits

Paul O'Connor, Brookhaven National Laboratory

Snowmass 2001

July 9 2001

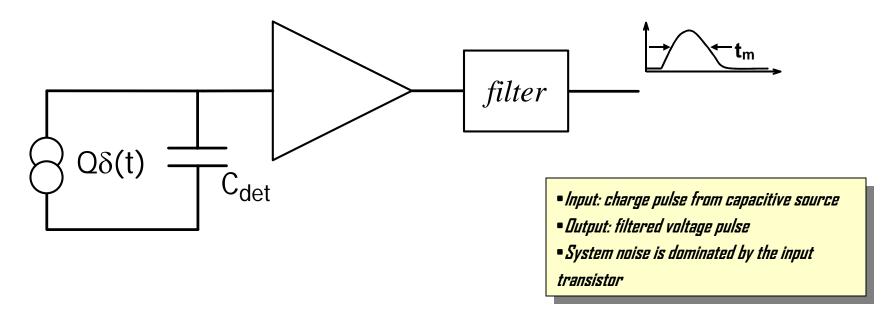

## Charge preamplifier/shaper as detector front end

- Low noise is critical for many experiments

- Ageing of gas detectors

- Fast, inefficient scintillators

- Thin semiconductors for tracking

- Position determination by interpolation

- Particle ID by dE/dx

#### **Outline**

- Low noise analog design in monolithic CMOS

- Preamplifier design

- Shaping amplifier

- Circuit examples

- MOS Scaling and CSA design

- Noise mechanisms in scaled devices

- Optimum capacitive match to detector

- Noise, dynamic range, and power vs. scaling length

- Interconnect issues

- Detector-to-preamplifier

- Front end-to-ADC

## Low Noise Analog Design

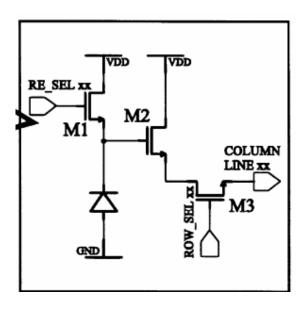

## MOS Charge Amplifier Design

- Key parameters:

- $-C_{det}$  ,  $I_{det}$  ,  $Q_{max}$

- Rate, P<sub>diss</sub>

- $f_T, K_F, I_{in}$

- Key design decisions

- $C_{gs}/C_{det}$

- Reset system

- Weighting function

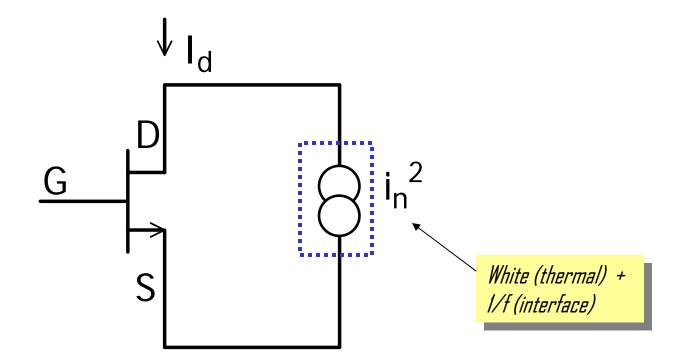

#### **MOSFET Channel Thermal Noise**

Drain current and its fluctuation:

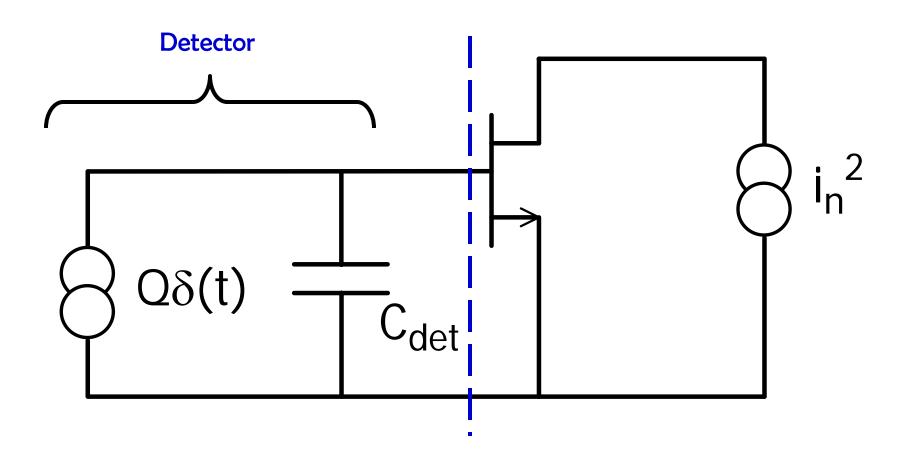

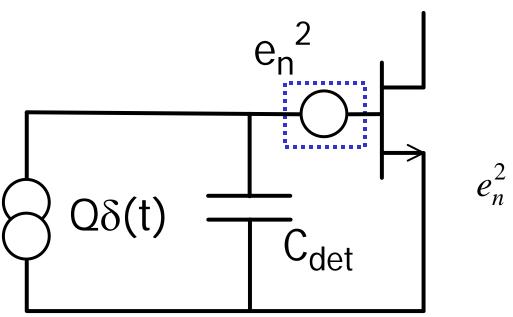

#### **MOSFET** connected to detector

### Transform noise to input

$$e_n^2 = \frac{4kT\gamma}{g_m} + \frac{K_F}{C_{gs}f}$$

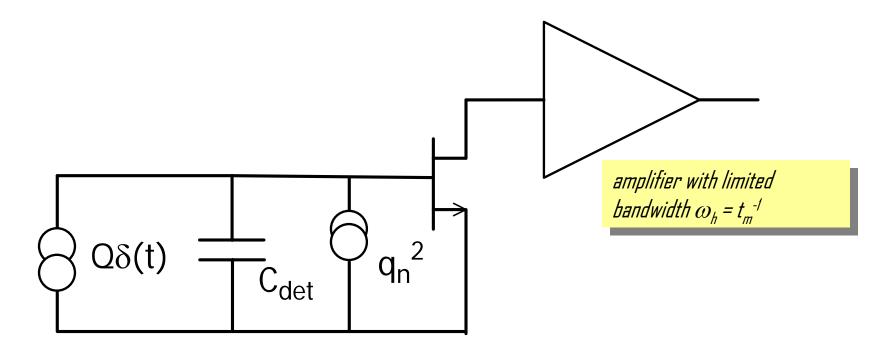

#### Equivalent input noise charge

$$ENC^{2} = \left(\frac{4kT}{g_{m}t_{m}} + \frac{K_{F}}{C_{gs}}\right)C_{in}^{2}$$

#### Device sizing for minimum ENC

• Increasing MOS size decreases noise sources while increasing transistor contribution to  $C_{in}$

$$ENC^{2} = \left(\frac{4kT}{g_{m} \cdot t_{m}} + \frac{K_{F}}{C_{gs}}\right) C_{in}^{2}$$

$$C_{in} = C_{gs} + C_{det}$$

=> optimum transistor size for series white and 1/f noise:

$$C_{gs,sw,opt} = \alpha_{sw} C_{det}$$

$$C_{gs,1/f,opt} = \alpha_{1/f} C_{det}$$

### **Optimized ENC**

• Transistor cutoff frequency  $g_m = C_{gs} \cdot \omega_T = C_{gs} / \tau_{el}$

$$ENC_{sw,opt} \approx \sqrt{kTC_{det}} \sqrt{\frac{\tau_{el}}{t_m}}$$

$$ENC_{1/f,opt} \approx \sqrt{K_F C_{det}}$$

- Key ingredients for low ENC:

- low C<sub>det</sub>

- long t<sub>m</sub>

- short  $\tau_{el}$

- Low  $K_F$

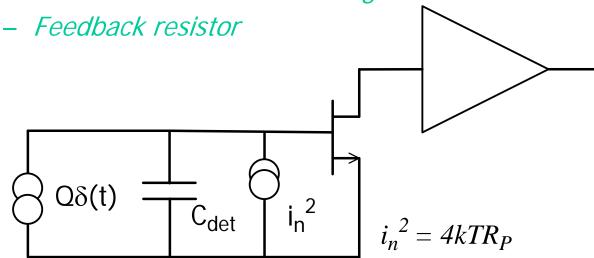

#### Parallel noise

- From any noise current source connected to input:

- Detector biasing resistor

$$ENC_{par} = \sqrt{\frac{4kTt_m}{R_p}}$$

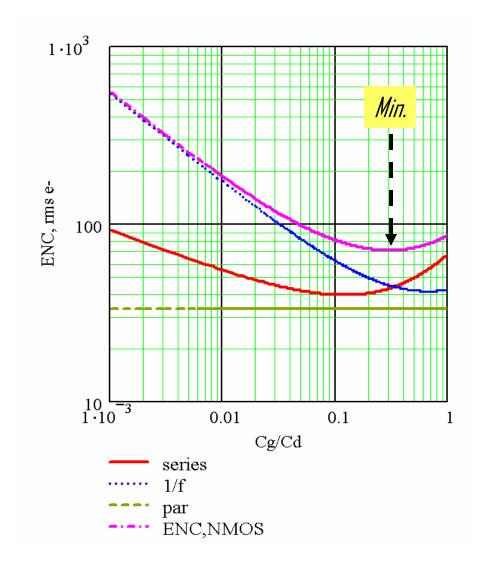

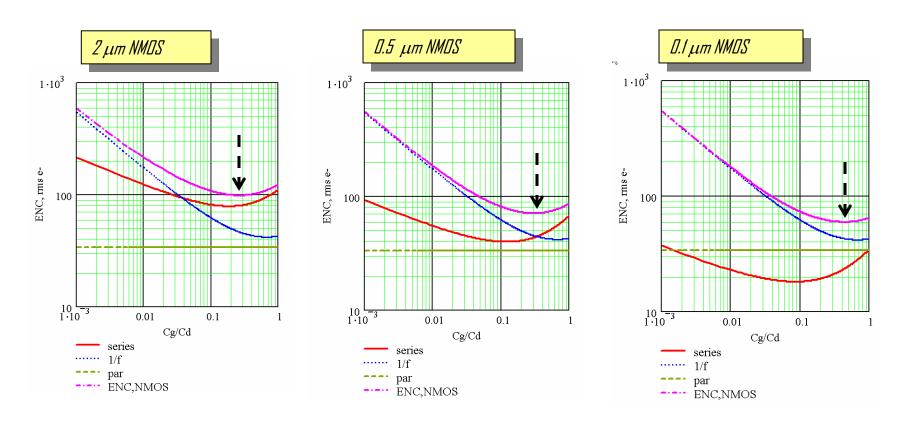

## Capacitive matching – composite noise

- $C_{det} = 3 \text{ pF}$

- $t_m = 1 \, \mu s$

- $P_{diss} = 1 \text{ mW}$

- $I_{leak} = 100 \text{ pA}$

- Technology: 0.35 μm NMOS

## **Basic Charge Amplifier**

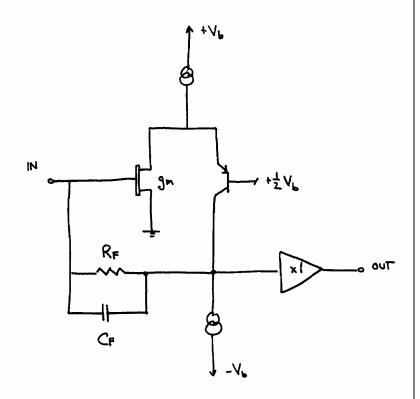

#### Configuration based on discrete/hybrid design

#### **CMOS** implementation

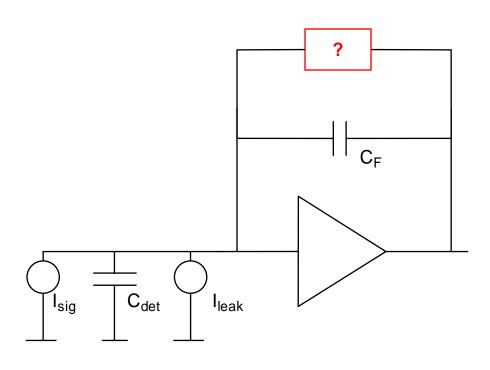

# Preamp Reset – Requirements

- all charge preamplifiers need DC feedback element to discharge C<sub>F</sub>

- usually, a resistor in the  $M\Omega$   $G\Omega$  range is used

- monolithic processes don't have high value resistors

- we need a circuit that behaves like a high resistor and is also

- insensitive to process, temperature, and supply variation

- low capacitance

- lowest possible noise

- linear

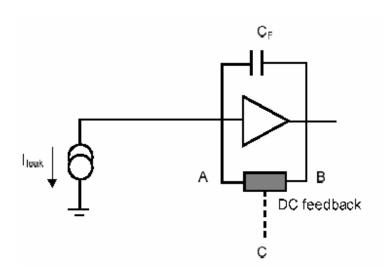

# Preamp Reset – Configurations

| Feedback<br>type                        | Circuit                                 | R <sub>eff</sub> (I <sub>leak</sub><br>=0) | Advantages/<br>Disadvantages                                                        |

|-----------------------------------------|-----------------------------------------|--------------------------------------------|-------------------------------------------------------------------------------------|

| Physical resistor                       | а <b>-{W}-</b> В                        | R                                          | + simple - hard to make large R - parasitic C - doesn't adjust to I <sub>leak</sub> |

| MOS<br>switch                           | A B C(pulse)                            | $\frac{1}{C_F \cdot f_{reset}}$            | + simple - dead time - switch noise                                                 |

| Triode<br>MOS                           | A B C Bias                              | $\frac{1}{\beta \cdot (V_{gs} - V_T)}$     | + compact<br>+ adjusts to I <sub>leak</sub><br>- nonlinear                          |

| Feedback g <sub>m</sub>                 | $A \bigoplus_{g_m}^B C_{\text{(Vref)}}$ | $\frac{1}{g_m}$                            | + adjusts to I <sub>leak</sub> - complex - excess noise - nonlinear                 |

| Attenuat-<br>ing cur-<br>rent<br>mirror | A <sub>I</sub> <<1 B                    | $\frac{R}{A_i}$                            | + aux. output for PZC - doesn't adjust to $I_{leak}$                                |

#### Nonlinear Pole-zero Compensation

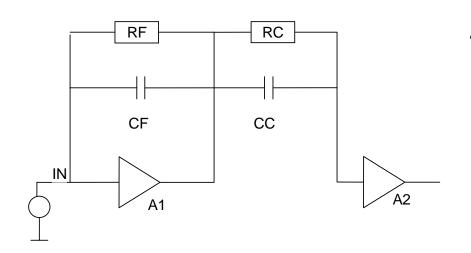

#### Classical

- $-RF \cdot CF = RC \cdot CC$

- Zero created by RC,CC cancels pole formed by RF, CF

G. Gramegna, P. O'Connor, P. Rehak, S. Hart, "CMOS preamplifier for low-capacitance detectors", NIM-A 390, May 1997, 241 – 250.

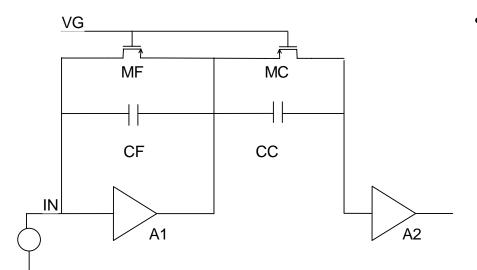

#### IC Version

- $-CC = N \cdot CF$

- $(W/L)_{MC} = N \cdot (W/L)_{MF}$

- Zero created by MC, CC

cancels pole formed by MF, CF

- Rely on good matching characteristics of CMOS FETs and capacitors

#### **Integrated Shaping Amplifiers**

- Limits the bandwidth for noise

- Gives controlled pulse shape appropriate for rate

- Control baseline fluctuations

- Bring charge-to-voltage gain to its final value

- By its saturation characteristics, sets upper limit on Q<sub>in</sub>

- Feedback circuits give the most stable and precise shaping

- At the expense of power dissipation

- Poor tolerance of passives limits accuracy of the poles and zeros

- High-order shapers give the lowest noise for a given pulse width

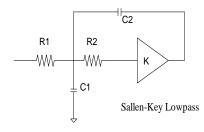

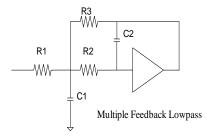

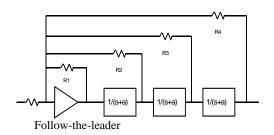

#### Filter topologies

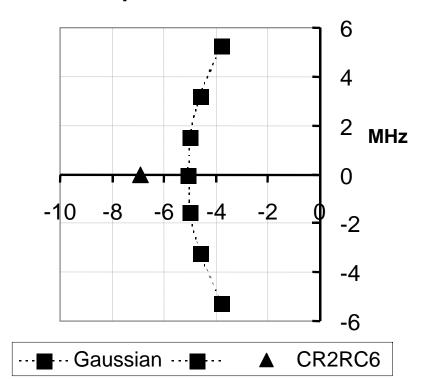

## Complex pole approximation to Gaussian pulse

#### **Shaper Pole Positions**

**Ohkawa synthesis method** (Ohkawa, NIM 138 (1976) 85-92, "Direct Syntheses of the Gaussian Filter for Nuclear Pulse Amplifiers")

For given filter order, gives closest approx. to a true Gaussian

More symmetrical than CR-RC<sup>n</sup> filter of same order for same peaking time

Noise weighting functions:

$$I_{L.comolex}/I_{L.CR-RC} = 1.18$$

series

$$I_{2,complex}/I_{2,CR-RC} = 0.81$$

parallel

#### Complex shapers: advantages

## Examples

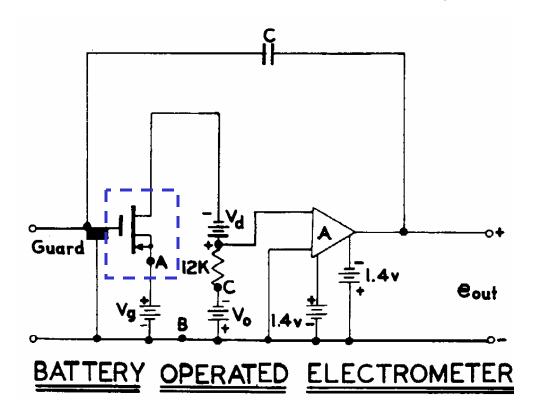

## Charge Amplifier based on Silicon MOSFET (1967)

V. Negro et al., "A Guarded Insulated Gate Field Effect Electrometer", IEEE Trnas. Nucl. Sci. Feb. 1967, 135 – 142 J.B. McCaslin, "A Metal-Oxide-Semiconductor Electrometer Ionization Chamber", UCRL-11405 (1964)

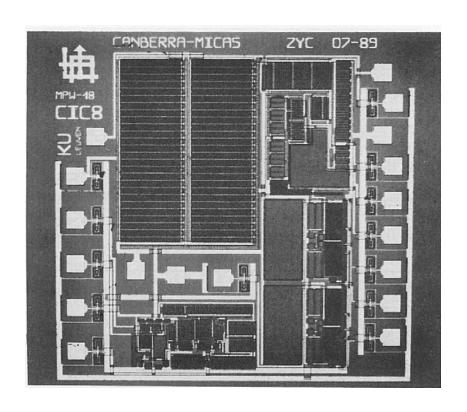

### Spectroscopy amplifier (1989)

Technology 3.0 µm CMOS

Power Supply +/- 5V

Chip size 2.5 x 2.5 mm

Channels 1

$C_{det}$  300 - 1000 pF

Reset external resistor

Shaping  $CR-RC^4$ , 1.6 µs  $3800 + 4.1 e^{-}/pF$

Power dissipation 96 mW

Z. Chang, W. Sansen, *Low-Noise Wide-Band Amplifiers in Bipolar and CMOS Technologies*, Kluwer 1991 Ch. 5

# Preamp-shaper for cathode strip chamber

- Detector: cathode strips of 0.5m MWPC with 50 pF C<sub>DET</sub>

- Charge interpolation to 1/100 of the strip pitch

- Fast (70 ns), 7<sup>th</sup> order bipolar shaping for charged particle tracking in high rate environment

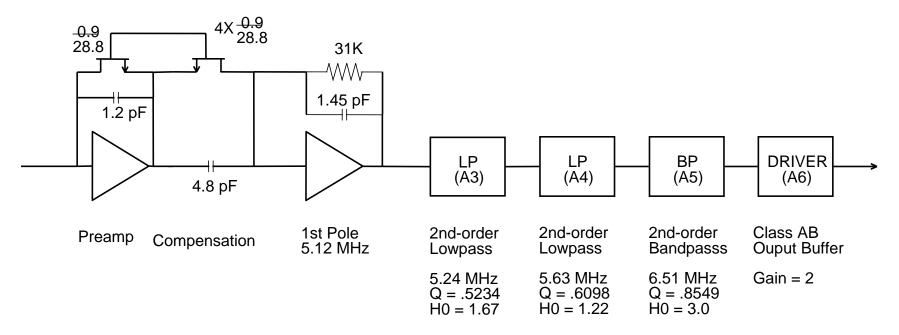

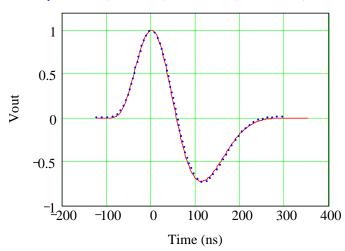

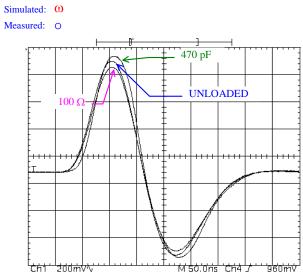

#### Preamp-shaper for cathode strip chamber

Pulse Shape simulated (solid red line) and measured (blue dotted line)

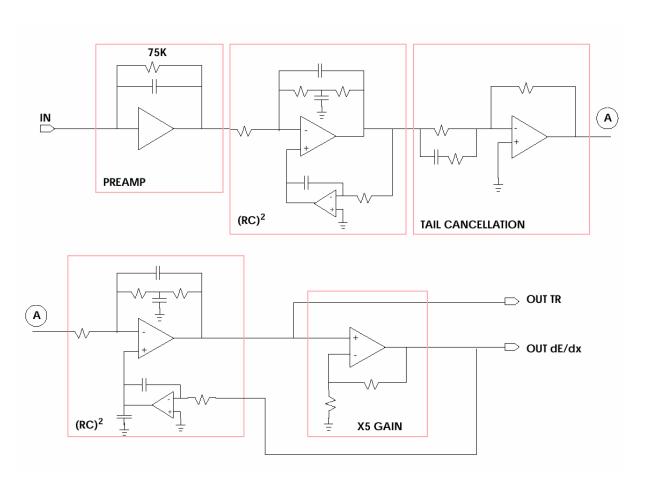

# Time Expansion Chamber & Transition Radiation Detector Preamp/Shaper

- 1m MWPC with

20 pF C<sub>DFT</sub>

- Fast (70 ns)

shaping for

charged particle

tracking

- Dual gain outputs for measurement of dE/dx and Transition Radiation

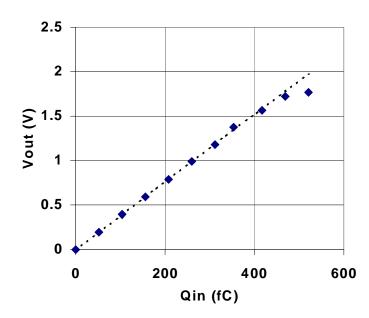

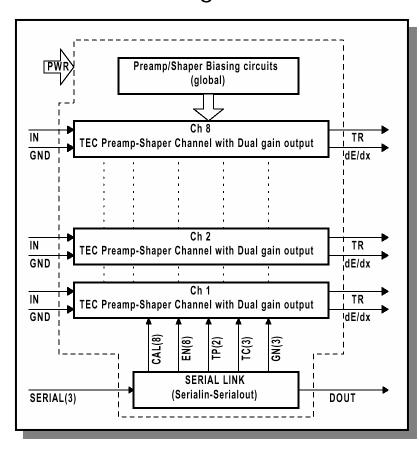

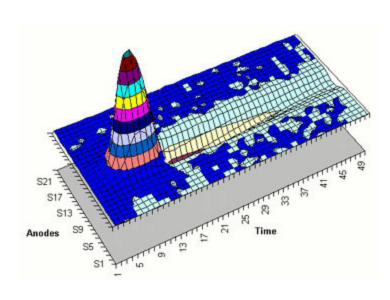

#### TEC-TRD Preamp/Shaper

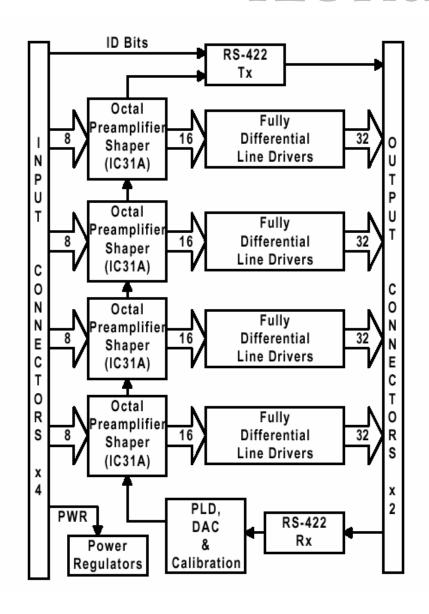

#### **Block Diagram**

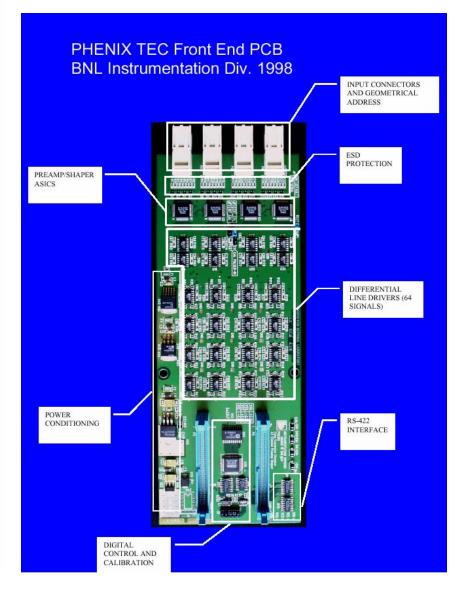

A. Kandasamy, E. O'Brien, P. O'Connor, W. VonAchen, "A monolithic preamplifier-shaper for measurement of energy loss and transition radiation" IEEE Trans. Nucl. Sci. 46(3), June 1999, 150-155

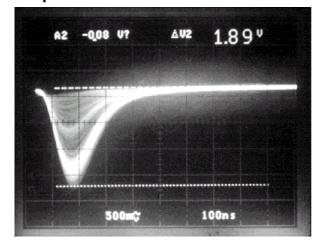

Die Layout

X-ray Response

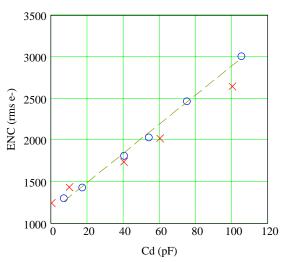

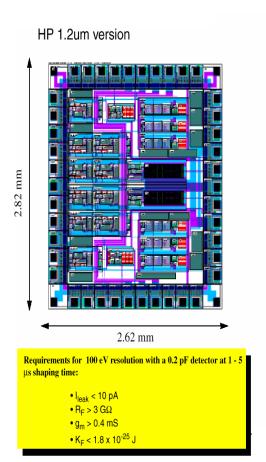

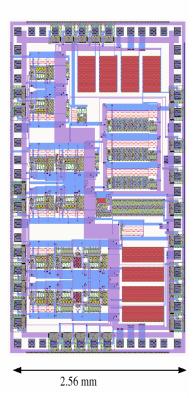

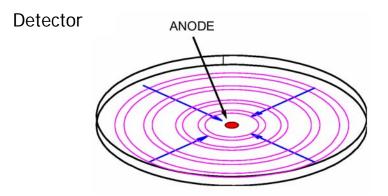

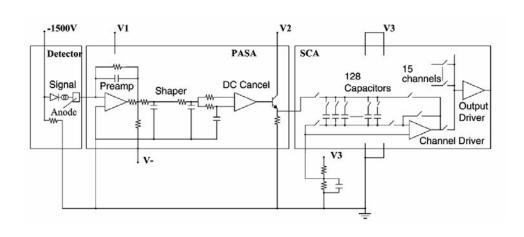

#### Drift Detector Preamplifier

AMS 1.2um version

- Used with ultra-low capacitance silicon drift detector, C<sub>det</sub> < 0.3 pF</li>

- Preamp only, used with external shaper

- Purpose: explore lowest noise possible with CMOS

- Reset system: MOS transistor with special bias circuit to achieve stable,  $> 100 \text{ G}\Omega$  equivalent resistance

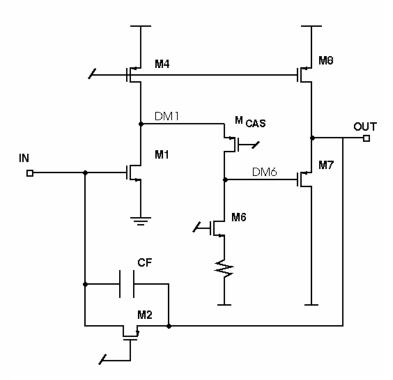

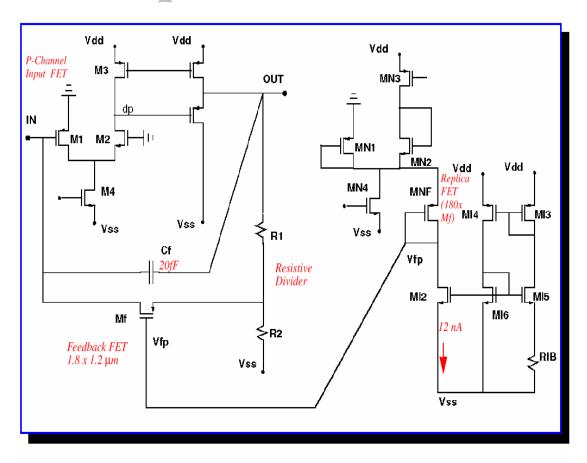

## Drift detector preamplifier – simplified schematic

Preamplifier

Bias Circuit

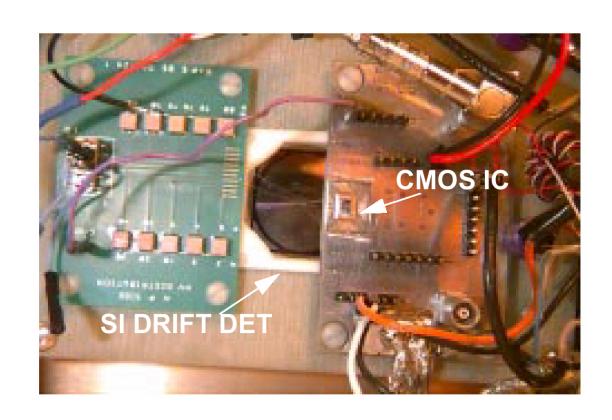

# Drift Detector & CMOS Preamplifier

#### Drift detector preamplifier – results

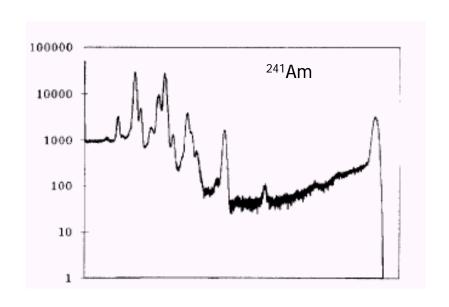

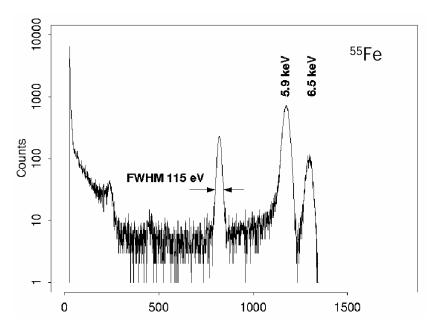

- Spectra of  $^{241}$ Am and  $^{55}$ Fe taken with 5mm  $\Phi$  Si drift detector and CMOS X-ray preamplifier. Detector and circuit cooled to -75 C.

- External 2.4 μs shaping.

- ENC =  $13 e^{-1}$  rms.

- Noise without detector: 9 e-

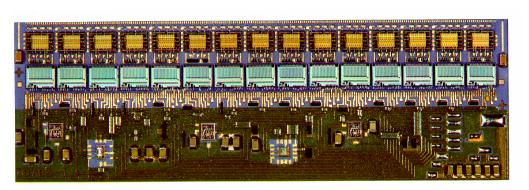

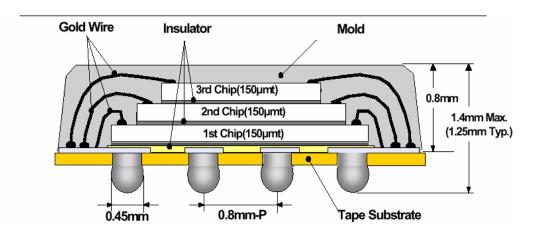

## SVT 240-channel Multi-Chip Module

D. Lynn et al., "A 240 channel thick film multi-chip module for readout of silicon drift detectors", NIM A439 (2000), 418 - 426

#### BNL Preamp/Shaper ICs, 1995 - 2001

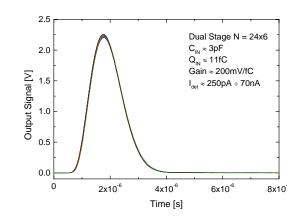

| PROJECT          | Hi-res.            | RHIC - PHENIX  | RHIC - STAR    | LHC - ATLAS         | Industry        | NSLS - HIRAX    | Units           |

|------------------|--------------------|----------------|----------------|---------------------|-----------------|-----------------|-----------------|

|                  | Spectroscopy       |                |                |                     | Partnership     |                 |                 |

| DETECTOR         | Si drift           | Time Expansion | Silicon Vertex | Cathode Strip       | CdZnTe gamma    | Si Pixel        |                 |

|                  |                    | Chamber        | Tracker        | Chamber             | ray detector    |                 |                 |

| Function         | Preamp             | Preamp/Shaper  | Preamp/Shaper  | Preamp/Shaper       | Preamp/Shaper   | Preamp/Shaper/  |                 |

|                  |                    |                |                |                     |                 | Counter         |                 |

| C <sub>DET</sub> | 0.3                | 30             | 3              | 50                  | 3               | 1.5             | pF              |

| Peaking          | 2400               | 70             | 50             | 70                  | 600:1200:2000:4 | 500:1000:2000:4 | ns              |

| Time             |                    |                |                |                     | 000             | 000             |                 |

| Gain             | 10                 | 2.4:12 - 10/25 | 40:70:90       | 4                   | 30:50:100:200   | 750:1500        | mV/fC           |

| Power            | 10                 | 30             | 3.8            | 33                  | 18              | 7               | mW/channel      |

| ENC              | 10                 | 1250           | 400            | 2000                | 100             | 24              | rms electrons   |

| Dynamic          | 1250               | 4600           | 700            | 1900                | 5600            |                 |                 |

| Range            |                    |                |                |                     |                 |                 |                 |

| Technology       | CMOS 1.2 um        | CMOS 1.2 um    | Bipolar 4 GHz  | CMOS 0.5 um         | CMOS 0.5 um     | CMOS 0.35 um    |                 |

| Input            | PMOS               | NMOS           | NPN            | NMOS                | NMOS            | PMOS            |                 |

| Transistor       | 150/1.2 um         | 4200/1.2 um    | 10 uA          | 5000/0.6 um         | 200/0.6 um      | 400/0.4 um      |                 |

| Reset            | Compensated        | Polysilicon,   | Nwell,         | Compensated         | Compensated     | Compensated     |                 |

| Scheme           | PMOS, $> 1G\Omega$ | 75 kΩ          | 250 kΩ         | NMOS, 30 M $\Omega$ | PMOS            | NMOS            |                 |

| No.              | 6                  | 8              | 16             | 24                  | 16              | 32              |                 |

| Channels         |                    |                |                |                     |                 |                 |                 |

| Die Size         | 7.3                | 15             | 8              | 20                  | 19              | 16              | mm <sup>2</sup> |

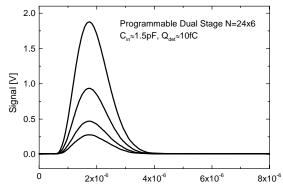

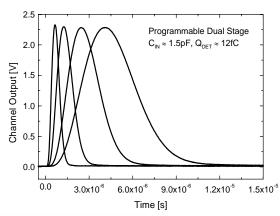

#### Practical amplifier considerations

- High order filters

- Programmable pulse parameters

- Circuit robustness:

- Self-biasing

- Low-swing, differential I/O

- Circuits tolerant to variations in

- Temperature

- Process

- Power supply

- DC leakage current

- Loading

#### Pulse vs. Temperature

#### **Gain variation**

#### Pulse vs. I<sub>leak</sub>

#### **Peaking time variation**

| Baseline | < 0.3mV/nA        | <30 μV/V | 75 μV/°C    | < 8 mV         | -        | Zout ~ 150 \(\Omega\) |

|----------|-------------------|----------|-------------|----------------|----------|-----------------------|

|          |                   |          |             |                |          | limit                 |

| Gain     | < 0.1%/nA         | <.001%/V | -0.04%/°C   | < 0.1%         | <0.1%/pF | No slew-rate          |

|          | l <sub>leak</sub> | Supply   | Temperature | Rate (to 5/tp) | Cin      | Zload                 |

## MOS Scaling and Charge Amplifier Design

### Scaling issues

- Fundamental device noise mechanisms

- Hot electron effects

- New process steps effect on 1/f noise

- Gate tunnelling current

- Change of the current-voltage characteristics

- Increase of weak inversion current

- Mobility decrease

- Velocity saturation

- Drain conductance (device intrinsic DC gain)

- Power supply scaling

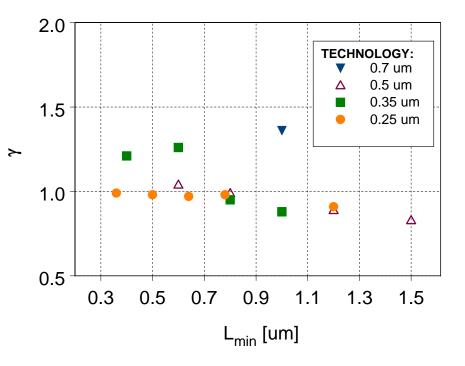

#### Series white noise

- Parameter  $\gamma = gm * Rn$

- Some models predict γ >> 1

for short channel devices

- At moderate inversion and low > VDS, γ remains in the range

0.8 < γ < 1.4</li>

- Shallow junctions increase S/D series resistance => noise

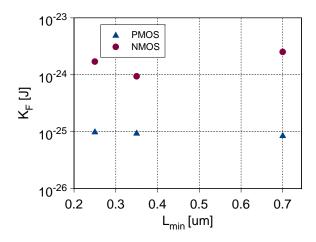

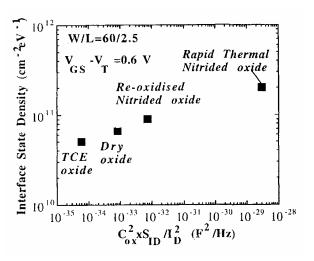

### 1/f noise in submicron CMOS

- Processes with n+/p+ poly gates and retrograde wells create surfacechannel PMOS – PMOS 1/f noise to become more like NMOS?

- Shallow junctions required for scaled processes limit the thermal budget – hence gate process will have reduced post-oxidation anneal and higher trap density, higher 1/f

- For ultrathin gates new dielectrics with higher trap densities will be used (nitrided, halogenated, H2 annealed)

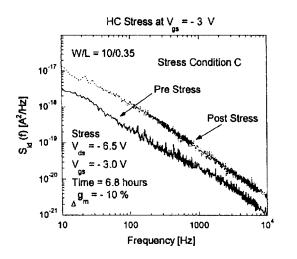

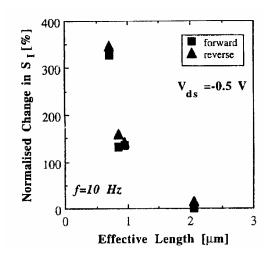

### 1/f noise and hot carrier stress

- Hot carrier stress generates new oxide/interface traps.

- 1/f noise more sensitive than change in static parameters:

- $\Delta g_m 10\%$  $- \Delta (1/f) + 400\%$

- Worse for shorter channel lengths

- A device engineered for "acceptable" degradation of  $V_{th}$  and  $g_m$  may show unacceptable increase in 1/f noise over the same period.

- The operating point of the device will determine the stability of the long-term 1/f noise

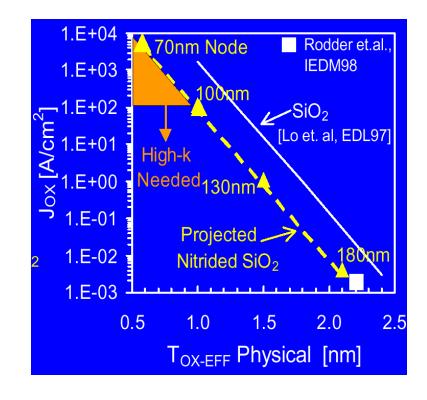

## Gate tunneling current

- Gate current expected to increase

100 200 x per generation below

0.18 μm

- $J_{ox} \sim 100 \text{ A/cm}^2 \text{ projected for } L_{min} = 0.1 \text{ } \mu\text{m} \text{ generation with nitrided } SiO_2$

- Considered tolerable for digital circuits (total gate area per chip ~ 0.1 cm²)

- Typical CSA input FET would have  $I_G$  ~ 1 10  $\mu$ A; ENCp ~ 2000 7000 rms e- at 1  $\mu$ sec

SiO<sub>2</sub> gate leakage current (Lo et al., Electron Dev. Letters 1997)

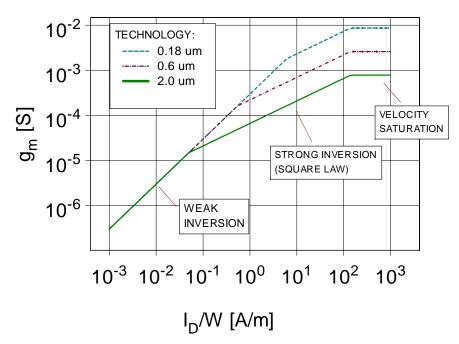

# Departure from square-law characteristics

- Submicron devices are less often operated in strong inversion, squarelaw region.

- Influences behavior of series white thermal noise

- Square-law devices have minimum series noise when  $C_{qs} = C_{det}/3$

- For other regions of operation, minimum noise can be for larger or smaller values of  $\mathcal{C}_{gs}$

## Generalized capacitive matching condition

- Drain current = constant

- Ratio of  $C_{gs}$  to  $C_{det}$  determined by  $C_{det}/I_{d}$ :

| C <sub>det</sub> / I <sub>D</sub><br>Ratio                                        | Region of operation                | Optimum capacitive match                           |  |  |

|-----------------------------------------------------------------------------------|------------------------------------|----------------------------------------------------|--|--|

| $\frac{C_{\text{det}}}{I_D} < \frac{6\mu}{v_{sat}^2}$                             | Velocity<br>saturated              | $C_{gs} = C_{det}$                                 |  |  |

| $\frac{6L^2}{\mu(nkT/q)^2} < \frac{C_{\text{det}}}{I_D} < \frac{6\mu}{v_{sat}^2}$ | Strong-<br>inversion<br>square-law | $C_{gs} = C_{det} / 3$                             |  |  |

| $\frac{C_{\text{det}}}{I_D} > \frac{6L^2}{\mu (nkT/q)^2}$                         | Weak<br>inversion<br>boundary      | $C_{gs} = \frac{2L^2I_D}{C_{\text{det}}(nkT/q)^2}$ |  |  |

P. O'Connor, G. De Geronimo, "Prospects for Charge Sensitive Amplifiers in Scaled CMOS", NIM-A accepted for publication

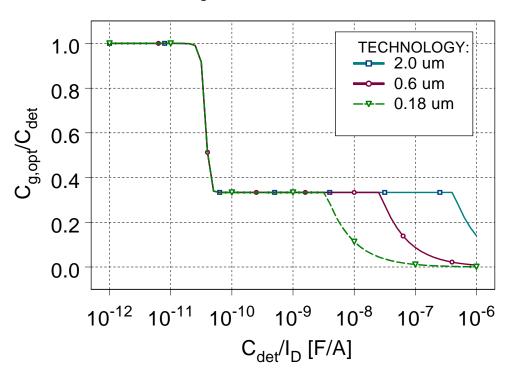

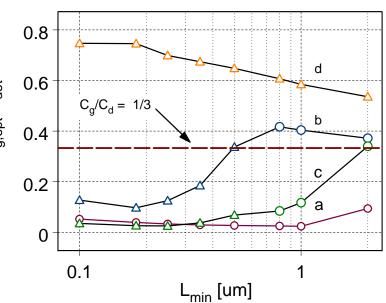

# Capacitive match vs. scaling – mixed white, 1/f and parallel noise

•  $C_{det} = 3 \text{ pF}$ ,  $t_m = 1 \text{ } \mu\text{s}$ ,  $P_{diss} = 1 \text{ mW}$ ,  $I_{leak} = 100 \text{ pA}$

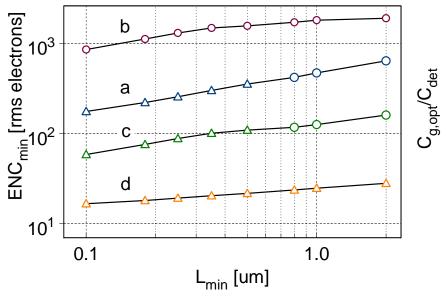

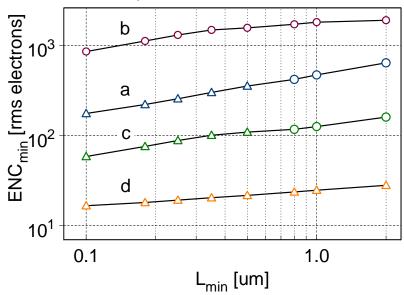

## Noise vs. scaling for mixed white, 1/f, and parallel noise

4 detector scenarios for scaling study

| System   | $\mathbf{C}_{_{det}}$ | <u>t</u> ,  | P    | I    | Detector        | Typical Application |

|----------|-----------------------|-------------|------|------|-----------------|---------------------|

| <u>a</u> | 30                    | 75          | 10   | .001 | Wire Chamber    | Tracking, Imaging   |

| <u>b</u> | 15                    | 25          | 0.2  | 10   | <u>Si</u> Strip | Tracking            |

| <u>c</u> | 0.3                   | 25          | 0.02 | 1    | Si Pixel        | Tracking            |

| <u>d</u> | 3                     | 2500 - 500* | 10   | 0.01 | Semiconductor   | Spectroscopy        |

| UNITS    | pF                    | ns          | mW   | nA   | -               | -                   |

Noise vs. scaling

Optimum gate width vs. scaling

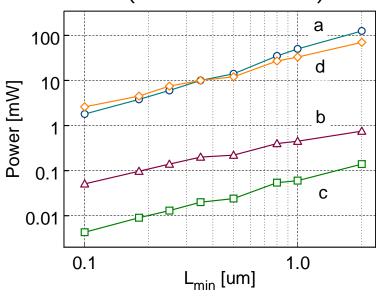

#### Noise and Power vs. Scaling

4 detector scenarios for scaling study

| System   | $\mathbf{C}_{_{\mathtt{det}}}$ | <u>t</u> ,  | P    | I    | Detector        | Typical Application |

|----------|--------------------------------|-------------|------|------|-----------------|---------------------|

| <u>a</u> | 30                             | 75          | 10   | .001 | Wire Chamber    | Tracking, Imaging   |

| <u>b</u> | 15                             | 25          | 0.2  | 10   | <u>Si</u> Strip | Tracking            |

| <u>c</u> | 0.3                            | 25          | 0.02 | 1    | Si Pixel        | Tracking            |

| <u>d</u> | 3                              | 2500 - 500* | 10   | 0.01 | Semiconductor   | Spectroscopy        |

| UNITS    | pF                             | ns          | mW   | nA   | -               | -                   |

Noise vs. scaling

(power held constant)

Power vs. scaling

(noise held constant)

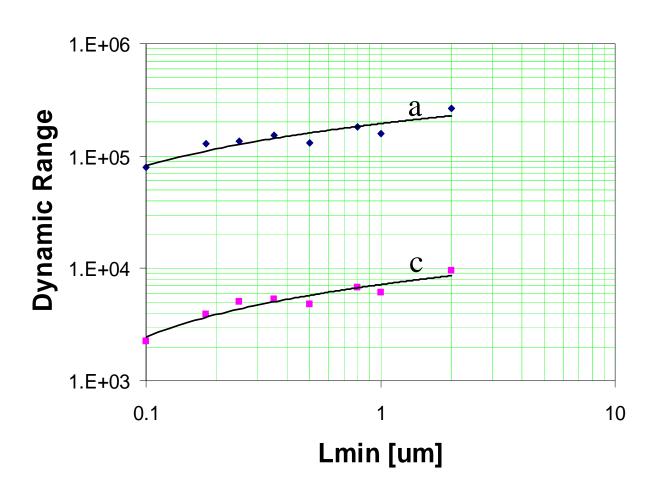

### Dynamic Range vs. scaling

### Interconnect

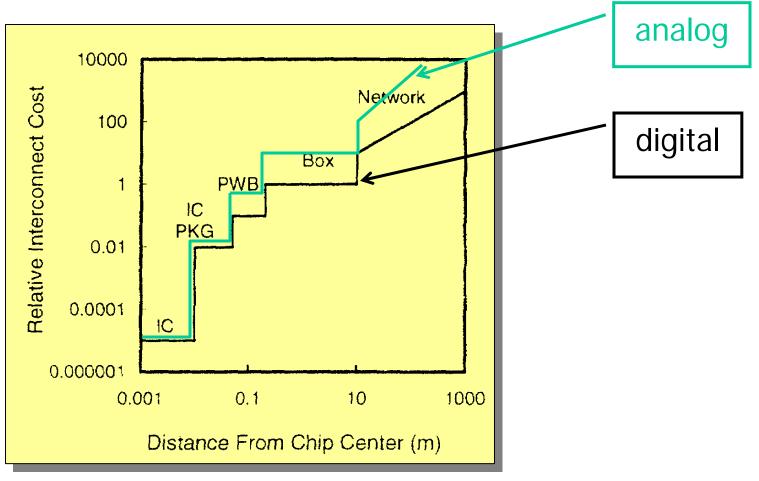

#### **Cost of Interconnect**

**ISSCC 2000**

# Interconnect issues in monolithic front ends

- Detector preamplifier

- Lowest possible capacitance

- Maintain small form factor

- Ease of assembly

- Front end ADC

- Efficient use of expensive "analog" interconnect

#### **TEC Front-End Card**

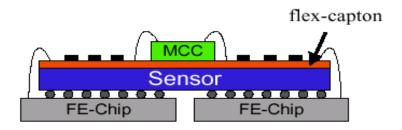

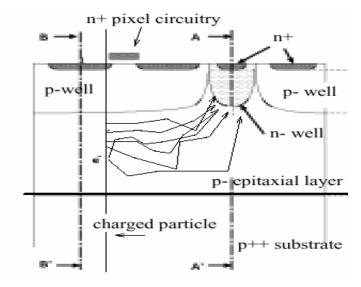

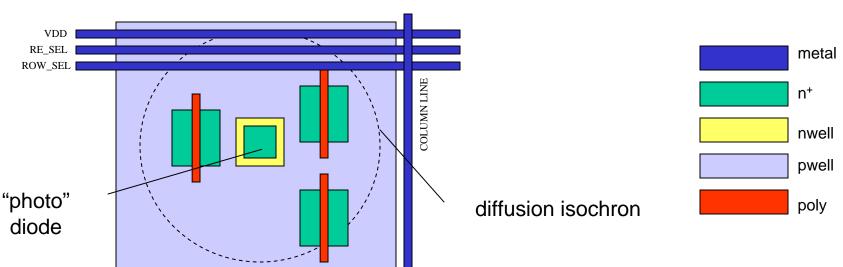

# Make the chip a part of the detector

### Make the detector part of the chip

# What goes between the preamp/shaper and the ADC?

- Experimental needs differ

- number of channels

- occupancy

- rate

- trigger

- Usually, its too expensive to put an ADC per channel

- Anyway the ADC would usually not be doing anything useful

- Occupancy < 100%, so no events most of the time in most channels

- What is the most efficient way to use the ADC(s)?

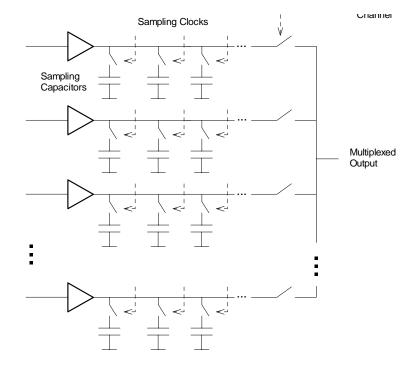

# Analog Sampling and Multiplexing

Inputs

Track-and-hold (triggered systems)

Track/Hold

Inputs

Select

Sampling Capacitor

Multiplexed Output

T

Analog memory (non-triggered)

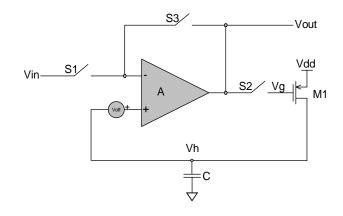

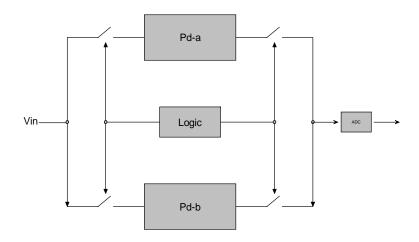

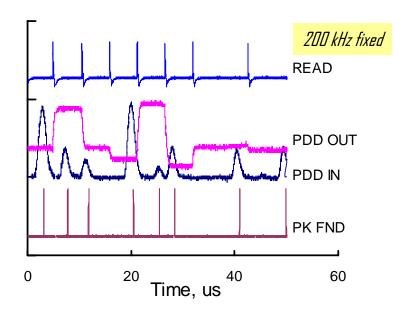

# New Peak Detector and Derandomizer

- Self-triggered

- Self-sparsifying

- New 2-phase configuration allows rail-to-rail operation, eliminates offsets

- absolute accuracy ~ 0.2%

- to within 300 mV of rails

- Two or more peak detectors in parallel can be used to derandomize events

- If a second pulse arrives before the readout of the first pulse in Pd-a, it is detected and stored on Pd-b.

## First experimental results

10

Accuracy of single PD

0.1

5

0

10

-10

-15

-15

-15

Peaking Time (µs)

PD/D response to random pulse train (241Am on CZT)

G. DeGeronimo, P. O'Connor, A. Kandasamy, "Analog Peak Detect and Hold Circuits Part 2: The Two-Phase Offset-Free and Derandomizing Configurations", NIM-A submitted for publication

#### **Conclusions**

- Today's CMOS technology can be used to make low noise front ends whose performance is nearly as good as the best discrete units

- In the future, increasing device cutoff frequency and gate oxide quality will help improve noise BUT

- Potentially serious increases in 1/f noise and gate current may accompany new process sequences

- Low supply voltage will hamper high dynamic range

- Increasing attention will have to be paid to interconnect at the technology, circuit, and architecture levels